AD574中英文翻译解析.docx

AD574中英文翻译解析.docx

- 文档编号:26381964

- 上传时间:2023-06-18

- 格式:DOCX

- 页数:17

- 大小:203.60KB

AD574中英文翻译解析.docx

《AD574中英文翻译解析.docx》由会员分享,可在线阅读,更多相关《AD574中英文翻译解析.docx(17页珍藏版)》请在冰豆网上搜索。

AD574中英文翻译解析

12位-AD574A转换器

【摘要】AD574是美国AnalogDevice公司生产的12位单片A/D转换器。

它采用逐次逼近型的A/D转换器,最大转换时间为25us,转换精度为0.05%,所以适合于高精度的快速转换采样系统。

芯片内部包含微处理器借口逻辑(有三态输出缓冲器),故可直接与各种类型的8位或者16位的微处理器连接,而无需附加逻辑接口电路,切能与CMOS及TTL电路兼容,在多种复杂环境下能正常工作。

关键词:

高精度逐次逼近型转换器

电路工作原理

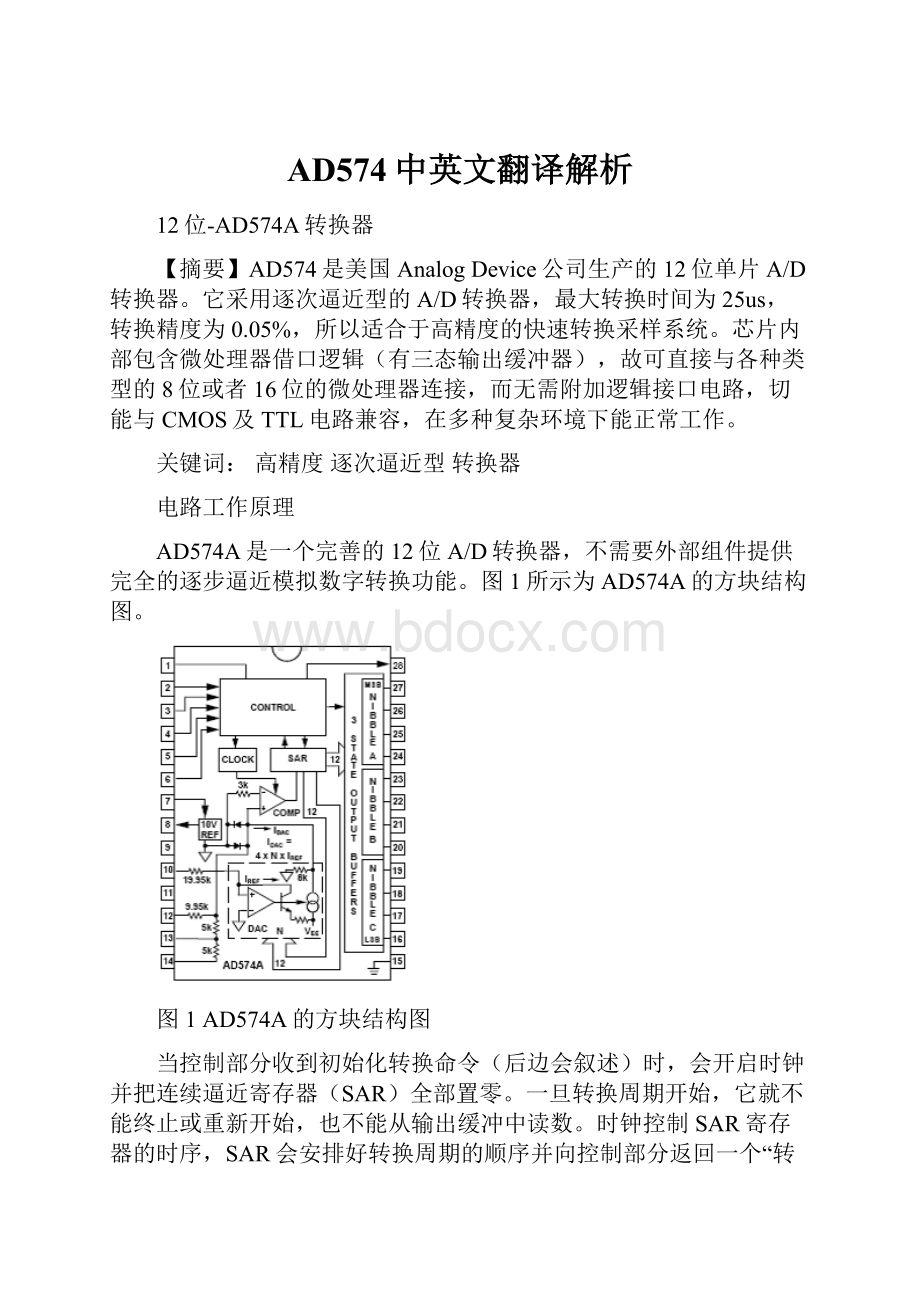

AD574A是一个完善的12位A/D转换器,不需要外部组件提供完全的逐步逼近模拟数字转换功能。

图1所示为AD574A的方块结构图。

图1AD574A的方块结构图

当控制部分收到初始化转换命令(后边会叙述)时,会开启时钟并把连续逼近寄存器(SAR)全部置零。

一旦转换周期开始,它就不能终止或重新开始,也不能从输出缓冲中读数。

时钟控制SAR寄存器的时序,SAR会安排好转换周期的顺序并向控制部分返回一个“转换结束”(end-of-convert)标志。

接着,控制部分停止时钟,把输出状态标志位置低,并允许控制函数,以便外部命令可以执行数据读取功能。

在转换周期期间,内部12位当前的产品DAC由SAR程序化从最高位(MSB)对最低有效位(LSB)通过5k(或10k)输入电阻器提供准确地平衡输入信号。

比较器确定位电流的连续增大是否造成了DAC当前总电流比输入电流增大或者减小;如果总电流较小,此位被留下;如果总电流较大,位被关闭。

在测试完所有位以后,SAR包含了准确表示输入信号在+1/2LSB之内的12位二进制编码。

温度补偿是外部提供给DAC基准电压并保证准确的转换的时间和温度的稳定性。

基准在10.000.2%伏之间平衡,当AD574A使用15伏电源时,除了按要求向参考输入电阻提供0.5mA,向双极偏移电阻提供1mA电流外,它可以给外部负载提供提供高至1.5mA的电流。

如果AD574A使用12伏电源,或者外部电流必须在全部温度范围内提供,那么我们推荐使用一个外部的缓冲放大器。

任何在AD574A参考手册上的外部负载都必须在转换过程中保持稳定。

要调整薄膜应用电容以匹配DAC(数模转换器)的实比例输出电流。

有两个5千欧的输入测量电阻允许10伏或20伏的区间。

10千欧的双极偏移电容接地用于单极操作,或连接到10伏参考电压上用于双极性操作。

AD574模拟输入电压

图2OP放大器与AD574连接

OP放大器的输出阻抗有一个开环值,在一个封闭回路中,这个值被回路增益(由增加的频率产生)等分。

放大器应该至少拥有500kHz的回路增益才能和AD574A一起使用。

要检查信号源的输出特性是否合适,就要在转换进行中使用示波镜监控AD574的输入端。

每12个干扰应该在1秒以内衰减。

关于取样—保持器的应用,我们推荐AD585型号。

我们推荐让AD711型号和AD544型号取样—保持器应在直流电下工作。

虽然AD574A的转换时间最高为35秒,但为了能够实现几个赫兹的频率的精确12位转换还是需要使用采样-保持放大器(SHA)的。

如果一个驱动AD574A的模拟输入信号电压在转换所需的计时周期中变化超过LSB的一半,那么输入端就需要一个SHA。

AD585是一种高线性的采样-保持放大器(SHA),它能够直接驱动AD574A的模拟输入端。

AD585的快速采集时间、低孔径和低孔径抖动都很好地使用于高速数据采集系统。

考虑到AD574A的转换时间为35秒,并且拥有10Vp-p的输入信号,这是能够实现1.5Hz精确转换时所能用的最高频率。

如图3所示,加上AD585后,最高频率增加到了26kHz。

AD585的低输出阻抗、快速连环反应和低损耗能够在变化的周期性负荷工况下维持12位准确性,使它适当用于高精确度转换。

许多其他SHAs达不到12位转换的准确性,并且可能因而减弱系统。

AD585被推荐应用于AD574A的采样与保持。

图3带采样保持器AD585的AD574A

AD574A电源的滤波、良好地校准和远离高频噪声是异常重要的.。

噪声补偿的使用会造成不稳定的输出信号。

除非特别要求滤掉输出端的电火花,交换式电源电路建议达到12比特的精确度。

注意:

一点点毫伏的噪声就代表着12比特ADC(电源)的巨大误差。

电路布局应该尝试定位AD574A,与之相连的相似物输入电路,并使其从逻辑电路上尽可能连接起来.因为这个原因,不推荐使用线路电路结构.应该选择好的印刷的电路体系.

逻辑控制

AD574A包含了芯片上逻辑,可以通过微处理器中通常存在的信号中提供开始转换和读取转换结果操作”如图6是AD574A的内部逻辑电路。

控制信号CE、CS,和R/C控制交换器的操作。

R/C的状态由CE和CS两个信号的加入来确定进行数据读取(R/C=1)或数据转换(R/C=0)。

记数器控制输入AO,12/8控制转换长度和数据格式。

AO线通常被连结到地址总线的最低有效位。

如果AO置低(电位)开始,按12位A/D进行转换。

当12/8=1时,12位数据线一次读出,主要用于16位微机系统;12/8=0时,可与8位机接口。

此引脚输入为高电平时,12位数据并行输出;当此引脚为低电平时,与引脚A0配合,把12位数据分两次输出。

12/8的引脚接DIGITALCOMMON输出8位数据12/8引脚接VLOGIC输出12位数据。

12/8的引脚不与TTL兼容的,必须和vlogic或者digital连接,在8位模式下,当Ao置高的时候,低4位加上尾随4个0有效。

在不需要内部3态缓冲器的情况下,该结构允许直接接口的8位数据流重叠。

在读取转换数据操作时不建议ao改变。

三态缓冲器不对称的允许与阻止时间可能造成内部总线冲突,对AD574A造成潜在危害.

图4

STS这个输出信号表明了转换器的状况。

STS值在转换开始时升高,在转换过程完成后降低回原样。

AD574A容易联接于多种微处理器和其他数字化系统。

下列AD574A控制信号的计时要求的讨论应该为系统设计者提供有用的对设备的操作了解。

图5

图5显示的是完整的AD574A运作时间矢量图表.坐标轴R/C在CE和CS被捕获之前都应较低;如果R/C显示较高,操作提示会立即发生,并可能引发系统争用.无论CE还是CS都能被用来转换.但是,我们推荐使用CE,因为它比CS有更少的系统延迟,并且能被较快地输入.在图表7,CE被用来转换.

一旦转换开始STS置成高位,直到转换循环完成,转换开始命令将被忽略。

直到转换周期是完全的。

在转换期间,输出数据缓冲无效。

图8给出了数据读取操作时间状况,在数据读取过程中,当CE和R/C都处于高电平(假定CS已经处于低电平)的时候,开始测量访问时间.如果这时CS能够使得设备工作,访问时间可延长100纳秒.

图6

在8位的总线接线模式中(和数字公用区连线的12/8输出),地址位AO,必须在CE升高的150毫秒之前和整个读取循环中保持稳定。

如果允许AO变化,将会导致对AD574A输出缓存区的损坏。

AD5474A单机操作

AD5474A可以“独立”模式使用,它是系统里很好用的、可用的和专用的端口,以这种方式不需要用总线连接。

按这方式,CE和12/8置成高位,CS和AO置成低位,而转化由RC控制。

当RC置成高位时,三态缓冲器启动,当RC置成低位时开始转换。

其允许两种控制信号一种高电位脉冲,低高电位脉冲。

由如图11所示的低脉冲操作。

在这种情况下R/C下降沿的输出响应被强制为高阻状态,在一个转换周期结束后置回有效逻辑。

STS线在R/C变为低电平600ns后变为高电平,当数据有效300ns后恢复低电平。

图7

如果转换是由如图12所示的高电平脉冲所初始化的,那么在R/C为高电平时,数据链是被允许的。

R/C的下降沿启动下一个转换,并且数据链返回到三态(并一直保持三态),知道下一个R/C高电平脉冲出现。

图8

通常应用R/C单机模式下的低脉冲。

图13阐明了典型的8086型处理机的单机构造。

额外的74F/S374插销提高了总线的访问/放行次数并协助简化转炉数-模部分的连接线。

图9

AD574与单片机接口

AD574A的控制逻辑使得绝大多数情况下和微处理器系统总线直接连线变成可能。

然而它不可能描述出每一种微处理器类型的接口连接的所有细节,下面将举几个具有代表性的例子。

典型的数模转换器接口程序序列涉及以下几步:

首先,在初始化会话的时候,地址被写进数模转换。

处理器必须等待会话周期的结束,因为多数数模转换器需要一个以上的指令周期来完成会话操作。

当然,有效数据只有在会话结束后才能被读取。

AD574A提供信号端输出(STS),它能指示会话过程。

这个信号可以由处理器通过读取外部三态缓冲(或其它输入端口)获得。

如果系统的计时要求非常严格(请记住AD574A的最大转换时间只有35毫秒)并且处理器在ADC转换周期中有其它任务要做的话,这个STS信号同样可以用于产生一个中断信号传递给转换过程。

另一种可行的延时方法是,先假设模数转换器会消耗35微秒来进行转换,然后插入足够多的空指令来保证处理器消耗掉35微秒的时间。

一旦建立,即完成转换,可以读取数据.在8位(或数位更少)ADC的情况下,单次读数运行即已足够.在转换器数位多于总线可使用数位的情况下,须选择数据格式,需进行多重读数运行.AD574A含有内部逻辑(器),允许通过选择连接12/8输入而直接到8位或多或16位数据总线界面上。

在采用16位数据总线时,(12/8高)数据总线(DB11通过DB0)既可以连接到数据总线的12位有效位或12位无效位。

剩余4位应用软件将其掩蔽.到8位数据总线的界面是采用左优格式来实现的。

在数位的上半部偶数地址(A0低)包含8MSBs(DB11通过DB4).。

奇数地址(A0高)包含4LSBs(DB3throughDB0),后面跟有4个零,从而消除数位掩蔽指令.

AD574A可以在输入/输出或者储存映像结构中被接线到Z-80处理机上。

图15阐明了一个输入/输出或者映像结构。

Z-80使用A0–A7地址线来解码输入/输出端口地址。

Z-80的一个有趣的特性就是当进行I/O操作时会自动插入一个等待状态,允许AD574A和时钟频率高达4MHz的Z-80处理器一起使用。

对于高于4MHz的实际应用,可以使用图16所展示的等待状态发生器。

在配置内存内部,AD574A可以和时钟频率高达2.5MHz的Z-80处理器通过接口相连接。

12-BitA/DConverter

【Abstract:

】AD574isa12bitA/DconverterAnalogproducedbyDevicecompanyAmerica.ItusessuccessiveapproximationtypeA/Dconverter,themaximumconversiontimeis25us,theconversionprecisionof0.05%,fastconversionsosuitableforhighprecisionsamplingsystem.Thechipcontainsamicroprocessorexcuselogic(threestateoutputbuffer),soitcanbedirectlyconnectedwiththevarioustypesof8bitor16bitmicroprocessors,withouttheneedforadditionallogicinterfacecircuit,cuttingcanbecompatiblewithCMOSandTTLcircuit,canworkinavarietyofcomplexenvironment.

Keywordshighprecisionsuccessiveapproximationconverter

CIRCUITOPERATION

TheAD574Aisacomplete12-bitA/Dconverterwhichrequiresnoexternalcomponentstoprovidethecompletesuccessiveapproximationanalog-to-digitalconversionfunction.AblockdiagramoftheAD574AisshowninFigure1.

Figure1.BlockDiagramofAD574A12-BitA-to-DConverter

Whenthecontrolsectioniscommandedtoinitiateaconversion(asdescribedlater),itenablestheclockandresetsthesuccessiveapproximationregister(SAR)toallzeros.Onceaconversioncyclehasbegun,itcannotbestoppedorrestartedanddataisnotavailablefromtheoutputbuffers.TheSAR,timedbytheclock,willsequencethroughtheconversioncycleandreturnanend-of-convertflagtothecontrolsection.Thecontrolsectionwillthendisabletheclock,bringtheoutputstatusflaglow,andenablecontrolfunctionstoallowdatareadfunctionsbyexternalcommand.

Duringtheconversioncycle,theinternal12-bitcurrentoutputDACissequencedbytheSARfromthemostsignificantbit(MSB)toleastsignificantbit(LSB)toprovideanoutputcurrentwhichaccuratelybalancestheinputsignalcurrentthroughthe5kΩ(or10kΩ)inputresistor.Thecomparatordetermineswhethertheadditionofeachsuccessively-weightedbitcurrentcausestheDACcurrentsumtobegreaterorlessthantheinputcurrent;ifthesumisless,thebitislefton;ifmore,thebitisturnedoff.Aftertestingallthebits,theSARcontainsa12-bitbinarycodewhichaccuratelyrepresentstheinputsignaltowithin1/2LSB.

Thetemperature-compensatedburiedZenerreferenceprovidestheprimaryvoltagereferencetotheDACandguaranteesexcellentstabilitywithbothtimeandtemperature.Thereferenceistrimmedto10.00volts0.2%;itcansupplyupto1.5mAtoanexternalloadinadditiontotherequirementsofthereferenceinputresistor(0.5mA)andbipolaroffsetresistor(1mA)whentheAD574Aispoweredfrom15Vsupplies.IftheAD574Aisusedwith12Vsupplies,orifexternalcurrentmustbesuppliedoverthefulltemperaturerange,anexternalbufferamplifierisrecommended.AnyexternalloadontheAD574Areferencemustremainconstantduringconversion.Thethin-filmapplicationresistorsaretrimmedtomatchthefull-scaleoutputcurrentoftheDAC.Therearetwo5kinputscalingresistorstoalloweithera10voltor20voltspan.The10kbipolaroffsetresistorisgroundedforunipolaroperationandconnectedtothe10voltreferenceforbipolaroperation.

DRIVINGTHEAD574ANALOGINPUT

Figure2.OpAmp–AD574AInterface

Theoutputimpedanceofanopamphasanopen-loopvaluewhich,inaclosedloop,isdividedbytheloopgainavailableatthefrequencyofinterest.Theamplifiershouldhaveacceptableloopgainat500kHzforusewiththeAD574A.Tocheckwhethertheoutputpropertiesofasignalsourcearesuitable,monitortheAD574’sinputwithanoscilloscopewhileaconversionisinprogress.Eachofthe12disturbancesshouldsubsideinsorless.

Forapplicationsinvolvingtheuseofasample-and-holdamplifier,theAD585isrecommended.TheAD711orAD544opampsarerecommendedfordcapplications.

SAMPLE-AND-HOLDAMPLIFIERS

AlthoughtheconversiontimeoftheAD574Aisamaximumof35s,toachieveaccurate12-bitconversionsoffrequenciesgreaterthanafewHzrequirestheuseofasample-and-holdamplifier(SHA).IfthevoltageoftheanaloginputsignaldrivingtheAD574Achangesbymorethan1/2LSBoverthetimeintervalneededtomakeaconversion,thentheinputrequiresaSHA.

TheAD585isahighlinearitySHAcapableofdirectlydrivingtheanaloginputoftheAD574A.TheAD585’sfastacquisitiontime,lowapertureandlowaperturejitterareideallysuitedforhigh-speeddataacquisitionsystems.ConsidertheAD574Aconverterwitha35sconversiontimeandaninputsignalof10Vp-p:

themaximumfrequencywhichmaybeappliedtoachieveratedaccuracyis1.5Hz.However,withtheadditionofanAD585,asshowninFigure3,themaximumfrequencyincreasesto26kHz.

TheAD585’slowoutputimpedance,fast-loopresponse,andlowdroopmaintain12-bitsofaccuracyunderthechangingloadconditionsthatoccurduringaconversion,makingitsuitableforuseinhighaccuracyconversionsystems.ManyotherSHAscannotachieve12-bitsofaccuracyandcanthuscompromiseasystem.TheAD585isrecommendedforAD574Aapplicationsrequiringasampleandhold.

Figure3.AD574AwithAD585SampleandHold

SUPPLYDECOUPLINGANDLAYOUT

CONSIDERATIONS

ItiscriticallyimportantthattheAD574Apowersuppliesbefiltered,wellregulated,andfreefromhighfrequencynoise.Useofnoisysupplieswillcauseunstableoutputcodes.Switchingpowersuppliesarenotrecommendedforcircuitsattemptingtoachieve12-bit

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- AD574 中英文 翻译 解析

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《初级会计实务》试题题库大全及答案详解.docx

《初级会计实务》试题题库大全及答案详解.docx

2016年高考全国I卷文综历史试题评分细则及分析PPT文档格式.ppt

2016年高考全国I卷文综历史试题评分细则及分析PPT文档格式.ppt