数字逻辑实验知识点总结.docx

数字逻辑实验知识点总结.docx

- 文档编号:26023473

- 上传时间:2023-06-17

- 格式:DOCX

- 页数:14

- 大小:146.04KB

数字逻辑实验知识点总结.docx

《数字逻辑实验知识点总结.docx》由会员分享,可在线阅读,更多相关《数字逻辑实验知识点总结.docx(14页珍藏版)》请在冰豆网上搜索。

数字逻辑实验知识点总结

数字逻辑实验报告、总结

专业班级:

计算机科学与技术3班学号:

41112115姓名:

华葱

一、实验目的

1.熟悉电子集成实验箱的基本结构和基本操作

2.通过实验进一步熟悉各种常用SSI块和MSI块的结构、各管脚功能、工作原理连接方法

3.通过实验进一步理解MSI块的各输入使能、输出使能的作用(存在的必要性)

4.通过实验明确数字逻辑这门课程在计算机专业众多课程中所处的位置,进一步明确学习计算机软硬件学习的主线思路以及它们之间的关系学会正确学习硬件知识的方法。

二、实验器材

1.集成电路实验箱

2.导线若干

3.14插脚、16插脚拓展板

4.各种必要的SSI块和MSI块

三、各次实验过程、内容简述

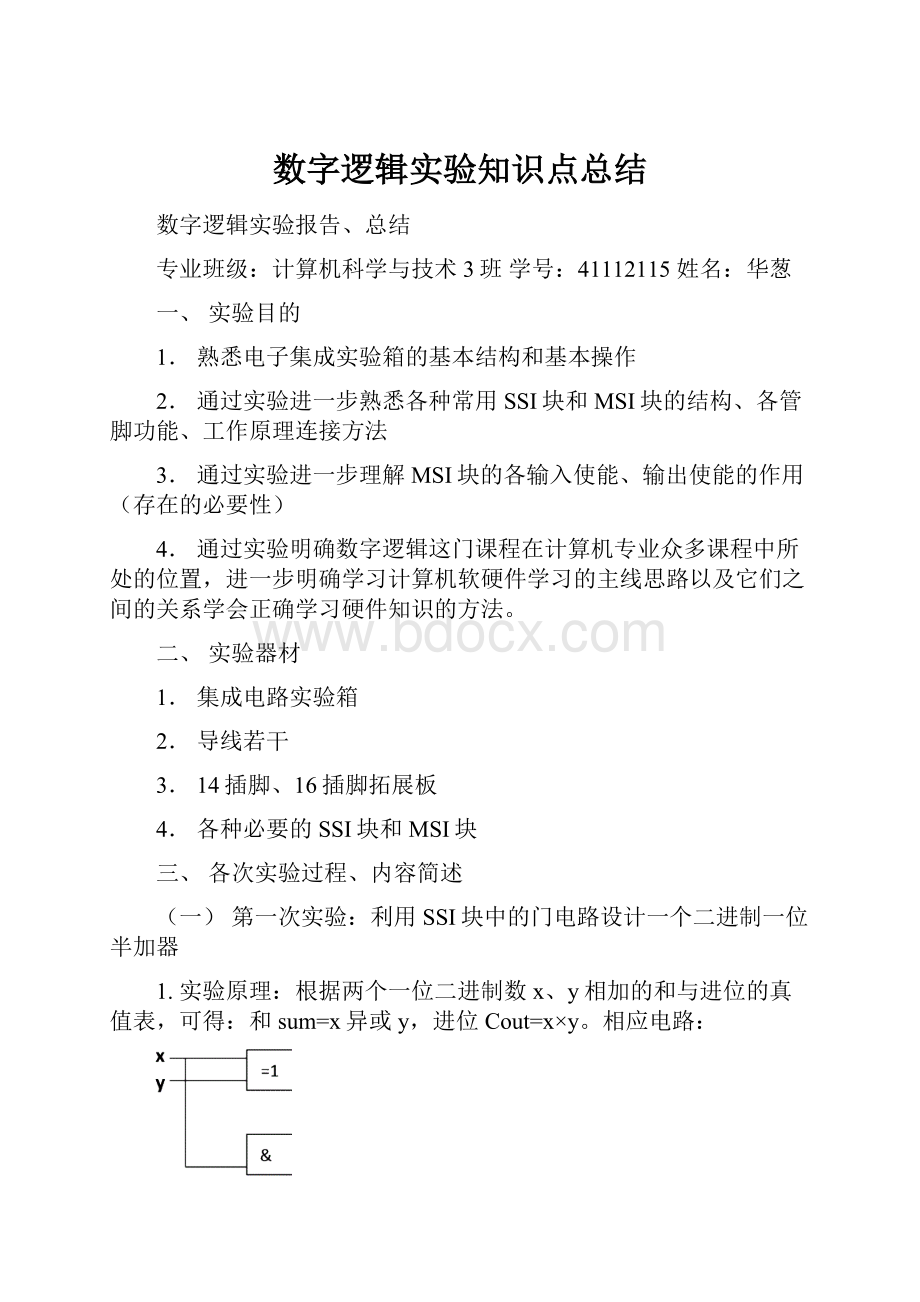

(一)第一次实验:

利用SSI块中的门电路设计一个二进制一位半加器

1.实验原理:

根据两个一位二进制数x、y相加的和与进位的真值表,可得:

和sum=x异或y,进位Cout=x×y。

相应电路:

2.实验内容:

a)按电路图连接事物,检查连接无误后开启电源

b)进行测试,令

c)如果输出位的变化情况与真值表所述的真值相应,则达到实验目的。

(二)第二次实验:

全加器、74LS138译码器、74LS148编码器、74LS85比较器的测试、使用,思考各个输入、输出使能端的作用

1.实验原理:

a)全加器

i.实验原理:

在半加器的基础上除了要考虑当前两个二进制为相加结果,还要考虑低位(前一位)对这一位的进位问题。

由于进位与当前位的运算关系仍然是和的关系,所以新引入的低位进位端Cin应当与当前和sum再取异或,而得到真正的和Sum;而进位位Cout的产生有三种情况:

Cout=xy+xCin+yCin得电路图(也可以列出关于Cin的真值表,利用卡诺图求解Cin的函数表达式):

ii.实验内容:

进行测试,穷举

iii.如果输出位的变化情况与真值表所述的真值相应,则达到实验目的。

b)74LS138译码器

i.实验原理:

译码器是一个能够将一串序列号(我个人理解为地址)所对应的有序编号(按照某种认为约定)进行表达的电子逻辑器件,74LS138译码器是译码器的一种,它能够将一个与十进制整数值等值的二进制序列翻译为相应的十进制值,将信号输出在相应的数据线上。

原理:

每一个一位(0~7)十进制值Yi都对应一个三位二进制序列的表达,也就对应一个极小项mi,即Yi=mi,则可根据mi对应的三个输入变量组合设计门电路(例如Y5=m5=ABC)。

将这8个十进制值都做这样的门电路设计,在进行相应的封装、集成,就形成了这种3-8译码器,其外部逻辑状态如图所示:

__

ii.实验内容:

按要求连接电路,将使能端按

iii.思考:

G1,G2A,G2B作用。

1.G1的作用:

G1在3-8译码器中起开启/封锁各与门的作用,它的存在决定了该3-8译码器芯片是否工作,因此如果需要拓展译码输入的位数由3位到多位,则需要利用该使能端。

如:

若需要设计一个4线-16线译码器,则可用最高位N3控制G1,因为如果N3为0则表明输入实际上是3位二进制,译码只许一块3-8译码器,但如果N3为1则表明输入为4位二进制,则需要开启第二块74LS138工作,因此可以通过N3的值驱动第二块74LS138,所以N3可以接到第二块74LS138的G1端。

2.G2A的作用:

如1所述,当N3的值为1(N3N2N1N0所对应的十进制大于7了),则第二块74LS138需要启用,但由于Yi的i>7因此第一块74LS138不再有译码输出,因此第一块74LS138需要被封锁,这如果用第一块74LS138的G1来控制,这将会破坏译码器器件使能输入的一致性(标准性)影响将来进一步的级联拓展(这将在3中具体说明)。

G2A的存在就解决了这个问题,N3可以通过G2A来控制第一块74LS138的工作状态,而不影响整个4线-16线译码器的使能。

3.G2B的作用:

考虑到整个4线-16线译码器的使能控制以及译码器器件输入使能的一致性,即人们希望设计出来的4线-16线译码器能够像74LS138一样具有三个使能端,第一个高有效,第二、三两个低有效,这样可以方便进一步的级联扩展,则有必要存在一个低有效使能端作为整个4-16译码器的第一个低有效使能端,而3-8译码器的G1和G2A已被占用,不能承担此项工作,这就是G2B存在的意义。

4.

其实根据我个人的理解,G1,G2A,G2B存在的意义并不是为方便级联拓展,因为级联的含义是前一个译码器的输出作为后一个译码器的输入,它解决的是n线-(8n-1)线(n为3的倍数)译码器设计,而4-16译码器(具体电路如图所示)的结构并不是两个74LS138级联,而是并联。

(注:

由于我对译码器的级联比较熟悉,而对译码器的并联较为生疏,因此我在此只做译码器并联的复习,级联的问题省略)

c)74LS148编码器

i.实验原理:

当译码器的输出端数量小于输入端数量的时候,译码器就成为了编码器。

按照我的理解,我认为编码器的工作于译码器的工作互逆,如前所述,译码器是将一个十进制整数对应的二进制翻译到对应以这个十进制为下标的数据线上,而编码器的工作机制则相反,它能够通过判断哪根数据线上有数据信号,则将其还原为数据线下标十进制值对应的二进制代码,并将其结果输出。

如果将一个74LS138的8个输入端分别接到一个74LS148对应的8个输入端,构成一个组合电路,并让它正常工作,那么输入的三位二进制数将先被翻译成相应数据线上的内容,再输入到编码器里面又编码回对应的三位二进制数,即输入什么将输出什么,相当于什么都没有做,因此我认为编码器工作原理与译码器工作原理互逆。

其外部逻辑状态为:

ii.实验内容:

在每一个Ii(0≤i≤7)对应的管脚上先后分别输入信号,观察A2A1A0的输出信号变化,如果输出对应的二进制值与i相等则达到实验目的。

iii.思考:

编码器为什么要有优先权?

两个输出使能GS和EO的存在有什么意义?

经过测试,同时在编码器的多个输入管脚Ii上送入信号,输出信号的值总是与下标i最大的Ii数据线对应的值相等,即其输入到其他下标较小的管脚中的信号没有被编码。

产生这个现象的原因就在于编码器的编码存在优先权。

反过来想,如果编码器没有优先权,那么当多个数据输入到编码器中,则编码器无法判断输入的数据究竟哪一个该编码,进而导致输出错误。

因此,编码需要考虑优先权。

应用:

医院里的病房都分一般病房和重症监护室,由于重症监护室的病人更需要时时关注,那么当同时有两个求助信号从病房送到护士站的时候,如果其中一个信号来自一般病房,另一个来自重症监护室,在护士站受到的信号应是来自重症监护室的求助信号,而那个一般病房的信号将由于优先权低于重症监护室的信号而被“忽略”。

另外,编码器还可用作数据寻址,将一个数据信号翻译为其对应的地址,在计算机内部的数据总线上,挂有若干的外部设备,当外部设备需要进行某种工作时,都要向CPU发送请求,这个请求将对应一个地址,使得CPU在该地址取相应的指令来授权该外部设备工作,当同一时刻有多个外部设备向CPU发送请求时,由于编码器具有优先权选择性,CPU将选择对应编码优先权最高的外部设备做授权工作。

这样就不会由于若干的外部设备共享一根数据总线,发送求的时候产生混乱。

输出使能EO的作用:

与译码器类似,EO用作级联扩展,当第一块74LS148的输入全部无效时,也就是需要编码的信号Ii中i大于7,也就是在下一块74LS148的某个输入管脚,此时第一块74LS148的EO为有效输出,而第二块需要开启工作,因此应把第一块74LS148的EO接到第二块74LS148的EI上,与74LS138类似,它能解决(8n-1)线-n线(n为3的倍数)的编码器设计问题。

输出使能GS的作用:

此问题仍然与译码器类似,GS不是供74LS148级联的而是供它并联,解决(8n-1)线-n线(n不是3的倍数)编码器的设计问题,比如设计一个16线-4线编码器。

下面就16线-4线编码器的设计谈一谈我的收获:

16线输入的编码器与74LS148的区别在于它需要编码的信号不一定在I0~I7中,还有可能在I8~I15中。

就此需要分类讨论,当需要编码的信息落在I0~I7范围内,也就是编码后的四位二进制结果最高位A3为0,那么第一块74LS148一定要使能,而74LS148没必要开启。

当需要编码的信息落在I8~I15也就是编码后的四位二进制结果最高位A3为1,而编码结果的后三位由第一块74LS148的输出端A2A1A0输出。

综上所述,编码结果的最高位为0时,也就是Ii的i小于7时,第二块74LS148不工作,而编码结果的最高位A3为1时,也就是Ii的i大于7时,输入信号从第二块74LS148的相应管脚输入,第一块74LS148的所有输入均无效,其EO有效输出,因此第二块74LS148必须要工作,而能够标志这种输入范围和是否工作关系的信号就是GS信号,恰好可以让第一块74LS148的EO使能第二块74LS148(接到其EI上)因此GS就正是我们要找的编码结果的最高位A3。

具体电路如图所示:

d).74LS85比较器的测试

__

__

i.实验原理:

比较两个二进制数的方法是从最高位开始,依次比较每一位。

在比较到第i位时,不仅要看两个二进制数第i位的大小,还要看第i-1位的比较结果,由二者共同决定第i位的比较结果。

74LS85的内部逻辑状态原理:

在比较两个数A、B的第i位Ai和Bi时,如果Ai>Bi,则一定有Ai=1,Bi=0,将此情况记为PGi,则PGi=AiBi;同理,Ai Ai=1,Bi=1和Ai=0,Bi=0,因此PEi=Ai⊙Bi(可用与或非门实现)。 74LS85是四位比较器,每一位比较的原理都如此,比较结果再和第i-1位的比较结果进行综合处理。 具体外部逻辑状态为: i.实验内容: 置入任意的 ii.思考: 如果比较的位数为8位,该如何利用74LS85设计电路? 当需要比较的数据为8位时,则将这两个数据分为两段段,即高四位和低四位,使用两块74LS58,第一块用于比较低四位,其 电路图略。 (三)第三次实验: 74LS74D触发器、74LS1634位二进制计数器、74LS1668位二进制移位寄存器 1).实验原理: a).74LS74D触发器。 i.实验原理: D触发器的内部原理在理论课上老师已经给我们讲过,我就不在此阐述。 在这里我只想专门谈一谈触发器与锁存器的区别以及锁存器如何实现边沿触发。 对于锁存器而言,要求在控制(时钟)输入CLK有效期间内,输入数据D稳定不变,但由于实际工程运用电子电路庞杂,数据难免会产生错误而导致传输不稳定(比如空翻现象),如果刻意要求数据稳定不变使器件正确工作将会给实际使用带来不便。 边沿触发的产生就很好的解决了这个问题,边沿触发可以使器件在控制信号的有效边沿时接收数据。 就D触发器而言,由于D锁存器的地方就在于多了两个信号接收门(与非门),更重要的是D触发器比D锁存器内部多了三条反馈数据线。 正是由于这三条反馈数据线,使得时序电路的产生成为了可能,让电子元器件在控制数据上“智能”了。 实验采用74LS74芯片,其中封装了两个D触发器其1/2外部逻辑状态为: ii.实验步骤: 验证次态于现态之间的关系,即次态方程。 给CLR送入一个0信号,并给CLK端送入一个时钟脉冲,使D触发器清零;给D端送入一个信号,并给CLK端送入一个时钟脉冲,使得数据送到D触发器内,再向CLK端送入一个时钟脉冲,观察输出Q与D触发器次态真值表是否一致,如果一致则达到实验目的。 iii.实验思考: D触发器是时序电路的细胞,是时序电路的最小单位,它让电子器件在时域上有序处理、存储数据成为可能,其原理是时序电路原理的基础。 (注: 由于我比较熟悉74LS163的结构,在此就不给出其外部逻辑状态了) b).74LS1634位二进制计数器 i.实验原理: 74LS163是一个可以清零、可以设置计数模数、计数起点、可拓展的计数器。 清零可以通过其清零端实现,而模数可通过置数端LD配合各输出端Qi实现,计数的起点由DCBA输入端输入,而两个使能端则实现进一步拓展级联。 ii.实验步骤: 将74LS163的ENP与ENT使能端接+5V信号,使芯片使能向CLR端送入信号并向CLK端送入信号,使得芯片清零。 将CLD和LD接GND,给 给CLK端送入一个时钟脉冲,观察输出是否为初始置数 iii.思考: 使能端ENP和ENT的作用。 为了实现多位二进制数(4位以上)加1计数的功能,需要给74LS163级联拓展,与译码器级联类似,如果数据低位的输出进位有信号,说明现有的74LS163已经不够表达当前的输出数据,需要借助另一块74LS163来进行表达,此时就涉及到一个问题,即第二块74LS163工作使能的控制,ENT使能端就可以负责此功能。 因此如果需要做级联,则第一级的74LS163进位输出RCO接入到第二级74LS163的ENT上。 因此,ENT除了控制电路处于置数方式或计数方式外,还控制最高位的ROC是否有效。 当ENT做了级联必须的使能时,还需要另一使能端控制较高级的74LS163的工作使能,这就是ENP存在的意义。 c).74LS166并入-串出移位寄存器 i.实验原理: 74LS166结构与74LS163结构比较相似,其SH/LD端相当于74LS163的ENT端。 当74LS166工作起来后,唯一的输出端Qh则会将实现置入芯片数据的8个二进制位 由于我对于74LS166的结构也比较熟悉,因此就不在此给出其外部逻辑状态了。 ii.实验内容: 实验准备工作与74LS163实验相同。 送信号到SH/LD中,并向CLK中送入一个时钟脉冲,使芯片处于置数的工作状态,任意置入一组8位二进制信号给 所有试验到此结束。 四、实验总结 做数字逻辑实验以及老师详细而全面的讲授恶补了我数字逻辑知识的漏洞,纠正了我以前的一些对数字逻辑知识不正确的理解,将曾经抽象的知识变得更容易理解了,极大的提高了我数字逻辑的学习质量以及我的学习兴趣,收获甚大! 上述我对实验内容的报告都是我的收获所在,尤其是译码器编码器的并联拓展、各个MSI块的使能端作用以及运用、时序电路基本原理基本单位的强化理解(D触发器原理),这些都是我在做实验之前的薄弱环节,而通过做实验,我现在对数字逻辑这门学科有了一个更深刻更佳正确的认识,最后,我就“作用”和“地位”两个角度谈一谈我对数字逻辑这门课的理解与认识。 五、理解内化 计算机专业的课程学习有两条主线: 硬件和软件。 软件课程之间没有很明显的关联,但是硬件课程则是一环套一环,逐层递进的。 由模拟电子技术中的晶体三极管和CMOS技术生产的晶体场效应管组成最基本的门电路,通过门电路之间的组合产生组合逻辑电路和时序电路以及计算机中必要的SSI块、MSI块和TSI块,这些都是需要必要的数字逻辑知识作为基础的,这些块进一步集成,就产生计算机最基本的硬件结构(CPU、寄存器、存储器等),最后由这些硬件结构搭建起冯诺依曼体系的计算机结构。 而所有这些环节的理论基础都是数学,尤其是离散数学(比如数字逻辑中常用的最小项的和、最大项的积本质上就是离散数学中析取范式与合取范式),如图所示。 在时钟脉冲电流的作用下,CPU通过可编程器件(如8259A等)管理、授权各个硬件模块与模块之间工作与配合,以此来完成读取计算机指令、执行计算机指令。 而指令就是人与计算机沟通的桥梁,人通过相应的语言(如汇编语言)来控制计算机执行指令,进而管理硬件资源。 当然,在此之后我们还有更多的课程需要学习,来搭建计算机硬件学习的主线。 以上就是我对数字逻辑课程的理解与认识,总之,这几次次试验课让我对于数字逻辑课程有了一个更加正确而深入的认识,学习质量提高显著,学习方法也有了改善。 感谢老师的讲授与指导! 我会继续刻苦学习。 目录 一、试验目的…………………………………………第01页 二、实验器材…………………………………………第01页 三、各次实验过程、内容简述………………………第01页 (一)第一次实验……………………………………第01页 半加器…………………………………………第01页 (二)第二次实验……………………………………第02页 a).全加器…………………………………………第02页 b).74LS138译码器…………………………………第03页 c).74LS148编码器…………………………………第07页 d).74LS85比较器…………………………………第11页 (三)第三次实验……………………………………第13页 a).74LS74D触发器…………………………………第13页 b).74LS1634位二进制计数器…………………………第14页 c).74LS166并入-串出8位移位寄存器…………………第15页 四、实验总结…………………………………………第16页 五、理解内化…………………………………………第16页 数字逻辑实验报告 专业班级: 11级计算机科学与技术3班 姓名: 华葱 学号: 41112115

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 逻辑 实验 知识点 总结

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《初级会计实务》试题题库大全及答案详解.docx

《初级会计实务》试题题库大全及答案详解.docx