《数字逻辑与数字系统》期末考试试题.docx

《数字逻辑与数字系统》期末考试试题.docx

- 文档编号:25847967

- 上传时间:2023-06-16

- 格式:DOCX

- 页数:72

- 大小:270.26KB

《数字逻辑与数字系统》期末考试试题.docx

《《数字逻辑与数字系统》期末考试试题.docx》由会员分享,可在线阅读,更多相关《《数字逻辑与数字系统》期末考试试题.docx(72页珍藏版)》请在冰豆网上搜索。

《数字逻辑与数字系统》期末考试试题

-

-

北京XX大学2006——2007

-

学年第一学期

-

-

-

-

-

-

A)

-

《数字逻辑与数字系统》期末考试试题(

-

-

-

-

-

-

一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必

-

-

-

-

考试

须按照监考教师指定座位就坐。

-

-

-

-

注意

二、书本、参考资料、书包等与考试无关的东西一律放到考场指定位置。

-

-

-

事项

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》

,有

-

:

-

-

-

考场违纪或作弊行为者,按相应规定严肃处理。

名

-

-

:

-

考试

姓

-

名

-

数字逻辑与数字系统

考试时间

2007年1

月26

日

-

-

课程

姓

-

-

-

-

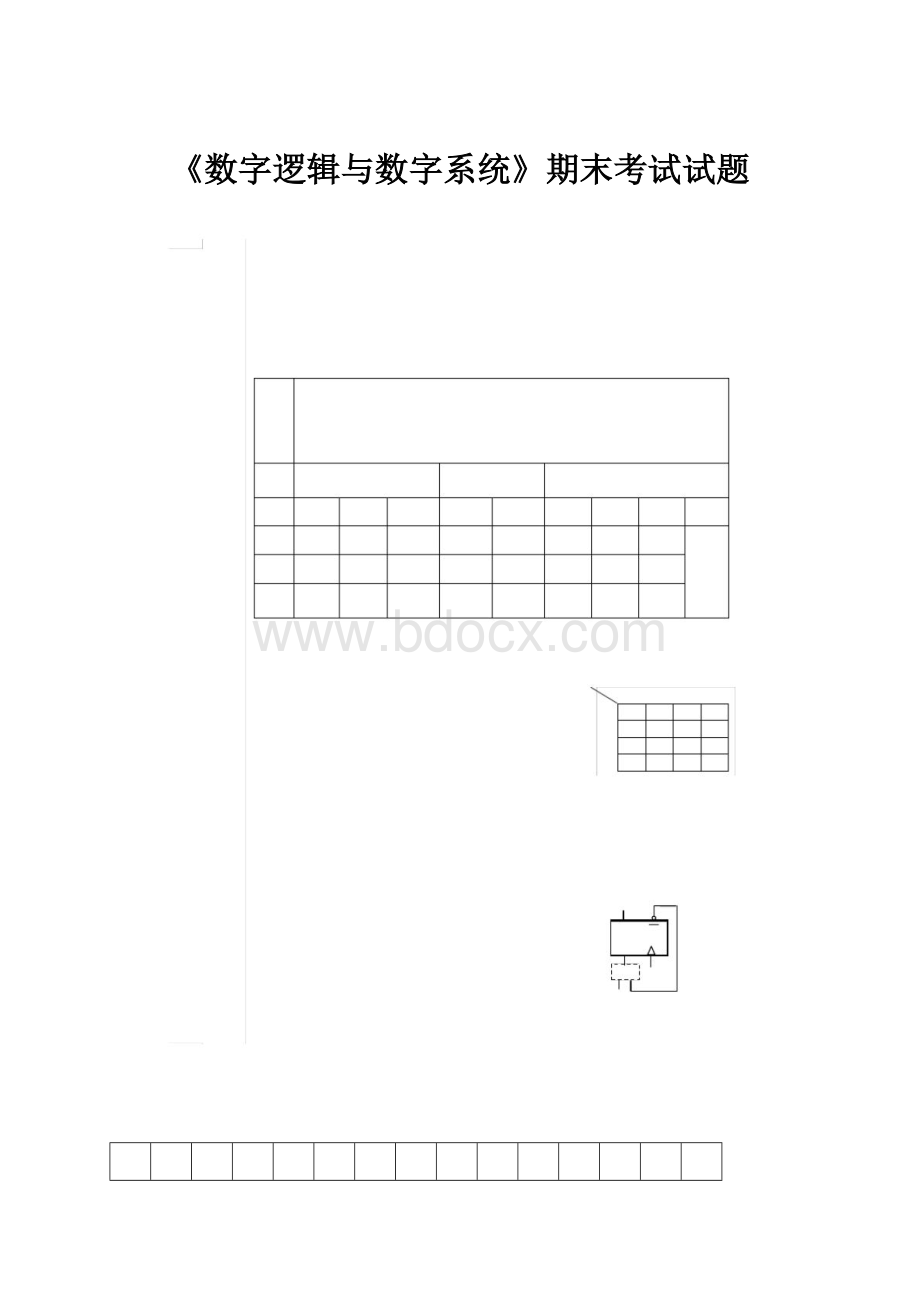

题号

一

二

三

四

五

六

七

八

总分

-

-

线

-

-

-

-

线

满分

10

20

10

10

10

12

14

14

-

-

-

-

-

得分

-

-

-

-

:

-

-

阅卷

号

-

-

教师

:

-

序

-

-

号

-

内

-

-

序

-

班

-

订

内

-

班

-

一、选择题(每小题1分,共10分。

)

订

-

-

-

-

-

-

-

AB

-

1.卡诺图如图1所示,电路描述的逻辑表达式

F=(

)。

00

01

11

10

-

CD

-

-

-

00

1

-

A.

∑m(1,2,4,5,9,10,13,15)

-

-

-

01

1

1

1

1

-

-

B.

∑m(0,1,3,4,5,9,13,15)

-

-

11

1

-

-

C.

∑m(1,2,3,4,5,8,9,14)

-

-

10

1

1

-

-

装

-

D.

∑m(1,4,5,8,9,10,13,15)

-

图1

-

-

装

-

:

-

-

-

2.在下列逻辑部件中,不属于组合逻辑部件的是(

)。

号

-

-

:

-

A.译码器

B.

锁存器

C.

编码器

D.比较器

学

-

号

-

-

学

-

-

-

-

-

3.八路数据选择器,其地址输入端(选择控制端)有(

)个。

-

-

-

-

A.8

B.2

C.3

D.4

-

-

-

-

-

-

4.将D触发器转换为

T触发器,图

2所示电路的虚框

Q

Q

-

-

:

-

-

内应是(

)。

D

-

级

-

-

:

-

班

-

A.或非门

B.

与非门

-

级

-

CP

-

班

-

C.异或门

D.

同或门

-

-

T

-

-

图2

-

-

-

-

-

5.用n个触发器构成计数器,可得到的最大计数模是(

)。

-

-

nB.2nC.nD.2n-1

6.GAL是指()。

A.随机读写存储器B.通用阵列逻辑C.可编程逻辑阵列D.现场可编程门阵列

7.EPROM的与阵列(),或阵列()。

A.固定、固定B.可编程、固定C.固定、可编程D.可编程、可编程

8.在ispLSI器件中,GRP是指()。

A.通用逻辑块B.输出布线区C.输入输出单元D.全局布线区

9.双向数据总线可以采用()构成。

A.三态门B.译码器C.多路选择器D.与非门

10.ASM流程图是设计()的一种重要工具。

A.运算器B.控制器C.计数器D.存储器

二、填空题(每小题

2分,共20分)

1.

图3所示加法器构成代码变换电路,若输入信号

B3B2B1B0为8421BCD码,则输出端

S3S2S1S0为______________________代码。

2.

2:

4译码器芯片如图4所示。

欲将其改为四路分配器使用,应将使能端

G改为

___________________,而地址输入端A、B作为_________________________。

B3

Co

B2

S3

Y0Y1Y2Y3

B1

74LS283

B0

S2

2:

4译码器

A3

加法器

S1

GAB

A2

S0

1

A1

A0

图4

图3

3.门电路的输入、输出高电平赋值为逻辑_________,低电平赋值为逻辑________,这种关系为负逻辑关系。

4.组合逻辑电路的输出只与当时的________状态有关,而与电路_______的输入状态无关。

5.译码器实现___________________译码,编码器实现___________________译码。

6.在同步计数器中,所有触发器的时钟都与___________________时钟脉冲源连在

一起,每一个触发器的

_______________变化都与时钟脉冲同步。

7.时序逻辑电路中输出变量是输入变量和状态变量的函数,

该电路为

____________。

8.在

CP

脉冲作用下,具有图

5(a)所示功能的触发器是

__________,具有图

5(b)所

示功能的触发器是

__________。

X=1

XY=1

φ

X=0

0

1

X=1

XY=0φ

0

1

XY=φ0

X=0

XY=

φ1

(a)

(b)

图5

9.ispLSI器件具有__________________________条编程接口线。

10.小型控制器的结构有________________型、_______________型和计数器型。

三、简答题(各

5分,共10分)

1.写出ispLSI1032

中通用逻辑块

GLB的五种组态模式;指出哪种工作速度最快?

哪

种工作速度最慢?

(

5分)

2.画出小型控制器的组成框图。

(5分)

四、综合逻辑电路分析题(10分)

1.写出图6中三态门的输出信号(2分)

FF

(直接写在图上)

2.写出F的逻辑表达式(4分)

3.说明图6电路的逻辑功能(4分)

五、组合电路设计(10分)

给定如下两种门器件,延迟时间分别为:

2输入与非门

计一个32位串行进位加法器。

1.列出一位全加器真值表,并写出求和、进位逻辑表达式。

20ns、异或门

(4分)

40ns。

设

2.画出加法器逻辑电路图(只画最低

2位),规定输入、输出均为原变量。

(3分)

3.计算加法器求和运算的最长时间。

(3分)

六、时序逻辑分析(12分)

由D触发器组成的同步时序电路如图7所示。

1、写出各触发器状态方程(3分)

2、列出状态转移表(3分)

3、画出状态转移图(3分)

4、说明此电路的逻辑功能(3分)

D0Q0

D1Q1

D2Q2

Q0

Q1

Q2

CP

图7

七、可编程逻辑设计(14分)

X=1

三比特格雷码加/减计数器状态图如图8

所示。

X为输入控制变量,X=1时计数器加,X=0时

H

X=0

100

计数器减,请用ABEL-HDL语言的状态图法

X=1

X=0

设计该计数器(测试向量部可选)。

G

101

X=0

X=1

F

X=0

111

X=1

A

000

E

110

X=1

X=0B001

X=1

X=0

C

011

X=0

X=1

X=0D010

X=1

图8

八、小型控制器设计(14分)

图9所示为数字累加系统的数据通路图,设计计数器型控制器。

寄存器

A从数据总线

上接收一系列输入数据,寄存器

B保存它们的累加结果,加法器完成求和运算,控制器指

挥执行部件自动完成上述运算。

其中LDA,LDB为打入寄存器的控制信号,

ADD为三态门使能

信号。

假设累加系统启动之前寄存器

A、B已清零。

控制器的状态变化发生在

T1节拍脉冲

时间,打入寄存器操作发生在

T2节拍脉冲时间,控制器状态周期为T=T1+T2。

1.画出控制器的ASM图

数据输入

2.列出状态转移真值表

3.写出激励方程和控制信号表达式

LDA

4.画出电路图

寄存器A

控

加

制

法

寄存器B

器

北京XX大学2006——2007学年第一学期

《数字逻辑与数字系统》期末考试试题

(A)标准答案

一、选择题(每小题1分,共10分)

1.A

2.B

3.C

4.D

5.A

6.B

7.C

8.D

9.A

10.B

二、填空题(每小题

2分,共20分)

1.余3码

2.数据输入D、地址控制输入A1、A0

3.0、1

4.输入、原来

5.多对一、一对多

6.同一个、状态

7.米里型

8.D触发器、JK触发器

9.5

10.多路选择器型(MUX)、定序型

三、简答题(各5分,共10分)

1.(5分)ispLSI1032中通用逻辑块GLB的五种组态模式是标准组态,高速直通组

态,异或逻辑组态,单乘积项组态,多模式组态。

其中单乘积项组态最快,多模式和异或逻辑组态最慢。

2.(5分)小型控制器的组成框图。

控制信号

⋯⋯

T1

T2

T2

控制信号译码电路

T

⋯⋯

T1

若干触发器

清零

⋯⋯

激励方程逻辑电路

⋯

反馈输入信号

⋯

四、时序电路分析题(10分)

1、(2分)右图从左到右为A0A1A2A3⋯⋯A15

2、(4分)FA0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15

FA0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15

3、(4分)当变量A0A1A2A3⋯⋯A15全位0时,输出F=1,由打入信号打入标志触发器保存。

F=1标志着三态门输出信号为全0。

这是判别总线上代码全为0的电路。

五、组合电路设计(10分)

1、真值表(2分)

AiBiCi-1SiCi

00000

00110

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Si

Ai

Bi

Ci

表达式:

2分

Ci

AiBi

AiCi1

BiCi1

AiBi

(Ai

Bi

)Ci1

2、画图(3分):

C2C1

S32

S2S1

⋯⋯

C31B32A32

C1B2A2C0B1A1

3、(3分)32位加法器最长时间为:

最低位异或门+31级进位+最高位异或门:

t=40ns+(20+20)ns×31+40ns=1320ns

六、时序电路分析(12分)

1、写出状态方程(3分)

n

1

D0

nn

Q0

Q1Q2

n

1

D1

n

Q1

Q0

n

1

D2

n

Q2

Q1

2、出状态转移表(3分)

n

n

n

n+1

Q1

n+1

n+1

Q2

Q1

Q0

Q2

Q0

0

0

0

0

0

1

0

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

0

1

0

0

1

0

0

0

0

1

0

1

0

1

0

1

1

0

1

0

1

1

3.状态转移图(

3分)

065626

1637

46

4、此电路是五进制计数器,可自启动(

3分)

七、硬件描述语言设计(14分)

MODULEcounter

TITLE'3-bitGraycodecounter';

(3分)

Clock,pin;

Xpin;

Q2,Q1,Q0nodeistype'reg';

QSTATE=[Q3,Q2,Q0];

A=[0,0,0];

A=[0,0,1];

A=[0,1,1];

(3分)

A=[0,1,0];

A=[1,1,0];

A=[1,1,1];

A=[1,0,1];

A=[1,0,0];

(2分)

QSTATE.CLK=Clock;

State_diagramQSTATE

StateA;

CASEX==1:

B;

X==0:

H;

ENDCASE

StateB;

CASEX==1:

C;

(6分)X==0:

A;

ENDCASE

⋯⋯

StateH;

CASEX==1:

A;

X==0:

G;

ENDCASE

E

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字逻辑与数字系统 数字 逻辑 系统 期末考试 试题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《 岁婴幼儿教养方案》.docx

《 岁婴幼儿教养方案》.docx