习题3组合逻辑电路分析与设计数字电子技术含答案.docx

习题3组合逻辑电路分析与设计数字电子技术含答案.docx

- 文档编号:25620889

- 上传时间:2023-06-10

- 格式:DOCX

- 页数:16

- 大小:216.59KB

习题3组合逻辑电路分析与设计数字电子技术含答案.docx

《习题3组合逻辑电路分析与设计数字电子技术含答案.docx》由会员分享,可在线阅读,更多相关《习题3组合逻辑电路分析与设计数字电子技术含答案.docx(16页珍藏版)》请在冰豆网上搜索。

习题3组合逻辑电路分析与设计数字电子技术含答案

习题3

组合逻辑电路分析与设计

数字电子技术

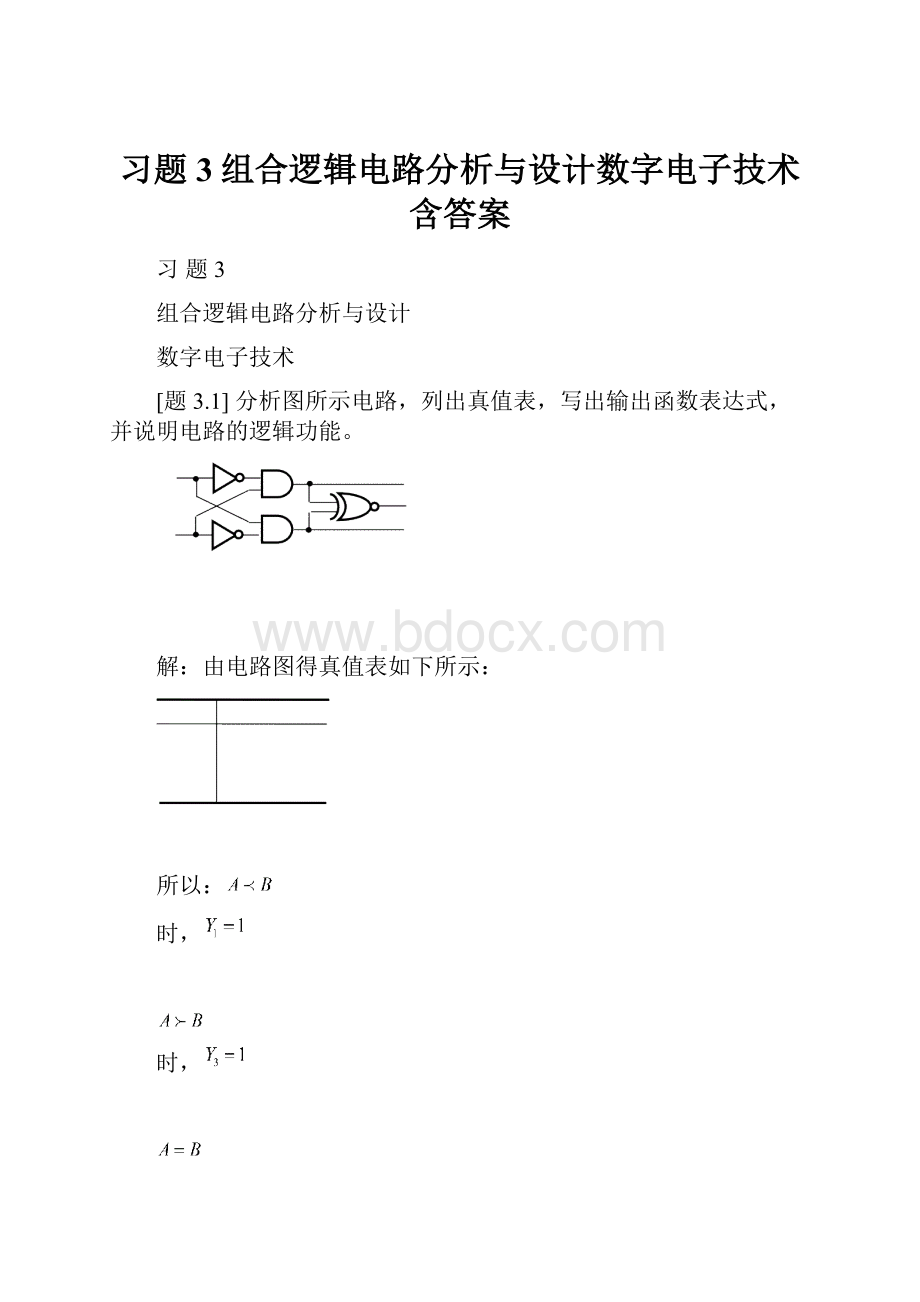

[题3.1]分析图所示电路,列出真值表,写出输出函数表达式,并说明电路的逻辑功能。

解:

由电路图得真值表如下所示:

所以:

时,

时,

时,

电路实现比拟器的功能。

A,B是输入;Y1,Y2,Y3分别是A

[题3.2]分析图题3.2所示电路,说明电路的逻辑功能。

解:

电路的逻辑函数表达式为:

电路的逻辑功能是:

在使能条件EN=1且S=0时,输出A;在使能条件EN=1且S=1时,输出B;使能条件EN=0时,输出高阻态。

电路实现数据选择器的功能。

[题3.3]图题3.3是一个密码锁控制电路。

开锁条件是必须将开锁开关闭合,且要拨对密码。

如果以上两个条件都得到满足,开锁信号为1,报警信号为0,即锁翻开而不报警。

否那么,开锁信号为0,报警信号为1。

试分析该电路的密码是多少。

解:

分析电路可知:

电路的密码是1001。

[题3.4]图题3.4所示电路由4位二进制比拟器7485和4位二选一数据选择器74157组成。

其中74157控制端

的控制作用为:

=0时,Yi=Ai,否那么,Yi=Bi。

试分析图示电路的逻辑功能。

解:

当

时,输出A;当

时,输出B;所以电路的功能是输出A,B中较小的数。

[题3.5]某建筑物的自动电梯系统有五个电梯,其中三个是主电梯〔设为A、B、C〕,两个备用电梯。

当上下人员拥挤,主电梯全被占用时,才允许使用备用电梯。

现需设计一个监控主电梯的逻辑电路,当任何两个主电梯运行时,产生一个信号〔Y1〕,通知备用电梯准备运行;当三个主电梯都在运行时,那么产生另一个信号〔Y2〕,使备用电梯主电源接通,处于可运行状态。

请列出该电路的真值表,并写出Y1、Y2的逻辑表达式。

解:

分析题意得真值表如下:

所以:

[题3.6]用与非门设计一个多数表决电路。

要求A、B、C三人中只要有半数以上同意,那么决议就能通过,但A还具有否决权,即只要A不同意,即使多数人也不能通过。

要求列出真值表,化简逻辑函数,并画出逻辑电路图。

解:

(1)分析题意得真值表如下:

(3)逻辑电路图如以下图示:

(2)函数的逻辑表达式:

[题3.7]用与非门设计一交通灯故障检测电路。

要求三色信号灯R、Y、G中有且只有一灯亮,输出

Z=0,无灯亮或同时有两灯或两灯以上亮均为故障,输出Z=1。

要求列出真值表,写出最简表达式,画出逻辑图。

解:

(1)设灯亮为1,灯灭为0,分析题意得(3)逻辑电路图如以下图示:

真值表如下:

(2)函数的逻辑表达式:

[题3.8]图题3.8表示一热水器的水位情况,虚线表示水位,A、B、C电极被水浸没时会有信号输出。

水面在C、B间时为正常状态,绿灯G亮;水面在B、A间或在C以上时为异常状态,黄灯Y亮;水面在A以下时为危险状态,红灯R亮。

试用SSI器件实现该逻辑功能的电路。

解:

(1)设对于水位A、B、C浸没状态为1,(3)逻辑电路图如以下图示:

露出状态为0,分析题意得真值表如下:

(2)化简后函数的逻辑表达式:

[题3.9]用3线-8线译码器芯片74LS138和必要的门电路实现以下逻辑函数:

〔1〕

〔2〕

〔3〕

解:

〔1〕

〔2〕

〔3〕

[题3.10]用8选一数据选择器实现逻辑函数。

〔1〕

〔2〕

〔3〕

解:

〔1〕

〔2〕

〔3〕

函数真值表如下:

[题3.11]试用4选一数据选择器实现逻辑函数

。

解:

函数真值表如下:

电路图如下所示:

[题3.12]用1片74283实现将余3码转换为8421BCD码的电路。

解:

8421BCD码相当于余3码减3,也即余3码加-3的补码1101。

[题3.13]用学过的器件设计一个检测8421BCD码并将其进行四舍五入的电路。

设四个输入变量为A、B、C、D,当输入伪码时Y1为1,作为告警输出;当输入大于或等于5时,Y2为1,作为四舍五入输出。

解:

列出函数的真值表:

用译码器实现电路:

[题3.14]试用两片4位二进制数加法器74283和必要的门电路组成一个实现两个1位十进制数的8421BCD码相加的加法器。

〔提示:

根据8421BCD码的加法运算规律,当两数之和小于或等于9时,相加的结果与按二进制数相加所得到的结果一样。

而当两数之和大于9时,那么应在按二进制数相加的结果上加6校正。

〕

解:

二进制和8421码和数如以下图所示:

由真值表得逻辑函数表达式为:

[题3.15]试用ROM实现8421BCD码到余3码的转换。

要求画出存储矩阵的点阵图。

解:

8421BCD码和余3码之间的关系用真值表表示如下:

所以:

ROM阵列图如下所示:

[题3.16]画出与以下实体描述对应的元件符号。

〔1〕ENTITYbuf3sIS--三态缓冲器实体

PORT(x:

INSTD_LOGIC;--输入端

ena:

INSTD_LOGIC;--输入端

y:

OUTSTD_LOGIC);--输出端

ENDENTITYbuf3s;

〔2〕ENTITYmux41aIS--四选一数据选择器实体

PORT(in0,in1,in2,in3:

INSTD_LOGIC;--数据输入端

sel:

INSTD_LOGIC_VECTOR(1DOWNTO0);--地址输入

y:

OUTSTD_LOGIC);--输出端

ENDENTITYmux41a;

解:

〔1〕〔2〕

[题3.17]阅读例3.3.1,试编写一个实现变量A、B相异或的VHDL源程序。

解:

ENTITYorgateIS

PORT〔a,b:

INBIT;

y:

OUTBIT〕;

ENDENTITYorgate;

ARCHITECTUREoneOForgateIS

BEGIN

y<=aXORb;

ENDARCHITECTUREone;

[题3.18]试编写一个实现半加器的VHDL源程序。

解:

ENTITYorgateIS

PORT〔a,b:

INBIT;

S,C0:

OUTBIT〕;

ENDENTITYorgate;

ARCHITECTUREoneOForgateIS

BEGIN

S<=aXORb;

C0<=aANDb;

ENDARCHITECTUREone;

[题3.19]逻辑电路如图题3.19所示,假设图中门电路的延时均为5ns,试根据A的输入波形,画出Y1和Y的波形。

解:

Y1和Y的波形的波形图如下图:

[题3.20]逻辑电路如图题3.20所示,判断该电路是否存在冒险现象,如果存在,请通过修改逻辑设计消除冒险现象。

解:

分析电路得逻辑函数表达式:

当

时,

;

当

时,

;

所以电路存在冒险现象。

如果通过修改逻辑设计消除冒险现象,就加上冗余项。

结果是:

本文档局部内容来源于网络,如有内容侵权请告知删除,感谢您的配合!

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 习题 组合 逻辑电路 分析 设计 数字 电子技术 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《爱和自由》读书心得15篇.docx

《爱和自由》读书心得15篇.docx