AltiumDesignerWinter09通用技巧窍门.docx

AltiumDesignerWinter09通用技巧窍门.docx

- 文档编号:25325564

- 上传时间:2023-06-07

- 格式:DOCX

- 页数:21

- 大小:352.62KB

AltiumDesignerWinter09通用技巧窍门.docx

《AltiumDesignerWinter09通用技巧窍门.docx》由会员分享,可在线阅读,更多相关《AltiumDesignerWinter09通用技巧窍门.docx(21页珍藏版)》请在冰豆网上搜索。

AltiumDesignerWinter09通用技巧窍门

I.AItiumDesignerWinter09支持中文版本,点击"DXP'—"preferences(优先选项)”在弹出的"Preferenee”窗口中选择“System"—“General”在右侧最下面的"localization”有个"uselocalizationresource"选项,打对勾选上。

点击OK,重启AltiumDesigner6,即出来中文界面。

2.自己连的线在交叉的地方是没有接点的,需要手工增加接点使其连接,方法:

快捷键

P—J;

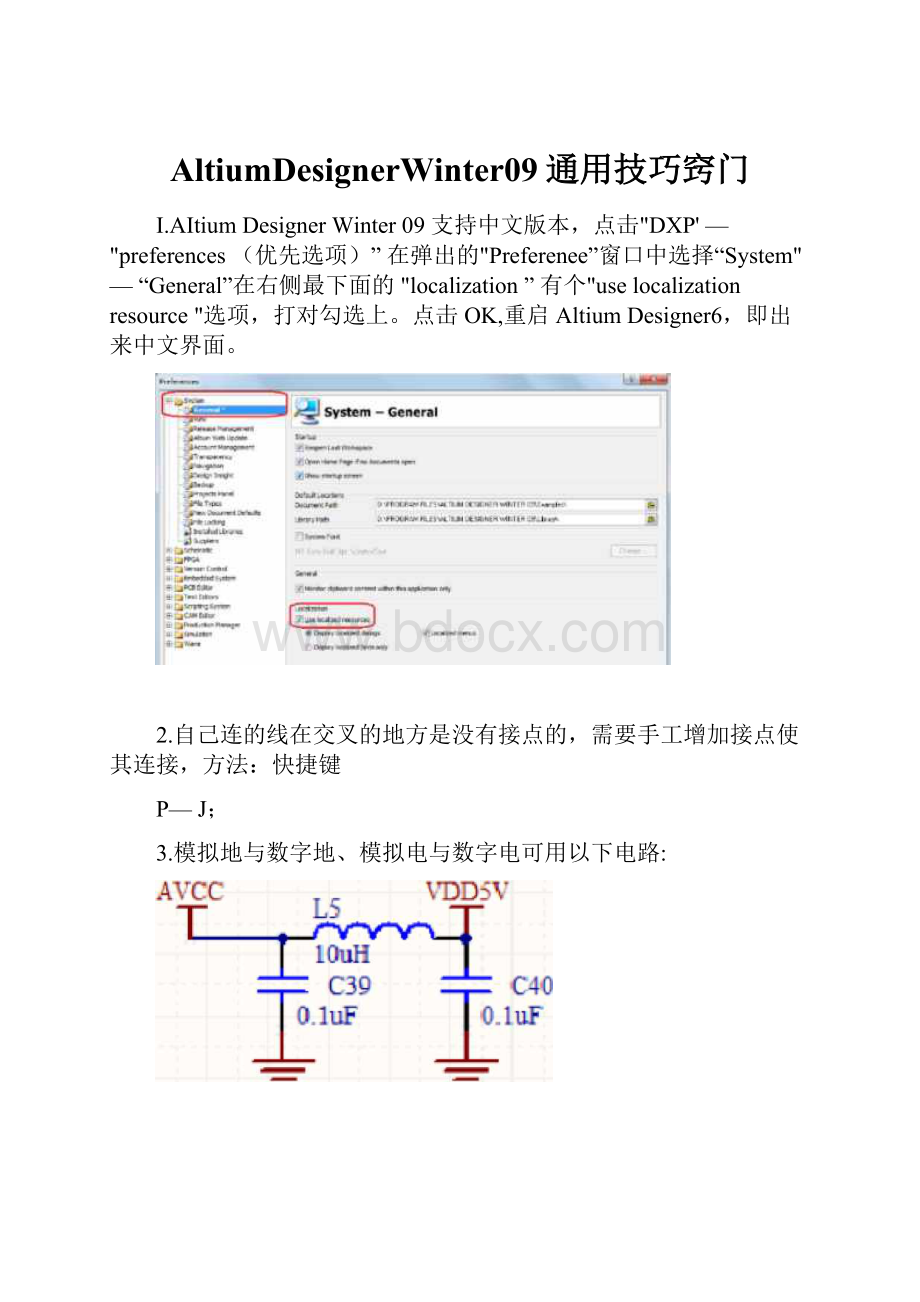

3.模拟地与数字地、模拟电与数字电可用以下电路:

AGXDGND

4.快速修改相同处,如某图中部分电阻的封装为

0603A,现全部改为R0603:

选中某个封装为0603A的电阻,点击右键,选择“查找相似对象”,弹出如下对话框

在参考符号"SymbolReferenee”和当前圭寸装“CurrentFootprint”中选择“Same”,同时选中下方的“选择匹配”,点击确定,出现如下窗口:

找到“CurrentFootprint”项,将封装改为R0603。

PCB'—“PCBlibrary”,

5•将封装并添加到封装库:

打开封装后,点击软件右下角的

弹出“PCBlibrary”窗口,如下图:

PCBLibrary占j

面具:

L

|陽同国團选择(S國缩啟£)

组件

命名焊盘原始的

新建览元祥(N]

祖件向导(W)t„

就m

I「复制Q

复制容称CY)

P^ste

Delete

园跡有囲

ISdhJ;占曰心

选择元件圭寸装,点击鼠标右键选择复制。

打开需要将该封装存放的封装库,打开该库的“PCBlibrary”窗口,在组件栏中点击鼠

标右键,选择"Paste1Components”,将封装粘帖到该库中。

6•在“工具”一“注解”中可用定义原理图中所有元件的标号。

在左侧的“处理顺序”中可用设置元件顺序标号的方法,在右侧先点击“ResetAll”对所有元件标号复位,在点击

“更新更改列表”,最后点击“接收更改(创建ECC)”,在生成的新对话框中点击“执行更改”。

7•在元件的“元件属性”中,注释为如“ReS'(电阻)、“Res0.1%'(精密电阻)、“Cap”

(电容),设为"不可见”,在右侧的“Parameters'参数中增加“Value”,并在“值”中写入值的大小,将其设为“可见的”。

8.在“报告”一“Billofmaterials”中可以生成报目清单,在左上角的“聚合的纵队”中加入“Value”使类型相同而值不同的元件可以分组,加入的方法为将下方“全部纵队”中的“Value”拖入上方的“聚合的纵队”。

Ek«&I4

社臼怦6

iffftdil*-7wt&id■MSiwr-jWjJ

十IAMM

讯Ml电占舶弓细塾

:

tr昨轴出和ie

«?

•:

<叼•用更■

MPCBiasfl*

itteCD11BAG1

HesaIJiQA.

HesfefUFtiCueJE

HDRZS13_CB1h^arrISKZi".

|Wi

Cnwwrt*

FMfepvt*

工輒朝It■'

*cMtm2口■

Mwil

Ad«±wa4

Uiw

«'

OwdHdSv曲」Lb

M»JRT

GMb■一沁丿阳T&

Lnrwri*

C^PTfhirva

Drafm罰

Dnkrartinl

Emea*

CiMFMPW”DiflpF■日

■*Jpn

*15.

RmnrRI2Rll耳口

=1壮gr#

in

Zf⑧帧W.^K耳帥協址2!

■

tn

应*审佛砒册口3e聲誓

rii

FMdarRaR9HT!

HZFOHEA

+w

Cs4MCHQI.QLCMIMW

fhF

CoKirrCJ.U隽Cl.CllOSM

1hriX7

iF—・igDIFDIJ!

Ii17D1£SW

HQhCMbWIWMB7CHUW12H

2Jn^

zmwcwag.CTi™0151^

加

ancucu

2

匚严血C]€SC7«05血卑询B|

IftjH

Mjdv』

rwtrazzw

WwlCM4WiGWCI2

RI-VJ

2S^7OJF

FaauBZLapsla*.£14Clfi

AB-V3

ZUE

u.u

ir?

阿jnMfeF

MucwIJ

OHT^i

Midterbl

l«K3Z»M

PwW4Ci9-K4«Cl

fitt*

U2U3

rsgo™

DmIMD?

DWlFMl^g

SCv

MbdlFAM

GqxRoit

hldorhcMla-

咖6KKtZ-iM*¥lDR»X1fl

-uewZWSs^J*h—■550a

Hb*10An3丹扁亠3hiJI卫

I"4c42F1PJI

七务卜片LCwJEemWi-P*“J5-/>

他FOmw^J

DC1脚C«w»M.1

FtateFllklH-2hb^r1€X2to科#1臨HWJ年!

><■缶血Z创W加営EftW*CM海hht砂

9•在绘制原理图时,有时不使用系统默认的模版,而是自己自定义一个模版。

首先我们去除系统默认的模块,在原理图中点击鼠标右键,选择“选项”一“文档选项”,出现“文档选项”窗口,如下图所示:

在左边的“选项”卡中将“标题块”此项去除,点击“确定”版就被移除了。

在原理图中点击鼠标右键,选择“放置”一“绘图工具”一“线”效果如下图所示:

,此时原理图中原来的模

,绘制新模块界面,

在原理图中点击鼠标右键,选择“放置”一“文本框”

,将文本放置在适当的位置,在

鼠标移动的时候按下“TAB'键可以修改文字、字体等等参数,效果如下:

APPROVEDBY

日期DATE

序列号SERIALND

CHECKEDB¥

日朗

HATE

m.TITLE

-4

DESINEDBY

日期

的号

DRWNO

STAND.ULDLZEDBY

E期

DATE,

■'

KOFDRW

比例

\Tr

SHEBTNO

最后我们添加一张公司的logo,在原理图中点击鼠标右键,选择“放置”一“绘图工具”—“图像”,将图片放置在适当的位置,效果如下:

底:

宁星科技发展(探圳)有限公司

APPROVEDBY

启期

DATI-

序列号SERL-UNO

SF

CHECKEDBY

rsw

DATE

h

Mitt'.TITLE

询计

nE^INFUBY

日斟DATE

图号DRWNO

版本

标准It

^TANDARDfaDBY

日期

DATE

BIN

1LOFDRW

SCALE

誘⑪,我页

SHEETNQ.

模板绘制好后,点击“文件”一“保存为”,输入保存文件名“YX_LOG,并在保存

文件类型中选择原理图模板类型“AdvaneedSchematicTemplate(*.schdot)”,将模版保存。

点击“DXP'—“优先选项”,选择“Schematic-General”选项卡,在该选项卡中的右下角一栏“默认模版”中选择“YX_LO'点击“确定”保存为默认的模版,如下图所示:

10.PCB生成向导:

点击原理图界面的右下角“System”一“Files”,打开“Files”面板,

点击最下方的“从模板新建文件”中最下方的“PCBBoardWizard”。

11.PCB板四周常设置一个过孔,方便板子固定,它的位置可用更具四个顶点的坐标来确定,一般过孔的大小为4mm,中间通孔的大小为3mm,距离两边的最小距离为5mm。

设置好大小和位置后将“锁定”栏选上,防止将其移位。

12.PCB初步生成后,可以使用“交叉探针”快速寻找到原理图或PCB中对应的元

件。

13.网络咼亮显示:

“Ctrl”+“鼠标左键”点击某一条网络,可以是这个网络呈现咼亮,在右下角的“掩膜级别”中可以设置亮度反差。

14.布局时,AGND的网络应尽量各自在一起,与GND分开,AVCC的网络也尽量在AGND

网络范围中,以方便覆铜;各个电源和地线都应尽量加粗。

覆铜后可在GND覆铜区增加过

孔以增加上下各层GND网络的连接。

15滤波电容尽量靠近相应的元件;差分信号线尽量缩短,并且差分信号线之间的长度尽量相等;晶振线要粗,尽量靠近相应元件;

16.过孔直径大小一般为30mil,通孔大小为15mil,在画图中,可以使用快捷键“P—V”增加过孔,也可以在画某根线时,按住“Shift”+“Ctrl”不放,滑动鼠标滚轮自动添加过孔。

17.对于一些需要对齐的元件或丝印,将他们选中,点击鼠标右键,选择“对齐”,在右侧出现的菜单中选择对其方式。

CDR31

R22

P23

CDR32

CD口33

18.布好线后需要对整个电路板各层进行覆铜,覆铜前需要设置一下电气规则,点击“设

计”一“规则”,弹出PCB规则窗口,在左侧选择“Clearanee”,在右下方的“最小清除”中设置距离为30mil,等到覆铜结束后在将间距修改回来。

选择PCB的表层或者底层,点击覆铜按钮,在弹出的窗口中设置覆铜方法,在“填充模式”中选择“Hatched(Tracks/Arcs)”,在网络选项中“连接到网络”选择需要覆铜的网络,

如GND或者AGND,下面的一个下拉菜单选择中间的“PourOverAllSameNetObjects”,使

覆铜的网格与相同网络的连线直接相连而非十字相连,最后选上“死铜移除”,点击确定。

MatchedCTTicks/Anca?

:

NaneC'urtliresChlr:

眉芮EH

)£口lofCopperFt^iois

囲怛

桶桥尺寸7011

•IC.心能

ODODIDI

41

总小星店K圧

豪比也式•帧

7

3

MBtBMtaGhd

巧u「Qvsr耳Sam甘IMacObjacEfi

覆铜结束后若需要修改一些覆铜的规则且不需要改变覆铜的面积时,可以先将规则改好,

在删去覆铜,按“Ctrl+Z”取消删除,还原的覆铜会自动按新规则生成。

19.GND在覆铜后,可能会出现过孔是十字相连而非直接相连,如图:

十字相连

点击“设计”一“规则”,弹出PCB规则窗口,

Style”,如下图所示:

直接相连

在左侧选择“Plane”一“PolygonConnection

点击鼠标右键,选择“新规则”,在右侧选择“高级的(询问)”,点击“询问助手”,弹出"Queryhelper”窗口。

如下图所示:

在左下角的“Categories"窗口中选择“ObjectTypeChecks”,右下角的窗口中找到“IsVia”

选项双击,此时在上方的“Query”窗口中会出现“IsViaALL”,点击“确定”,返回规则设定

界面。

然后在“关联类型”下来菜单中选择"directconnect”。

一般DXP软件会默认将新建的规则优先权大于原先的规则,如果不是,我们可以手工

修改,使该过孔覆铜的规则优先于其它的覆铜规则,点击下方的“优先权”,出现“编辑规

则优先权”窗口,如下图所示:

选择“IsViaALL'项,点击下方的“增加优先权”,将IsViaALL”项的优先权设置为1,

默认为2。

20.完成PCB后,使用“工具”一“设计规则检查”,出现检测规则设置窗口,一般我

们使用默认即可,点击“运行DRC',进行电气规则检查,弹出错误信息窗口,若有错误

则会显示错误的信息。

Flessages

Oss3

DateN

Do亡umentSourceM«iage

ClearanceConstraint.BetweenPadC4D-112tXHJ.4&Gmil,42S5.54^irril}TopLayer.^ndPadC41

Time

■|

■YX-IULN-..Adva..QearanG&Gorstr^rit:

Track...18:

11:

232011/1..2

■IC...YXdULM*.Ajdva...ClearanceConstraint:

PadFt...1B:

11:

232011/1.,3

■1C...YX-IULM-...

」|C...YX-IULM-

■环YWULNL

■[CYXdULM-..

■YX-IULM-..

Adva...CearaneeCanstraint:

BetweenPadC...18:

11:

232011/1...4

Adva...CearanceCoristrarit:

BetweenTrack...1S:

11:

23B

Adva.n.ClearanceConstraint:

Traoklld18;11;23201171.^,5

Adva...QearanceCorstrant.Between卩edC..18:

11:

237

Ad如…OearaneeConstraint:

BetweenPadC...18:

111:

332011.'M...S

选中其中一条信息双击会自动跳转到如下图,对其点击鼠标右键,选择"冲突”如下图在“违规规则”中,我们可以看到“因为我们在规则中设置了"Clearanee”的

PCB出错的地方,出错的地方软件会显示出绿色,

—“显示所以冲突”,弹出“违规详情”对话框,

ClearaneeConstraint(Gap=30mil)”的信息,这是

“最小清除”为30mil,而该电阻的两个焊盘间距

却小于30mil,我们在规则中将“Clearanee”的“最小清除”改为10mil,在运行DRC检测发现该错误信息已经没有了。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- AltiumDesignerWinter09 通用 技巧 窍门

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《初级会计实务》试题题库大全及答案详解.docx

《初级会计实务》试题题库大全及答案详解.docx