静态时序分析StaticTimingAnalysis基础与应用.docx

静态时序分析StaticTimingAnalysis基础与应用.docx

- 文档编号:25303647

- 上传时间:2023-06-07

- 格式:DOCX

- 页数:22

- 大小:409.46KB

静态时序分析StaticTimingAnalysis基础与应用.docx

《静态时序分析StaticTimingAnalysis基础与应用.docx》由会员分享,可在线阅读,更多相关《静态时序分析StaticTimingAnalysis基础与应用.docx(22页珍藏版)》请在冰豆网上搜索。

静态时序分析StaticTimingAnalysis基础与应用

前言

在制程进入深次微米世代以后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。

此一趋势使得如何确保IC品质成为今日所有设计从业人员不能不面临之重大课题。

静态时序分析(StaticTimingAnalysis简称STA)经由完整的分析方式判定IC是不是能够在利用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。

但是,关于许多IC设计者而言,STA是个既熟悉却又陌生的名词。

本文将力求以简单表达及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?

STA的简单概念如下:

套用特定的时序模型(TimingModel),针对特定电路分析其是不是违背设计者给定的时序限制(TimingConstraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

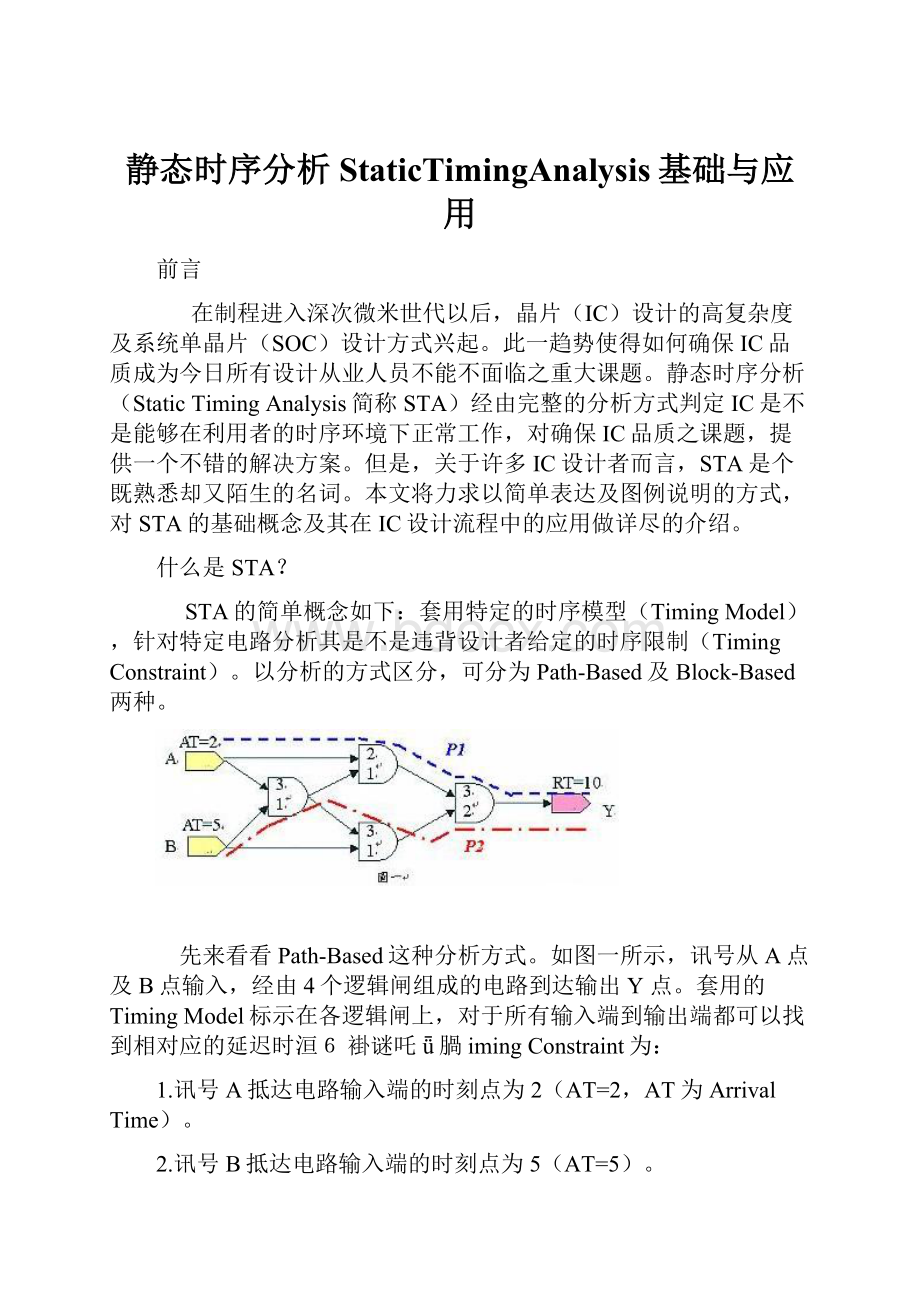

先来看看Path-Based这种分析方式。

如图一所示,讯号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。

套用的TimingModel标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时洹6褂谜吒ǖ腡imingConstraint为:

1.讯号A抵达电路输入端的时刻点为2(AT=2,AT为ArrivalTime)。

2.讯号B抵达电路输入端的时刻点为5(AT=5)。

3.讯号必需在时刻点10之前抵达输出端Y(RT=10,RT为RequiredTime)。

此刻咱们针对P1及P2两条途径(Path)来做分析。

P1的起始点为A,讯号抵达时刻点为2。

通过第1个逻辑闸以后,由于此闸有2单位的延迟时刻,因此讯号抵达此闸输出的时刻点为4(2+2)。

依此类推,讯号经由P1抵达输出Y的时刻点为7(2+2+3)。

在和上述第三项TimingConstraint比对以后,咱们能够得知对P1那个途径而言,时序(Timing)是知足利用者要求的。

依照一样的方式能够取得讯号经由途径B抵达输出Y的时刻点为11(5+1+3+2),照样和上述第三项TimingConstraint比对,咱们能够得知对P2那个途径而言,Timing是不知足利用者要求的。

对图一的设计而言,总共有6个讯号途径。

关于采纳Path-Based分析方式的STA软体来讲,它会对这6个讯号途径作一一的分析,然跋文录下结果。

IC设计者藉由检视其分析报告的方式来判定所设计的电路是不是符合给定的TimingConstraint。

由于最经常使用来做静态时序分析验证核可(STASignoff)的EDA软体PrimeTime?

采纳Path-Based的分析方式,因此本文将以Path-Based的分析方式介绍为主。

再来看看Block-Based的分析方式。

此不时序资讯(TimingInformation)的贮存再也不是以途径为单位,而是以电路节点(Node)为单位。

由TimingConstraint咱们仅能得知A节点的AT为2,B节点的AT为5和Y节点的RT为10。

Block-Based的分析方式会找出每一个节点的AT和RT,然后比对这两个数值。

当RT的值大于AT时表示讯号比TimingConstrain中要求的时刻还早抵达,如此那么Timing是知足的,反之那么不知足。

STA资料预备

在做STA之前,咱们必需对其预备工作有充分的了解。

STA所需的资料如图三所示,以下咱们分项说明。

其中DesignData部份,由于BlockModel和STA软体相关性太高,咱们不在此加以说明,请直接参阅您STA软体的利用手册。

图三

LibraryData:

STA所需要的TimingModel就寄存在标准元件库(CellLibrary)中。

这些必要的时序资讯是以TimingArc的方式呈此刻标准元件库中。

TimingArc概念逻辑闸任两个端点之间的时序关系,其种类有CombinationalTimingArc、SetupTimingArc、HoldTimingArc、EdgeTimingArc、PresetandClearTimingArc、RecoveryTimingArc、RemovalTimingArc、ThreeStateEnable&DisableTimingArc、WidthTimingArc。

其中第一、4、五、8项概念时序延迟,其他各项那么是概念时序检查。

图四

CombinationalTimingArc是最大体的TimingArc。

TimingArc若是不专门宣告的话,确实是属于此类。

如图四所示,他概念了从特定输入到特定输出(A到Z)的延迟时刻。

CombinationalTimingArc的Sense有三种,别离是inverting(或negativeunate),non-inverting(或positiveunate)和non-unate。

当TimingArc相关之特定输出(图四Z)讯号转变方向和特定输入(图四A)讯号转变方向相反(如输入由0变1,输出由1变0),那么此TimingArc为invertingsense。

反之,输出输入讯号转变方向一致的话,那么此TimingArc为non-invertingsense。

当特定输出无法由特定输入单独决按时,此TimingArc为non-unate。

图五

图六

图七

图八

图九

图十

图十一

图十二

其他的TimingArc说明如下。

∙ SetupTimingArc:

概念序向元件(SequentialCell,如Flip-Flop、Latch等)所需的SetupTime,依据Clock上升或下降分为2类(图五)。

∙ HoldTimingArc:

概念序向元件所需的HoldTime,依据Clock上升或下降分为2类(图六)。

∙ EdgeTimingArc:

概念序向元件ClockActiveEdge到资料输出的延迟时刻,依据Clock上升或下降分为2类(图七)。

∙ PresetandClearTimingArc:

概念序向元件清除讯号(Preset或Clear)发生后,资料被清除的速度,依据清除讯号上升或下降及是Preset或Clear分为4类(图八)。

那个TimingArc通常会被取消掉,因为它会造成讯号途径产生回路,这对STA而言是不许诺的。

∙ RecoveryTimingArc:

概念序向元件ClockActiveEdge之前,清除讯号不准启动的时刻,依据Clock上升或下降分为2类(图九)。

∙ RemovalTimingArc:

概念序向元件ClockActiveEdge以后,清除讯号不准启动的时刻,依据Clock上升或下降分为2类(图十)。

∙ ThreeStateEnable&DisableTimingArc:

概念Tri-State元件致能讯号(Enable)到输出的延迟时刻,依据Enable或Disable分为2类。

(图十一)

∙ WidthTimingArc:

概念讯号需维持稳固的最短时刻,依据讯号维持在0或1的位准分为2类。

(图十二)

上文列出了标准元件库内时序模型的项目,但对其量化的数据却没有加以说明。

接下来,咱们就来看看到底这些时序资讯的确实数值是如何概念在标准元件库中的。

以CombinationalTimingArc为例,讯号从输入到输出的延迟时刻能够描述成以输入的转换时刻(TransitionTime)和输出的负载为变数的函数。

描述的方式能够是线性的方式,如图十三所示。

也能够将这2个变数当做指标,成立时序表格(TimingTable),让STA软体能够查询出正确的延迟时刻。

这种以表格描述的方式会比上述线性描述的方式准确许多,因此现今市面上大部份的标准元件库皆采纳产生时序表格的方式来成立TimingModel。

图十三

咱们举个简单的例子来讲明STA软体如何从时序表格计算出元件延迟时刻。

(图十四)

图十四

∙ 元件延迟时刻(Ddelay):

输入达逻辑1位准50%到输出达逻辑1位准50%的时刻。

∙ 元件转换时刻(Dtransition):

输出达逻辑1位准20%(80%)到80%(20%)的时刻。

∙

当输入的转换时刻为,输出负载为时,可由图十四的时序表格查得元件I2的延迟时刻为。

而由于表格的大小有限,关于无法直接由表格查询到的延迟时刻(如输入转换时刻,输出负载),STA软体会利用线性内插或外插的方式计算延迟时刻。

关于其他的TimingArc,不管是时序延迟或时序检查,其相对应的时序数值计算和上例的计算方式是一样的。

接下来咱们说明操作环境(OperatingCondition)对时序的阻碍。

操作环境指的是制程(Process)、电压(Voltage)、温度(Temperature)三项因子。

这三项因子通常会被简称为PVT,其对时序的阻碍可用下方线性方程式来描述。

其中nom_process、nom_voltage及nom_temperature会概念在标准元件库中,代表成立时序表格时的操作环境。

InterconnectData:

在「什么是STA」段落的例子中,为了方便说明,咱们并无把逻辑闸和逻辑闸间的连线延迟(InterconnectDelay)考虑在内。

事实上,许多DSMIC设计之时序表现是由连线延迟主导的,其重要性不容咱们轻忽。

连线延迟依照布局与绕线(P&R)前后有不同的考量。

在布局与绕线前,元件在晶片中摆放的位置尚未确信,因此连线延迟是一个预估值。

而在布局与绕线以后,连线延迟那么是依如实际绕线计算出来的。

对布局与绕线之前的连线延迟,一般是用WireloadModel来预估。

WireloadModel依照晶片面积的预估大小及连线驱动元件数量(Fan-out)的多寡来决定连线的电阻和电容值,STA软体那么利用这些电阻电容值计算出连线延迟。

在布局与绕线以后,能够利用电阻电容萃取(RCExtraction)软体将绕线图形转换成实际的电阻电容电路,然后贴回(Back-annotate)STA软体计算连线延迟。

TimingConstraints:

TimingConstraint为利用者所给定,用来查验设计电路时序的准那么。

其中最重要的一项确实是时脉(Clock)的描述。

关于一个同步电路而言,暂存器和暂存器之间的途径延迟时刻必需小于一个Clock周期(Period),也确实是说,当咱们确认了Clock规格,所有暂存器间的途径的TimingConstraint就会自动给定了。

图十五

Clock规格包括波形、Latency及Uncertainty的概念。

波形概念一个Clock的周期及讯号上升缘及下降缘的时刻点。

Latency概念从Clock来源到序向元件Clock输入端的延迟时刻。

Uncertainty那么概念Clock讯号到序向元件Clock输入端可能早到或晚到的时刻。

若是上面的文字让你有不知所云的感觉,那底下看图说故事的讲解或许会让你有比较清楚的概念。

在图十五的电路中,左侧的正反器(Flip-Flop)在第一个Clock上升缘时会丢出资料,此资料会在第二个Clock上升缘让右边的Flip-Flop撷取。

要分析右边的Flip-Flop可否正确撷取资料就必需明白第一个Clock上升缘抵达节点C1的时刻点和第二个上升缘抵达节点C2的时刻点。

假设在时刻点为0的时候,Clock讯号由S点动身,通过一段时刻(sourcelatency,1个时刻单位,模拟晶片外的Clock延迟时刻,例如板子上的绕线产生的讯号延迟时刻)抵达电路的Clock输入端点P,接下来再通过一段时刻(晶片内Clock绕线造成的讯号延迟时刻),Clock讯号别离抵达C1和C2节点。

若是电路已经进行布局与绕线,输入端点P到C1和C2的讯号延迟时刻可由连线上的寄生电阻电容计算得来。

例如说,通过计算发觉讯号由P传递到C1需要1个时刻单位,由P传递到C2需2个时刻单位,那么Clock讯号第一个上升缘抵达C1和第二个上升缘抵达C2的时刻点就会如图十六下方两列所示,别离为时刻点2和13(因为加上了1个时刻单位的sourcelatency)。

图十六

在布局与绕线之前,咱们无法准确得知P到C1和C2的讯号延迟时刻,仅能先做个预估。

图十五的networklatency及上文提到的Uncertainty确实是用来做此种预估的。

先假设咱们拥有某种完美的布局与绕线软体能够让Clock输入端点P到所有Flip-Flop的Clock输入端的讯号延迟时刻一模一样,那么咱们只要明白那个讯号延迟时刻就能够够取得Clock讯号抵达C1和C2的时刻点了。

那个讯号延迟时刻能够藉由电路特性(如预估面积大小,Flip-Flop数量等)来做预估,而那个预估值确实是所谓的networklatency。

若是这种完美的软体存在的话,那Clock的上升缘抵达C1和C2的时刻点就能够够由Latency(sourcelatency+networklatency)计算出来。

很不幸的,世界上没有这么完美的软体,在布局与绕线后Clock输入端点P到所有Flip-Flop的Clock输入端的讯号延迟时刻可不能完全一样。

也确实是说Clock的某个上升缘可不能同时抵达C1和C2。

因此咱们要对上述的预估值做些修正,加入Uncertainty的描述来概念Clock上升缘左右移动的可能范围。

在图十六中,Uncertainty为1个时刻单位,因此Clock第一个上升缘会在时刻点3(因为Latency为3)左右1时刻单位范围内(也确实是时刻点2到时刻点4)抵达C1,。

第二个上升缘那么会在时刻点12到14的范围内抵达C2。

除Clock之外,关于电路其他输出输入端点及其周边的环境(BoundaryCondition)也要加以描述。

在说明BoundaryCondition之前,咱们得对途径(Path)有更进一步的了解。

上文曾提及STA会将电路中所有的Path找出来加以分析,但Path的概念是什么呢?

Path依照起点及终点能够分为4种:

1.由Flip-FlopClock输入到Flip-Flop资料输入(图十七左上)。

2.由要紧输入(PrimaryInput,简称PI)到Flip-Flop资料输入(图十七右上)。

3.由Flip-FlopClock输入到要紧输出(PrimaryOutput,简称PO)(图十七左下)。

4. 由要紧输入到要紧输出(图十七右下)。

当Clock规格确信了以后,第1种Path的时序限制(TimingConstraint)就自动的给定了。

为了给定其他3种Path的时序限制,咱们必需概念BoundaryCondition。

一般来说,我们会定义下列的BoundaryCondition:

1.DrivingCell:

概念输入端点的推动能力(图十八)。

2.InputTransitionTime:

概念输入端点的转换时刻(图十八)。

3.OutputCapacitanceLoad:

概念输出负载(图十八)。

4.InputDelay:

输入端点相关于某个Clock领域的延迟时刻。

(图十九,Delayclk-Q+a)

5.OutputDelay:

自输出端点往外看相关于某个Clock领域的延迟时刻。

(图十九,c)

在这些BoundaryCondition概念以后,上述4种Path事实上都可看成是第1种Path(Flip-Flop到Flip-Flop)。

也确实是说,加上BoundaryCondition后,只要Clock给定,所有Path的TimingConstraint就会自动给定。

。

图十八

图十九

由于每一个Path都有TimingConstraint,因现在序分析都能够进行。

但在某些情形下,有些Path的分析可能没成心义,因此你会想忽略这些Path的分析。

或是有些Path分析的方式不一样,你会想指定这些Path的分析方式。

现在就要设定一些TimingException,如FalsePath和Multi-cyclePath等等来处置非一样性的时序分析。

STA流程及分析方式

STA的流程如图二十所示,而其分析验证的项目确实是咱们前文提及之时序检查相关的TimingArc,如SetupTime、HoldTime等等。

以下咱们针对SetupTime举1实际范例来讲明STA的分析方式。

图二十

SetupTime

设计电路如图二十一所示,时序模型(TimingModel)及时序限制(TimingConstraint)如下:

图二十一

∙ 所有逻辑闸在输出讯号上升时最长的延迟时刻为3ns,最短为2ns。

∙所有逻辑闸在输出讯号上升时最长的延迟时刻为2ns,最短为1ns。

∙所有连线(Net)最长的延迟时刻为2ns,最短为1ns。

∙所有Flip-FlopClock到Q的延迟时刻为3ns。

∙所有Flip-Flop的SetupTime为1ns(Ts)。

∙所有Flip-Flop的HoldTime为1ns(Th)。

∙Clock周期为14ns(Dclkp)。

∙Clocksourcelatency为2ns(Dclks)。

∙Clocknetworklatency为3ns(Dclkn)。

∙Clockuncertainty为1ns(Dclku)。

∙B及C的inputdelay皆为1ns(Da、Db、Dc)。

∙Y的outputdelay为3ns(DY)。

接下来,咱们以Step-By-Step的方式说明时序分析的方式。

1. 第一找出所有TimingPath,咱们只列出具代表性的3条TimingPath来加以说明。

图二十二

2. 假设输入A讯号由0变1,计算第1条Path终点讯号抵达的时刻(ArrivalTime简称AT)。

3. 假设输入A讯号由1变0,计算第1条Path终点AT。

图二十四

4. 计算第1条Path终点的需求时刻(RequiredTime,简称RT)。

图二十五

5. 假设输入A讯号由0变1,计算第1条Path终点的Slack。

Slack等于RT和AT的差值,关于SetupTime验证来讲等于RT-AT,关于HoldTime验证来讲等于AT-RT。

在此SetupTime范例中,Slack为正,表示讯号实际抵达Path终点时刻比必需抵达的时刻还早,因此Timing是知足的。

图二十六

6. 假设输入A讯号由1变0,计算第1条Path终点的Slack。

Slack为正,因此Timing是知足的。

综合5和6,第1条Path的Timing是符合规格的,其Slack为4ns(取较差状况)。

图二十七

7. 假设前级Flip-Flop的讯号由0变1,计算第2条Path终点的AT。

图二十八

8. 假设前级Flip-Flop的讯号由1变0,计算第2条Path终点的AT。

图二十九

9. 计算第2条Path终点的RT

图三十

10. 假设前级Flip-Flop的讯号由0变1,计算第2条Path终点的Slack。

Slack为负,因此Timing不知足。

图三十一

11. 假设前级Flip-Flop的讯号由1变0,计算第2鮌ath终点的Slack。

Slack为负,因此Timing不知足。

综合10和11,第2条Path的Timing不知足,其Slack为-3。

图三十二

12. 假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的AT。

图三十三

13. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的AT。

图三十四

14. 计算第3条Path终点的RT。

图三十五

15. 假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的Slack。

Slack为负,因此Timing不知足。

图三十六

16. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的Slack。

Slack为负,因此Timing不知足。

综合15和16,第3条PathTiming不符合规格,其Slack为-4。

图三十七

综合上述分析结果,此电路的时序不符合规格,其CriticalPath是Path3,Slack为-4。

总结

本文先对STA的概念做概念性的介绍,在下集的文章中,将对STA在实际IC设计流程中的应用举一范例说明,请列位拭目以待。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 静态 时序 分析 StaticTimingAnalysis 基础 应用

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《爱和自由》读书心得15篇.docx

《爱和自由》读书心得15篇.docx