DCT.docx

DCT.docx

- 文档编号:25192031

- 上传时间:2023-06-06

- 格式:DOCX

- 页数:14

- 大小:30.08KB

DCT.docx

《DCT.docx》由会员分享,可在线阅读,更多相关《DCT.docx(14页珍藏版)》请在冰豆网上搜索。

DCT

一.测试目的

利用FPGA对dct4x4模块进行验证,为以后的整个图像组的模块进行FPGA验证提供可能。

二.功能说明

dct4x4模块主要完成的功能是:

输入一个4x4矩阵X,然后对X进行左右乘矩阵

具体实现是先取X的两行并行先进行行变换(就是先右乘矩阵),然后X的剩下两行在进行行变换。

全部行变换完后,在取行变换完后的矩阵的前两列,并行进行列变换,然后取剩下两列并行进行列变换。

这采用的是半流水结构,所以最后输出要两拍,第一拍输出前两列,第二拍输出后两列。

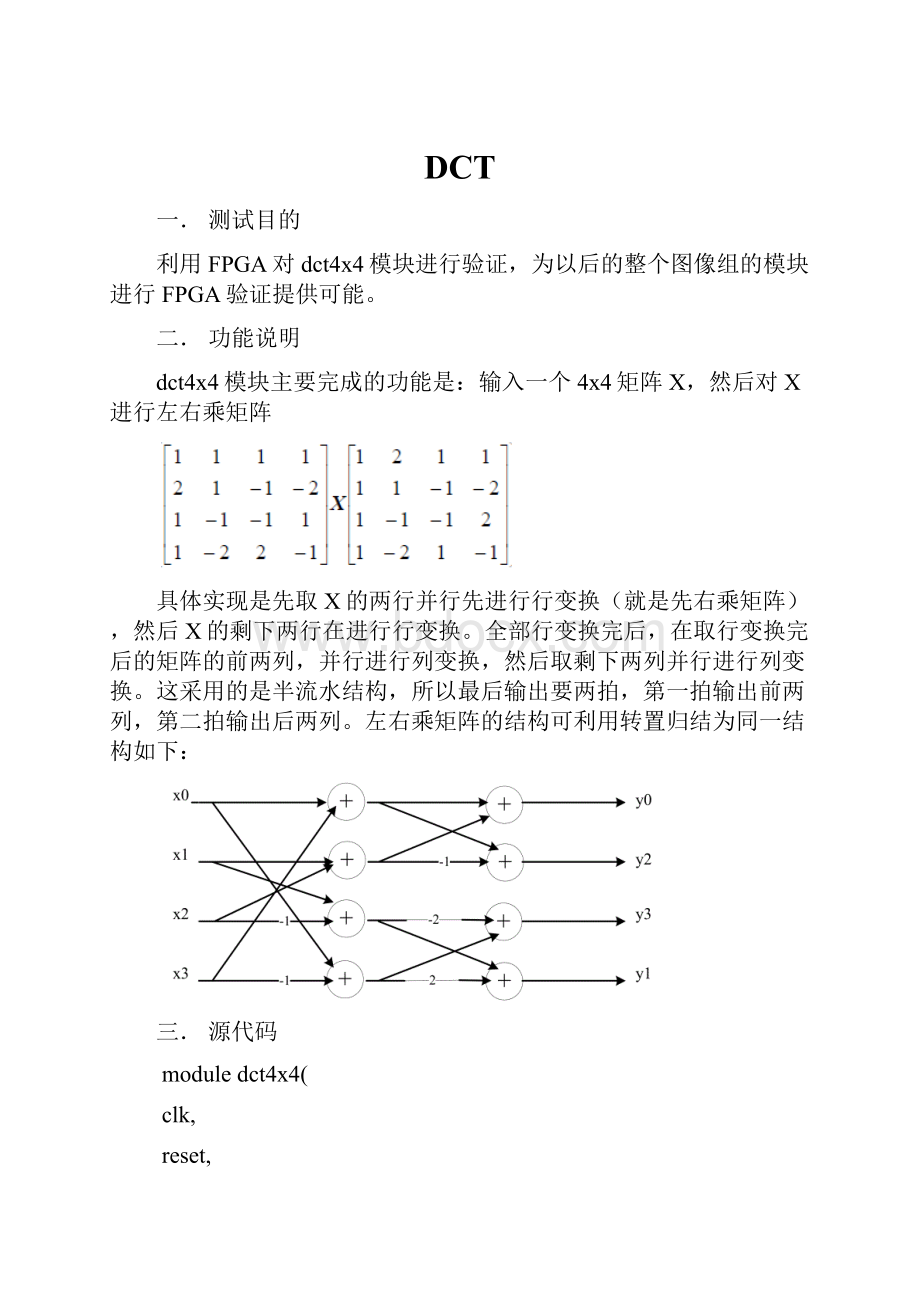

左右乘矩阵的结构可利用转置归结为同一结构如下:

三.源代码

moduledct4x4(

clk,

reset,

end_MV,

twoD_0,

twoD_1,

twoD_2,

twoD_3,

twoD_4,

twoD_5,

twoD_6,

twoD_7,

dif_0,

dif_1,

dif_2,

dif_3,

dif_4,

dif_5,

dif_6,

dif_7,

dif_8,

dif_9,

dif_10,

dif_11,

dif_12,

dif_13,

dif_14,

dif_15,

en_out

);

input[8:

0]dif_0,dif_1,dif_2,dif_3,dif_4,dif_5,dif_6,dif_7,

dif_8,dif_9,dif_10,dif_11,dif_12,dif_13,dif_14,dif_15;

inputclk,reset;

inputend_MV;

output[14:

0]twoD_0,twoD_1,twoD_2,twoD_3,twoD_4,twoD_5,twoD_6,twoD_7;

outputen_out;

regen_out;

reg[14:

0]twoD_0,twoD_1,twoD_2,twoD_3,twoD_4,twoD_5,twoD_6,twoD_7;

reg[14:

0]oneD_0,oneD_1,oneD_2,oneD_3,oneD_4,oneD_5,oneD_6,oneD_7,

oneD_8,oneD_9,oneD_10,oneD_11,oneD_12,oneD_13,oneD_14,oneD_15;

reg[14:

0]dif0,dif1,dif2,dif3,dif4,dif5,dif6,dif7;

wire[14:

0]oneD0,oneD1,oneD2,oneD3,oneD4,oneD5,oneD6,oneD7;

reg[1:

0]oneD_count;

reg[2:

0]twoD_count;

wireen_wire;

assignen_wire=(twoD_count==3'd3|twoD_count==3'd2)?

1'b1:

1'b0;

always@(posedgeclk)begin

if(!

reset)begin

en_out<=0;

endelsebegin

en_out<=en_wire;

end

end

//====================================================

wireoneD_en;

assignoneD_en=(end_MV==1)||(oneD_count!

=0);

always@(posedgeclk)

if(!

reset)

oneD_count<=0;

elseif(oneD_en)

oneD_count<=(oneD_count==0)?

2'b11:

oneD_count-1;

//=====================================================

wiretwoD_en;

assigntwoD_en=((oneD_count==2'b01)||(twoD_count!

=0));

always@(posedgeclk)

if(!

reset)

twoD_count<=0;

elseif(twoD_en)

twoD_count<=(twoD_count==0)?

3'b100:

twoD_count-1;

//==============================================

dct4dct4_1(.clk(clk),.reset(reset),.D0(dif0),.D1(dif1),.D2(dif2),.D3(dif3),

.F0(oneD0),.F1(oneD1),.F2(oneD2),.F3(oneD3));

dct4dct4_2(.clk(clk),.reset(reset),.D0(dif4),.D1(dif5),.D2(dif6),.D3(dif7),

.F0(oneD4),.F1(oneD5),.F2(oneD6),.F3(oneD7));

//===============

always@(oneD_countortwoD_count

ordif_0ordif_1ordif_2ordif_3ordif_4ordif_5ordif_6ordif_7

ordif_8ordif_9ordif_10ordif_11ordif_12ordif_13ordif_14ordif_15

oroneD_0oroneD_1oroneD_2oroneD_3oroneD_4oroneD_5oroneD_6oroneD_7

oroneD_8oroneD_9oroneD_10oroneD_11oroneD_12oroneD_13oroneD_14oroneD_15)

if(oneD_count!

=0)

case(oneD_count)

2'b11:

begin

dif0={dif_0[8],dif_0[8],dif_0[8],dif_0[8],dif_0[8],dif_0[8],dif_0};

dif1={dif_1[8],dif_1[8],dif_1[8],dif_1[8],dif_1[8],dif_1[8],dif_1};

dif2={dif_2[8],dif_2[8],dif_2[8],dif_2[8],dif_2[8],dif_2[8],dif_2};

dif3={dif_3[8],dif_3[8],dif_3[8],dif_3[8],dif_3[8],dif_3[8],dif_3};

dif4={dif_4[8],dif_4[8],dif_4[8],dif_4[8],dif_4[8],dif_4[8],dif_4};

dif5={dif_5[8],dif_5[8],dif_5[8],dif_5[8],dif_5[8],dif_5[8],dif_5};

dif6={dif_6[8],dif_6[8],dif_6[8],dif_6[8],dif_6[8],dif_6[8],dif_6};

dif7={dif_7[8],dif_7[8],dif_7[8],dif_7[8],dif_7[8],dif_7[8],dif_7};

end

2'b10:

begin

dif0={dif_8[8],dif_8[8],dif_8[8],dif_8[8],dif_8[8],dif_8[8],dif_8};

dif1={dif_9[8],dif_9[8],dif_9[8],dif_9[8],dif_9[8],dif_9[8],dif_9};

dif2={dif_10[8],dif_10[8],dif_10[8],dif_10[8],dif_10[8],dif_10[8],dif_10};

dif3={dif_11[8],dif_11[8],dif_11[8],dif_11[8],dif_11[8],dif_11[8],dif_11};

dif4={dif_12[8],dif_12[8],dif_12[8],dif_12[8],dif_12[8],dif_12[8],dif_12};

dif5={dif_13[8],dif_13[8],dif_13[8],dif_13[8],dif_13[8],dif_13[8],dif_13};

dif6={dif_14[8],dif_14[8],dif_14[8],dif_14[8],dif_14[8],dif_14[8],dif_14};

dif7={dif_15[8],dif_15[8],dif_15[8],dif_15[8],dif_15[8],dif_15[8],dif_15};

end

default:

begin

dif0=0;dif1=0;dif2=0;dif3=0;

dif4=0;dif5=0;dif6=0;dif7=0;

end

endcase

elseif(twoD_count!

=0)

case(twoD_count)

3'b100:

begin

dif0=oneD_0;dif1=oneD_4;dif2=oneD_8;dif3=oneD_12;

dif4=oneD_1;dif5=oneD_5;dif6=oneD_9;dif7=oneD_13;

end

3'b011:

begin

dif0=oneD_2;dif1=oneD_6;dif2=oneD_10;dif3=oneD_14;

dif4=oneD_3;dif5=oneD_7;dif6=oneD_11;dif7=oneD_15;

end

default:

begin

dif0=0;dif1=0;dif2=0;dif3=0;

dif4=0;dif5=0;dif6=0;dif7=0;

end

endcase

else

begin

dif0=0;dif1=0;dif2=0;dif3=0;

dif4=0;dif5=0;dif6=0;dif7=0;

end

//========================

always@(posedgeclk)

if(!

reset)

begin

oneD_0<=0;oneD_1<=0;oneD_2<=0;oneD_3<=0;

oneD_4<=0;oneD_5<=0;oneD_6<=0;oneD_7<=0;

oneD_8<=0;oneD_9<=0;oneD_10<=0;oneD_11<=0;

oneD_12<=0;oneD_13<=0;oneD_14<=0;oneD_15<=0;

end

elseif(oneD_en&&oneD_count!

=0)

case(oneD_count)

2'b10:

begin

oneD_0<=oneD0;oneD_1<=oneD1;oneD_2<=oneD2;oneD_3<=oneD3;

oneD_4<=oneD4;oneD_5<=oneD5;oneD_6<=oneD6;oneD_7<=oneD7;

end

2'b01:

begin

oneD_8<=oneD0;oneD_9<=oneD1;oneD_10<=oneD2;oneD_11<=oneD3;

oneD_12<=oneD4;oneD_13<=oneD5;oneD_14<=oneD6;oneD_15<=oneD7;

end

default:

begin

oneD_0<=0;oneD_1<=0;oneD_2<=0;oneD_3<=0;

oneD_4<=0;oneD_5<=0;oneD_6<=0;oneD_7<=0;

oneD_8<=0;oneD_9<=0;oneD_10<=0;oneD_11<=0;

oneD_12<=0;oneD_13<=0;oneD_14<=0;oneD_15<=0;

end

endcase

//========================

always@(posedgeclk)

if(!

reset)

begin

twoD_0<=0;twoD_1<=0;twoD_2<=0;twoD_3<=0;

twoD_4<=0;twoD_5<=0;twoD_6<=0;twoD_7<=0;

end

elseif(twoD_en&&twoD_count!

=0)

begin

twoD_0<=oneD0;twoD_1<=oneD1;twoD_2<=oneD2;twoD_3<=oneD3;

twoD_4<=oneD4;twoD_5<=oneD5;twoD_6<=oneD6;twoD_7<=oneD7;

end

endmodule

moduledct4(clk,reset,D0,D1,D2,D3,F0,F1,F2,F3);

inputclk,reset;

input[14:

0]D0,D1,D2,D3;

output[14:

0]F0,F1,F2,F3;

reg[14:

0]m0_reg,m1_reg,m2_reg,m3_reg;

wire[14:

0]m0,m1,m2,m3;

assignm0=D0+D3;

assignm1=D1+D2;

assignm2=D1-D2;

assignm3=D0-D3;

always@(posedgeclk)

if(!

reset)

begin

m0_reg<=0;m1_reg<=0;m2_reg<=0;m3_reg<=0;

end

else

begin

m0_reg<=m0;m1_reg<=m1;m2_reg<=m2;m3_reg<=m3;

end

assignF0=m0_reg+m1_reg;

assignF1=m2_reg+{m3_reg[13:

0],1'b0};

assignF2=m0_reg-m1_reg;

assignF3=m3_reg-{m2_reg[13:

0],1'b0};

endmodule

四.测试

第一组:

1输入:

-8588126121

-79706583

-80664943

-82869741

输出:

609-1255-685-560

277-476113-73

175-159-11998

-14-1341

2输入9121211

19-44-24

26214-35

132534-4

输出114209-84177

-60-90112-100

110-167-24-111

035615

3输入-11-34-1716

-21-89-5214

-23-100-3152

-27-93-660

输出-362-658482196

-6492-178-184

138-6-106-8

112-34-24-32

4输入304533-3

22277-3

-3-236

181111

输出193102-71-9

197295-10510

798-4519

-24-85-1045

第二组:

1输入-4-3-1-1

2925466

5660344

3843120

输出37112785-204

-243-3646173

-20371-121158

-24153-42-21

2输入-1-1-1-2

-47-42-37-62

-41-7-6-48

73025-10

输出-24379-16542

-200-621604

337347-26

115-61-35-38

3输入71365

1722

0-3-7-8

0-1-2-3

输出1941-11-22

104-9-22-37

31-5-30

-233899

4输入1-2-3-17

0-2-3-3

-7-7-7-7

-2-2-10

输出-6239-817

-1291-2233

1025-1215

-5628-1614

第三组:

1输入31-27

76-110

76-111

6509

输出74-646-58

-23-617

-16-6-412

-9-831

2输入2111

-1011

001-1

-2-3-2-2

输出-3-3-16

2901-5

-5550

1215-25

3输入-24-10

-2527

-19-7-32

-1-5-51-79

输出-154266-66-42

317-49571-10

-1161408-10

51-15-4730

4输入0122038

15122228

-3-15-11-12

-19-13-34

输出67-18-5-9

336-39472-32

-526-45-57

-127-72419

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- DCT

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《初级会计实务》试题题库大全及答案详解.docx

《初级会计实务》试题题库大全及答案详解.docx