MOS结构CV特性测量及BT试验.docx

MOS结构CV特性测量及BT试验.docx

- 文档编号:25107739

- 上传时间:2023-06-05

- 格式:DOCX

- 页数:8

- 大小:84.84KB

MOS结构CV特性测量及BT试验.docx

《MOS结构CV特性测量及BT试验.docx》由会员分享,可在线阅读,更多相关《MOS结构CV特性测量及BT试验.docx(8页珍藏版)》请在冰豆网上搜索。

MOS结构CV特性测量及BT试验

实验四MOS结构C-V特性测量及BT实验

1.实验目的与意义

对MOS结构测量其高频电压-电容(C-V)曲线,以及利用正、负偏压温度处理方法(简称土BT试验)进行Si/SiO:

界而研究,可以获得MOS结构的多个参数:

二氧化硅层的厚度,衬底硅掺杂类型、浓度,以及二氧化硅层中可动电荷与固定电荷密度。

通过实验全过程的操作及数据处理,使学生加深对所学“固态电子论”中半导体表面理论的理解,特別是硅-二氧化硅系统性质的理解。

掌握用C-V方法测量MOS结构样品的多个参数。

2.实验原理

3.

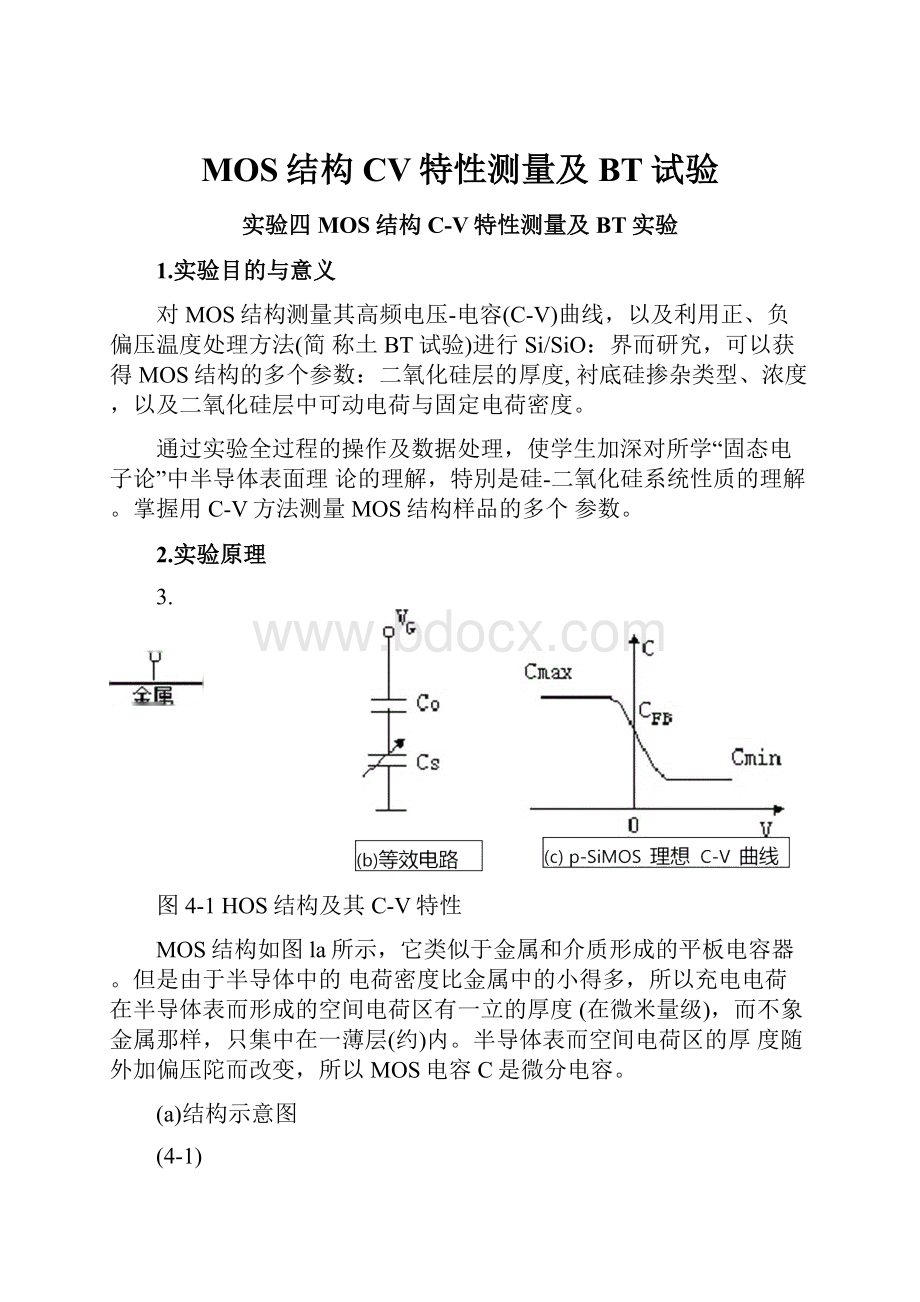

图4-1HOS结构及其C-V特性

MOS结构如图la所示,它类似于金属和介质形成的平板电容器。

但是由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表而形成的空间电荷区有一立的厚度(在微米量级),而不象金属那样,只集中在一薄层(约)内。

半导体表而空间电荷区的厚度随外加偏压陀而改变,所以MOS电容C是微分电容。

(a)结构示意图

(4-1)

式中:

Q是金属电极上的电荷而密度;月是电极而积。

理想情形可假设MOS结构满足下列条件:

①金属-半导体间的功函数差为零:

②SiO:

层中没有电荷:

③SiO:

与半导体界面处不存在界而态。

偏压冷一部分降在SiO:

上,记为仏:

一部分降在半导体表面空间电荷区,记为仏,即:

VG=Vo+Vs(4-2)

%又称为表面势。

考虑到半导体空间电荷区电荷和金属电极上的电荷数量相等、符号

相反,有:

|e.J=|eG|(4-3)

式中:

0S为半导体表面空间电荷区电荷面密度。

将(4-2)、(4-3)代入(4-1)式,有:

C=A^=A

dQG

(4-4)

式(4-4)表明MOS电容是©和Cs串联而成,其等效电路为图4-1的b所示。

其中8是以SiO:

为介质的氧化层电容,它的数值不随%改变,Cs是半导体表而空间电荷区电容,其数值随%改变。

因此,有:

(4-5)

(4-6)

式中:

f戸1(TF/id、分别为真空介电常数和二氧化硅相对介电常数。

由式(4-6)看,Qs的大小主要由空间电荷区单位而积电量0s随表而势7s的变化而定。

P型硅的理想MOS结构髙频C-V特性曲线如图1的c所示,V轴表示外加偏压,C轴是电容值©最大电容Cmax^Co.最小电容d乃和最大电容之间有如下关系:

1

\+丄严吟KT居

氐心q・Nn;

式中:

再为Si衬底参杂浓度:

〜戸l(TF/n),为半导体的相对介电常数:

KT(室温)=:

q二*1(TC,为电子荷电;nR10%in',为Si本征载流子浓度。

当母0时,半导体表面能带平直,称为平带。

平带时,对应的偏压称为平带电压,记为Vno显然,对于理想MOS结构,耳尸0。

此时,对应的电容称为平带电容,记为g对于给左的MOS结构,归一化平带电容有如下关系:

(4-8)

考虑实际的HOS结构,由于SiO:

中总是存在电荷(通常都为正电荷),且金属-半导体接触的功函数并不相等,两者功函数差记为入。

因此,仏也不为零。

若不考虑界而态,有下式:

(4-9)

图4-2铝柵P-SiMOS结构C-V特性

对于铝栅P-SiMOS结构,怡大于零,G也大于0(正电荷),所以V„ 利用正、负偏压温度处理方法(简称土BT处理),可将氧化层中可动电荷和固泄电荷区分开。 -BT处理是给样品加一眾的负偏压(即%<0),同时将样品加热到一泄温度,由于可动电荷(主要为钠离子)在高温下有较大的迁移率,在负偏压下将向Al/SiO=界而运动;然后,保持偏压不变,将样品自然冷却到室温: 最后,去掉偏压,测C-V特性,得到图2中的曲线2。 此时,可动电荷都迁移到Al/SiO=界而处,对平带电压没有影响,由式(4-9)可得: (4-10) 式中: Q是固龙电荷而密度。 若仏已知,则可确泄二氧化硅中固龙电荷而密度: 血(4-12) 改变偏压极性,作+BT处理,加热时间和-BT相同。 与-BT同样测量C-V特性,将得到图2中的曲线3。 由于这时可动电荷基本上都移到Si/SiO=界而附近。 所以沧中包含有固左电荷和可动电荷的影响。 可动电荷而密度为Q,有: V顷"怦-性-匕尸性+f(4-14) 令△匕力=|"皿2一匕血|,并由(4-14)式可得可动电荷面密度: cAV 0=(4-⑸ 4.实验内容 采用髙频CW测试方法,以及正、负偏温(士BT)实验,测量MOS结构的CW特性曲线;并通过数值汁算得到MOS结构样品的多个特性参数: 衬底硅掺杂类型、浓度,二氧化硅层的厚度,以及二氧化硅层中可动电荷与固泄电荷的而密度。 5.实验仪器与样品 哈尔滨工业大学研制的髙频C-V特性测试仪,计算机控制系统,打印机,【-具有偏压、加热控温装置的多功能探针台,显微镜。 高频C-V特性测试系统如图4-3所示。 计算机控制输出 图4-3髙频C-V特性测试系统示意图 巾卩匸 [to热控温装置 样品u ——w口载偏压装蓋 家功能探针台U 」朮冷却装置1 高频C■嘴性测试仪输入输岀 QQQ 另有MOS结构芯片样品若干片。 6.实验步骤 (-)C-V测试 准备如图4-4所示,连接探针台、C-V特性测试仪及计算机。 开计算机进入C-V测试状态。 测量将样片放在探针台上接好,进行测试,打印测试结果: 在显微镜下测量被测MOS结构A1电极直径。 7.数据处理 1.截图及近似图 A1圆片直径为2mm° 2.由QW曲线1确立MOS结构芯片村底掺杂类型。 利用公式(4-5)和(4-7)讣算二氧化硅层厚度&,及衬底掺杂浓度M利用公式(4-8)汁算平带电容為: 由平带电容得到平带电压Vno利用公式(4-9)计算二氧化硅层中正电荷而密度 D.MOS结构芯片衬底掺杂类型为N型 Co=A£{}£r[},^0=F/m、%二,A=2• 由图像得Cmax=200pF,Cmin=50pF; ~cT 掺杂™35)Z(寻7警A盏矿 估算可得N二cmS 8.讨论丿 所测曲线及数据与理论是否相符,如不相符分析原因 1激励正压不断增加,电容没有岀现最大值,而是持续增加。 原因: 半导体表而态处于非平衡深耗尽状态,由于空间电荷区少子产生速度没有电压变化快,反型层来不及建立,为满足电中性条件,耗尽层延伸到半导体深处,产生大量电荷,由于电容和空间电荷区深度成反比,所以电容可以一直增加。 2图像比理论图像靠左。 原因: SiO2绝缘层里存在电荷,产生电场,影响了空间电荷区的分布: 实验中其他存在误差的地方: 管里半导体不均匀,会有其他杂质造成影响: 2.由于MOS管通过导电底板与测量端相连,底板的电容特性会影响到实验结果;3。 测量仪器内部产生的误差。 9.实验思考与总结 通过实验,加深了对半导体表而理论的理解,特別是硅-二氧化硅系统性质,初步了解 了使用C-V方法测量MOS结构样品的多个参数。 改进意见: 1.更换仪器直流模块可以提高仪器直流特性,保持数据的稳左性。 也可以不 更换,但是需要测量每个数据阶段的直流偏移量,然后在实际数据的基础上去掉直流偏移量: 2.选择均匀的样品进行测量,在正式测量前可以先测各个样品的均匀度,选择其中最好的一个进行实验。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- MOS 结构 CV 特性 测量 BT 试验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《爱和自由》读书心得15篇.docx

《爱和自由》读书心得15篇.docx