F2812DSP的最小系统设计.doc

F2812DSP的最小系统设计.doc

- 文档编号:2486781

- 上传时间:2022-10-30

- 格式:DOC

- 页数:7

- 大小:88.11KB

F2812DSP的最小系统设计.doc

《F2812DSP的最小系统设计.doc》由会员分享,可在线阅读,更多相关《F2812DSP的最小系统设计.doc(7页珍藏版)》请在冰豆网上搜索。

F2812DSP的最小系统设计

摘要:

本文主要介绍了基于TI公司生产的TMS320F2812DSP最小系统设计。

该最小系统主要包括电源、时钟、复位、外扩SRAM以及JTAG接口的设计,为实现基本的程序演示,还增加了外部中断,基本输入输出、以及异步串行通信模块。

关键词:

TMS320F2812;DSP;最小系统;串行通信

6

1 引言

DSP由于运算速度快,具有可编程特性及接口灵活的特点,使得它在电子产品的研制中,发挥着越来越大的作用。

采用DSP器件来实现数字信号处理系统更是成了当前的发展趋势。

如何以最短的开发周期,开发出适于自己应用的高性能低成本的DSP板,己经成为广大DSP工程技术人员共同关心的问题。

DSP最小系统板硬件设计是本文的主要任务。

在介绍TMS320F2812基本特点的基础上,运用DSP技术和硬件电路设计知识进行了DSP最小系统设计,包括电源设计、复位电路设计、时钟电路设计、外扩存储器设计、JTAG接口设计等,为实现基本的程序演示,还增加了外部中断,基本输入输出、以及异步串行通信模块。

本文使用AltiumDesignerSummer09设计电路板,绘制电路原理图,并对最小系统的高速PCB板进行了设计。

最后,以自行设计的高速DSP板为硬件平台,使用CCS3.3软件,编写测试程序。

经过多次软硬件调试和测试,验证了DSP最小系统板卡能正常运行,能满足基本信号处理的要求。

2 硬件设计

2.1 电源设计

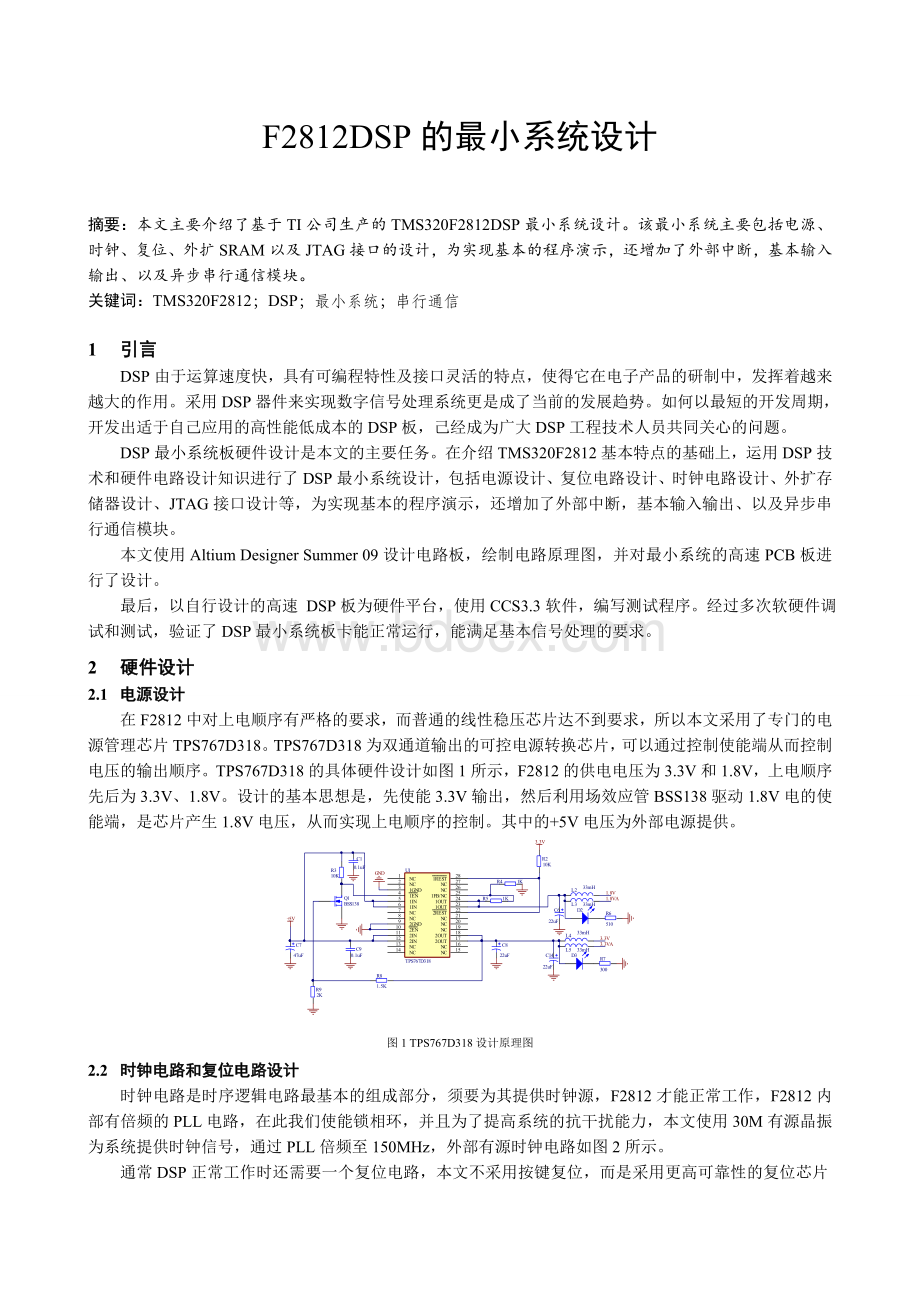

在F2812中对上电顺序有严格的要求,而普通的线性稳压芯片达不到要求,所以本文采用了专门的电源管理芯片TPS767D318。

TPS767D318为双通道输出的可控电源转换芯片,可以通过控制使能端从而控制电压的输出顺序。

TPS767D318的具体硬件设计如图1所示,F2812的供电电压为3.3V和1.8V,上电顺序先后为3.3V、1.8V。

设计的基本思想是,先使能3.3V输出,然后利用场效应管BSS138驱动1.8V电的使能端,是芯片产生1.8V电压,从而实现上电顺序的控制。

其中的+5V电压为外部电源提供。

图1TPS767D318设计原理图

2.2 时钟电路和复位电路设计

时钟电路是时序逻辑电路最基本的组成部分,须要为其提供时钟源,F2812才能正常工作,F2812内部有倍频的PLL电路,在此我们使能锁相环,并且为了提高系统的抗干扰能力,本文使用30M有源晶振为系统提供时钟信号,通过PLL倍频至150MHz,外部有源时钟电路如图2所示。

通常DSP正常工作时还需要一个复位电路,本文不采用按键复位,而是采用更高可靠性的复位芯片IMP809L,当外部供电电压下降至2.7V时,系统就会产生复位,复位电路如图3所示。

图2时钟电路图3复位电路

2.3 外扩SRAM设计

添加SRAM是为了增加系统的存储空间,在F2812中内部存储空间很小,许多程序要求有较大的存储空间,所以应在电气平台中添加SRAM。

F2812中为用户提供了众多外部存储空间,最多可扩展1M*16b的存储空间。

SRAM为静态随机存储器,一般由存储矩阵、地址译码器和读写控制电路组成。

本文采用IS61LV12816SRAM,IS61LV12816有16根数据总线和17根地址总线,最大存储空间为128K*16b。

在F2812Z中,可用的外部存储空间为Zone0、Zone1、Zone2、Zone6,其中Zone0、Zone1共用一个片选信号线(44脚),Zone2的片选信号是(88脚),Zone6的片选信号是(133脚),本文将Zone2分配给SRAM,在硬件设计上,将(88脚)连接到IS61LV12816的片选信号()上,同时将DSP的读使能信号线和写使能信号线分别接到IS61LV12816的读、写使能信号线上,实现对IS61LV12816的读写控制。

DSP可选配置为微计算机模式或者微处理器模式,IS61LV12816设计电路如图4所示。

图4IS61LV12816设计原理图

2.4 JTAG接口电路设计

为方便程序的调试和下载,须要一个JTAG接口,如图5所示。

在程序调试时,须要配合CCS编译环境以及XD510/XD560仿真器配合使用。

图5JTAG接口电路

2.5 RS-232(串口)设计

串行通信接口(SCI)是一个采用发送、接收双线制的异步串行通信接口,即通常所说的UART口,它支持16级的接收发送FIFO,从而降低了串口通信时CPU的开销。

SCI模块支持CPU和其它使用非归零制(NRZ)的外围设备之间的数字通信。

在不使用FIFO的情况下,SCI接收器和发送器采用双级缓冲模式,此时SCI接收器和发送器都有独立的使能和中断位,它们可以被设置成独立操作或者同时进行全双工通信模式。

在F2812中有两路串行通信接口(SCI口),本文将SCIB口设计成RS-232口,主要测试与上位机进行通信的功能,电平转换芯片采用美信公司的MAX3232。

与上位机通信的接口采用通用的串口DB9,串口通信电路如图6所示。

图6RS-232硬件设计电路图

2.6 GPIO(流水灯)设计

为测试通用输入输出,本文设计了流水灯电路,首先是一个灯亮、灭,然后两个灯亮、灭,如此,灯的数目依次增加,直到8个灯全部点亮,最终灭灯。

如图7所示。

图7流水灯设计电路图

2.7 外部中断设计

为测试外部中断,本文设计了按键形式的外部中断源,使用F2812XINT1中断引脚,如图6所示。

图8外部中断

3 软件(测试程序)设计

在程序测试部分本文实现这样的功能,将上位机与F2812通过串口相连,上位机可以利用串口调试助手发送数据给F2812,当F2812接收到的数据为‘a’时,开启流水灯;每按一次按键,F2812向上位机发送一个数据‘s’,利用串口调试助手可以看到接收的数据,并且关闭流水灯。

3.1 系统设置总程序

/*------------------------------------------------------------**

**文件名:

MinSys.c**

**处理器:

DSP281x**

**版本:

DSP281xC/C++HeaderFilesV1.20**

**Boot配置:

boottoZone2**

**功能描述:

F2812最小系统测试**

**修订日期:

2011-06-12**

**备注:

外部中断、定时、GPIO、SCI**

**------------------------------------------------------------*/

#include"DSP281x_Device.h"//DSP281x头文件

#include"DSP281x_Examples.h"//DSP281x头文件

voidInitGpio(void); //初始化GPIO,复用,方向

voidIsrAddr(void); //定义中断服务程序的入口地址

voidPieIntEnable(void); //使能PIE级中断

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- F2812DSP 最小 系统 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls