计算机组成原理阵列乘法器课程设计汇本报告.docx

计算机组成原理阵列乘法器课程设计汇本报告.docx

- 文档编号:2480050

- 上传时间:2022-10-30

- 格式:DOCX

- 页数:13

- 大小:587.35KB

计算机组成原理阵列乘法器课程设计汇本报告.docx

《计算机组成原理阵列乘法器课程设计汇本报告.docx》由会员分享,可在线阅读,更多相关《计算机组成原理阵列乘法器课程设计汇本报告.docx(13页珍藏版)》请在冰豆网上搜索。

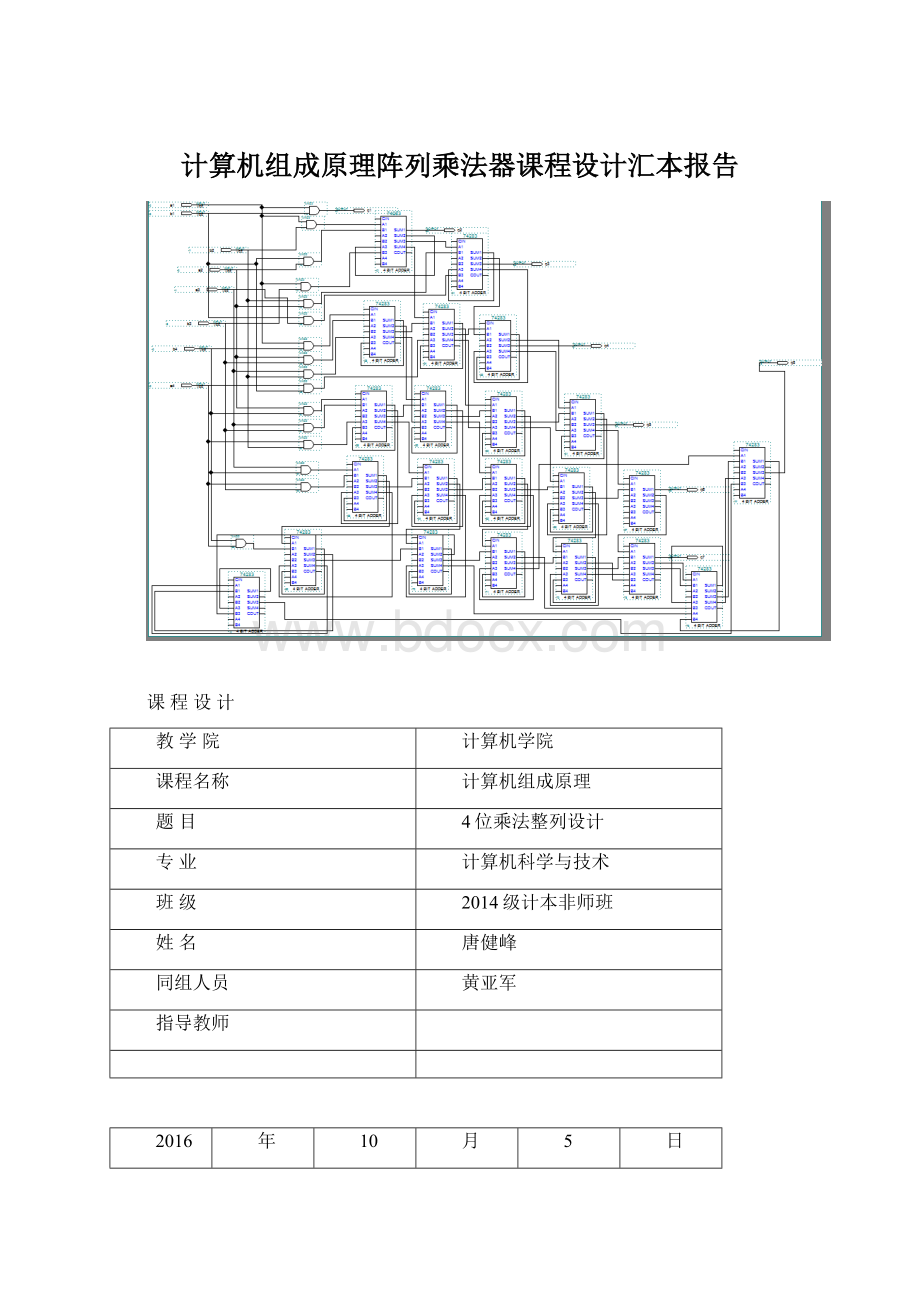

计算机组成原理阵列乘法器课程设计汇本报告

课程设计

教学院

计算机学院

课程名称

计算机组成原理

题目

4位乘法整列设计

专业

计算机科学与技术

班级

2014级计本非师班

姓名

唐健峰

同组人员

黄亚军

指导教师

2016

年

10

月

5

日

1课程设计概述

1.1课设目的

计算机组成原理是计算机专业的核心专业基础课。

课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。

同时也巩固了我们对课本知识的掌握,加深了对知识的理解。

在设计中我们发现问题,分析问题,到最终的解决问题。

凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。

1.2设计任务

设计一个4位的二进制乘法器:

输入信号:

4位被乘数A(A1,A2,A3,A4),4位乘数B(B1,B2,B3,B4),

输出信号:

8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8).

1.3设计要求

根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。

(1)制定设计方案:

我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。

(2)客观要求

要掌握电子逻辑学的基本容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。

小组成员要积极配合共同达到目的。

2实验原理与环境

2.11.实验原理

计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。

2.22.实验环境

2.2.1双击maxplu2II软件图标,启动软件

(1).新建工程,flie->newproject....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。

点击OK

(2).原理图输入

(1)建立图形输入文件在图1-16中的File菜单的project项下选择“New…”,出现图1-18所示的对话框

选择“GraphicEditorfile”后,单击“OK”,出现图1-19即可开始建立图形输入文件

(3).调入元件符号在图1-19图形编辑区双击鼠标左键可打开“Entersymbol”对话框,如图1-20所示。

在该对话框你可选择需要输入的元件/逻辑符号。

例如你可选择一个计数器,一个与门等

3总体方案设计

总体结构图

图3总体结构图一

根据an与bn的乘积,然后相应的am与bm与运算,可得到qn的值,最后按从大到小的顺序排列qn,即为计算结果。

如下所示:

1100

*0101

1100

0000

1100

0000

0111100

即为十进制的12*5=60

1.设计方案

(1)为了进一步提高乘法运算速度,可采用类似人工计算的方法,阵列的每一行送入乘数Y的每一数位,而各行错开形成的每一斜列则送入被乘数的每一数位。

(2)4×4阵列乘法器可以由一定数量的4个输入加法器构成的;

(3)4个输入加法器可以由多个全加1器(74283)构成;

详细设计与实现

4*4乘法的设计主要包括以下几个主要的模块的设计

3.1.2一位全加器的设计与实现

一位全加器的逻辑图,如下图所示:

图5一位全加器的逻辑图

3.1.3四位及八位求补电路的设计原图:

四位求补电路的逻辑图,如下图所示:

图6四位求补电路的逻辑图

八位求补电路的逻辑图,如下图所示:

图7八位求补电路的逻辑图

3.1.4阵列乘法器的设计:

4×4阵列乘法器的逻辑图,如下图所示:

图84×4阵列乘法器的逻辑图

图9阵列乘法器的电路原理图

4实验过程与调试

实验仿真图:

图10仿真结果

4位*4位乘法器的仿真结果如图:

图114*4的乘法器仿真图

4.1主要故障与调试

4.1.1故障1这次课程设计的精华之一就是设计阵列乘法器刚开始时由于按照课本上的设计所以掉下了好多的与门所以在仿真的时候出现了好多的问题,后在老师的指导下,,得以改进了设计和避免了很多的连线的错误,提高了速度

4.1.2故障2在实验的时候,对实验的软件和装置很不是熟悉,导致文件的命名时经常出错,而且问题还不宜被发现,在老师的提示下照到了问题的所在,后来就没有遇到类似的问题。

4.1.3故障3在做求补电路的时候我们做的事4位的求补器但是需要8位的求补器所以我们就拿两个4位的求补器去连接结果由于连线的错误导致了好多的错误,后来我们直接连接8位的求补器就解决了问题。

5设计总结与心得

5.1课设总结

基于对象的存储是为了克服当前基于块的存储存在的诸多难题,在存储接口和结构层次的重要发展。

可以根据应用负载选择优化的存储策略。

作了如下几点工作:

1)我们小组负责的是阵列乘法器的设计,通过小组的合作我们一次完成了全加器、求补器、阵列乘法器然后完成了综合的拼接工作,虽然在最后的阶段出了一些问题但是我们小组掌握了此次设计的核心容达到了实验的目的。

2)此次看课程设计我们实现任意给定两位四位二进制的相乘运算,相乘积的计算结果为8位二进制。

将移位复制的被乘数依次对准乘数数位的位置进行排列,然后将各列相加。

如果乘数的某一数位为0,将跳过相应的被乘数,下一个复制被乘数的位置是由向乘数的最高位方向移动时有1出现的位置

3)这次课程设计虽然没有在规定的时间完成要求的任务,但是我们小组每一个组员都认真负责的设计,对组成原理这门学科的了解更加深刻,学到了好多以前不曾知道的知识。

其他需要总结的容,(自行修订扩充)。

5.2课设心得

在还没有作课程设计时我是比较畏惧组成原理这门课设的,毕竟前几次小实验每每都是做得很不尽人意,总是不能在老师规定的时间完成,所以担心这种不好的过程会给后面的大实验也即课设带来很大的负面影响。

这次实验我的设计题目是-阵列乘法器,通过和同学的讨论和老师的交流,并在老师的指导下,解决了很多的问题,从其中获得了知识,使得我对环境和工具的使用能力得到了进一步的提升,我相信,这将给以后的学习和实验带来益处,最后圆满的完成了实验。

此次课程设计实验,不仅是对课程知识的巩固,对所学理论知识的很好应用与发挥,更是对新知识的学习,新鲜工具的应用的提升和实践能力的提升,而且对个人自学能力的也是一个极大考验,处于信息快速发展更新世代人只有不断提高自身自学能力才能很好地接受合理地利用信息化时代所出现的各色个样的产品。

这次课设然我领悟到很多课本以外的一些生活处事道理:

(1)学习是永无止境不断充实自我提升自身价值就得不断地接受并吸收新鲜事物。

(2)合作是前进的最佳途径,现在所做的只是小的实验项目步入社会合作精神会比自身能力来得更重要;

参考文献

[1]磊华,王小兰.计算机组成原理实验指导及课程设计指导书(基于EDA平台).:

华中科技大学,2010年.

[2]磊华,吴非,莫正坤.计算机组成原理.:

清华大学,2011年.

[3]DAVIDA.PATTERSON(美).计算机组成与设计硬件/软件接口(原书第3版).:

机械工业.2007年.

[4]袁春风编著.计算机组成与系统结构.:

清华大学,2011年.

[5]志刚,FPGA与SOPC设计教程-DE2实践.:

电子科技大学,2007

计算机组成原理课程设计成绩评定表

1、课程设计答辩或质疑记录

1

2

3

2、答辩情况

a)未能完全理解题目,答辩情况较差□c)理解题目较清楚,问题回答基本正确□

b)部分理解题目,答辩情况较差□d)理解题目透彻,问题回答流利□

3、课程设计报告

a)容:

不完整□完整□详细□

b)方案设计:

较差□合理□非常合理□

c)实现:

未实现□部分实现□全部实现□

d)文档格式:

不规□基本规□规□

考勤成绩:

,

占总成绩比例10%

答辩成绩:

,

占总成绩比例30%

课程设计论文成绩:

,

占总成绩比例60%

课程设计总成绩:

4、课程设计评语

指导教师签字:

年月日

1.一位全加器FA的部由哪些逻辑门构成?

采用一个或门进位其结果Si三个输入信号AiBiCi异或得到,信号Ci+1位进位.

2.第二题中,阵列乘法器的算前求补器的作用是?

将两个操作数A和B在不带符号的乘法阵列相乘以前,先变成正整数.

3.阵列乘法器的算后求补器的作用是?

当两个输入操作数的符号不一致时把运算额结果变成带符号位的原码.

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机 组成 原理 阵列 乘法器 课程设计 本报

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls