计算机系统结构课后题资料.docx

计算机系统结构课后题资料.docx

- 文档编号:24374819

- 上传时间:2023-05-26

- 格式:DOCX

- 页数:14

- 大小:334.60KB

计算机系统结构课后题资料.docx

《计算机系统结构课后题资料.docx》由会员分享,可在线阅读,更多相关《计算机系统结构课后题资料.docx(14页珍藏版)》请在冰豆网上搜索。

计算机系统结构课后题资料

[例题1.1]假设将某一部件的处理速度加快到10倍,该部件的原处理时间仅为整个运行时间的40%,则采用加快措施后能使整个系统的性能提高多少?

[解答]由题意可知:

Fe=0.4,Se=10,根据Amdahl定律,加速比为:

Sn=1/(0.6+0.4/10)=1.56

[例题1.2]采用哪种实现技术来求浮点数平方根FPSQR的操作对系统的性能影响较大。

假设FPSQR操作占整个测试程序执行时间的20%。

一种实现方法是采用FPSQR硬件,使FPSQR操作的速度加快到10倍。

另一种实现方法是使所有浮点数据指令的速度加快,使FP指令的速度加快到2倍,还假设FP指令占整个执行时间的50%。

请比较这两种设计方案。

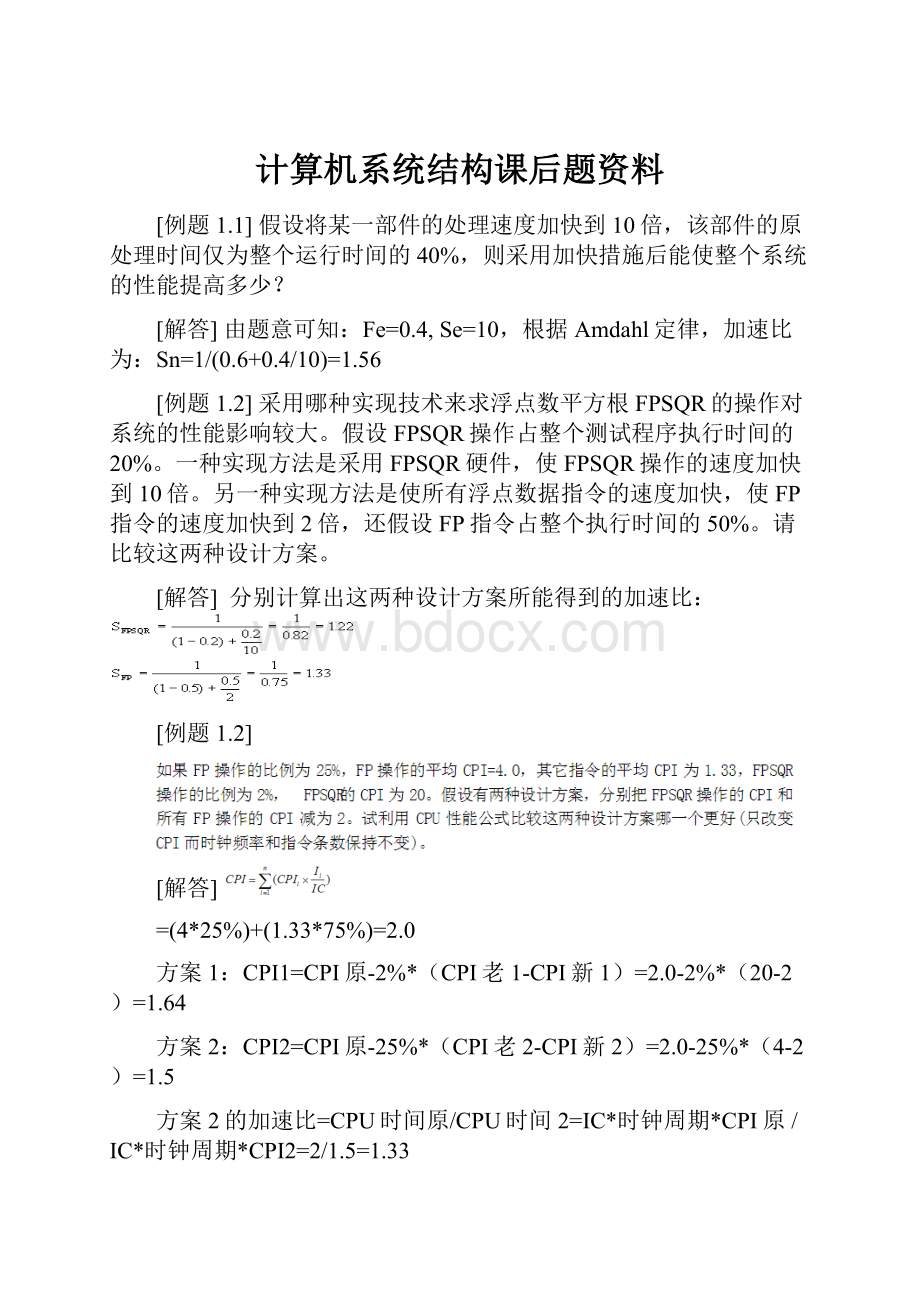

[解答]分别计算出这两种设计方案所能得到的加速比:

[例题1.2]

[解答]

=(4*25%)+(1.33*75%)=2.0

方案1:

CPI1=CPI原-2%*(CPI老1-CPI新1)=2.0-2%*(20-2)=1.64

方案2:

CPI2=CPI原-25%*(CPI老2-CPI新2)=2.0-25%*(4-2)=1.5

方案2的加速比=CPU时间原/CPU时间2=IC*时钟周期*CPI原/IC*时钟周期*CPI2=2/1.5=1.33

[习题1.17]假设高速缓存Cache工作速度为主存的5倍,且Cache被访问命中的概率为90%,则采用Cache后,能使整个存储系统获得多高的加速比Sp?

[解答]我们首先对新的存储系统的性能做以下的假设:

在Cache不命中的情况下,对Cache的访问不会额外损失时间,即:

首先,决定Cache是否命中所用的时间可以忽略;其次,在从主存向Cache传输的同时,数据也被传输给使用部件(不需要再从Cache中读取)。

这样,新的存储系统中,平均存取时间分为两个部分:

其中,R表示各种情况所占的比例。

根据加速比的计算公式,

[习题1.19]

[解答]CPI=∑CPIi×[Ii/Ic]=45000/105+(32000×2)/105+(15000×2)/105+(8000×2)/105=1.55

MIPS=(40×106)/(1.55×106)=25.8MIPS

Te=105/(25.8×106)=3.88ms

[习题1.20]某工作站采用时钟频率为15MHz、处理速率为10MIPS的处理机来执行一个已知混合程序。

假定每次存储器存取为1周期延迟、试问:

(1)此计算机的有效CPI是多少?

(2)假定将处理机的时钟提高到30MHz,但存储器子系统速率不变。

这样,每次存储器存取需要两个时钟周期。

如果30%指令每条只需要一次存储存取,而另外5%每条需要两次存储存取,还假定已知混合程序的指令数不变,并与原工作站兼容,试求改进后的处理机性能。

[解答]

(1)由MIPS=时钟频率/(CPI×106),则有:

CPIA=时钟频率/(MIPS×106)=1.5。

(2)当时钟频率为15MHZ时,假设不进行存储操作指令的CPI为x,则要进行一次存储操作指令的CPI为1+x,要进行二次存储操作指令的CPI为2+x,因此有:

1.5=x×65%+(1+x)×30%+(2+x)×5%

解得x=1.1

当时钟频率为30MHZ时,不进行存储操作指令的CPI不变为1.1,要进行一次存储操作指令的CPI为2+x=3.1,要进行二次存储操作指令的CPI为4+x=5.1,因此平均CPI为:

CPIB=1.1×65%+3.1×30%+5.1×5%=1.9

所以MIPSB=时钟频率/(CPIB×106)=(30×106)/(1.9×106)=15.8

[习题2.13]一个处理机共有10条指令,各指令在程序中出现的概率如下表:

指令信号出现概率Huffman编砝码2/8扩展编砝码3/7扩展编砝码10.250.2030.1540.105

一个处理机共有10条指令,各指令在程序中出现的概率如下表:

指令信号出现概率Huffman编砝码2/8扩展编砝码3/7扩展编砝码

10.25

20.20

30.15

40.10

50.08

60.08

70.05

80.04

90.03

100.02

(1)采用最优Huffman编码法(信息熵)计算这10条指令的操作码最短平均长度。

(2)采用Huffman编码法编写这10条指令的操作码,并计算操作码的平均长度,计算与最优Huffman编码法(信息熵)相比的操作码信息冗余量。

将得到的操作码编码和计算的结果填入上面的表中。

(3)采用2/8扩展编码法编写这10条指令的操作码,并计算操作码的平均长度,计算与最优Huffman编码法相比的操作码信息冗余量。

把得到的操作码编码和计算的结果填入上面的表中。

(4)采用3/7扩展编码法编写这10条指令的操作码,并计算操作码的平均长度,计算与最优Huffman编码法相比的操作码信息冗余量。

把得到的操作码编码和计算的结果填入上面的表中。

[解答]

[习题2.14]

一台模型机共有7条指令,各指令的使用频度分别是35%、25%、20%、10%、5%、3%、

2%,有8个通用数据寄存器,2个变址寄存器。

(1) 要求操作码的平均长度最短,请设计操作码的编码,并计算所设计操作码

的平均长度。

(2) 设计8位字长的寄存器-寄存器型指令3条,16位字长的寄存器-存储器型变址寻址方式指令4条,变址范围不小于正、负127。

请设计指令格式,并给出各字段的长度和操作码的编码。

[解答]

[习题2.15]

某处理机的指令字长为16位,有双地址指令、单地址指令和零地址指令三类,并假设每个地址字段的长度均为6位。

(1) 如果双地址指令有15条,单地址指令和零地址指令的条数基本相同,问单地址指令和零地址指令各有多少条?

并且为这三类指令分配操作码。

(2) 如果要求三类指令的比例大致为1:

9:

9,问双地址指令、单地址指令和零地址指令各有多少条?

并且为这三类指令分配操作码。

[解答]

(1)双地址指令格式为:

466

操作码

地址码1

地址码2

单地址指令格式为:

106

操作码

地址码

零地址指令格式为:

16

操作码

双地址指令15条,操作码为:

0000~1110;

单地址指令26-1=63条,操作码为:

1111 000000~1111 111110

零地址指令26=64条,操作码为:

1111 111111 000000~1111 111111 111111

(2)双地址指令14条,地址码:

0000~1101;

单地址指令26*2-2=126条,1110000000~1110111110,1111000000~1111111110;

零地址指令128条1111111111000000~1111111111111111。

[习题3.1]什么是存储系统?

对于一个由两个存储器M1和M2构成的存储系统,假设

M1的命中率为h,两个存储器的存储容量分别为s1和s2,存取时间分别为t1和t2,每千字节的成本分别为c1和c2。

⑴ 在什么条件下,整个存储系统的每千字节平均成本会接近于c2?

⑵ 该存储系统的等效存取时间ta是多少?

⑶ 假设两层存储器的速度比r=t2/t1,并令e=t1/ta为存储系统的访问效率。

试以

r和命中率h来表示访问效率e。

⑷ 如果r=100,为使访问效率e>0.95,要求命中率h是多少?

⑸ 对于⑷中的命中率实际上很难达到,假设实际的命中率只能达到0.96。

现在

采用一种缓冲技术来解决这个问题。

当访问M1不命中时,把包括被访问数据在内的一个数据块都从M2取到M1中,并假设被取到M1中的每个数据平均可以被重复访问5次。

请设计缓冲深度(即每次从M2取到M1中的数据块的大小)。

[解答]

[习题3.3]

要求完成一个两层存储系统的容量设计。

第一层M1是Cache,其容量有三

种选择:

64KB、128KB和256KB,它们的命中率分别为0.7、0.9和0.98;第二层M2是主存储器,其容量为4MB。

并设两个存储器的存取时间分别为t1和t2,每千字节的成本分别为c1和c2。

如果c1=20c2和t2=10t1。

⑴ 在t1=20ns的条件下,分别计算三种存储系统的等效存取时间。

⑵ 如果c2=0.2美元/KB,分别计算三种存储系统每千字节的平均成本。

⑶ 对三种存储系统的设计作一个比较,并分别按平均成本和等效存取时间指出

它们性能的排列次序。

⑷ 根据等效存取时间和平均成本的乘积,选择最优的设计。

[解答]

(1)t=ht1+(1–h)t2,

当cache为64k时,t=0.7*20ns+(1-0.7)*200ns=74ns;

当cache=128k时,t=38ns;

当cache=256k时,t=23.6ns

(2)按照公式:

cache=64k,c=0.2585美元/k字节;

cache=128k,c=0.3152美元/k字节;

cache=256k,c=0.4235美元/k字节

(3)按等效访问时间由小到大排序,容量分别为:

256k,128k,64k

按每字节平均价格由小到大排序,分别为:

64k,128k,256k

(4)①19.129ns.美元/k字节;

②11.9776ns.美元/k字节;

③9.9946ns.美元/k字节;

选256k的cache最优

[习题3.7]有16个存储器模块,每个模块的容量为4M字节,字长为32位。

现在要用这16个存储器模块构成一个主存储器,有如下几种组织方式:

方式1:

16个存储器模块采用高位交叉方式构成存储器。

方式2:

16个存储器模块构成并行访问存储器。

方式3:

16个存储器模块采用低位交叉方式构成存储器。

方式4:

2路高位交叉8路低位交叉构成存储器。

方式5:

4路高位交叉4路低位交叉构成存储器。

方式6:

4路并行访问4路低位交叉构成存储器。

⑴ 写出各种存储器的地址格式。

⑵ 比较各种存储器的优缺点。

⑶ 不考虑访问冲突,计算各种存储器的频带宽度。

⑷ 画出各种存储器的逻辑示意图。

[解答]

(1)主存地址格式:

区号E

区内组号G

组内块号B

块内地址W

1

1

1

4

(2)Cache地址格式:

组号

组内块号

块内地址

1

1

4

(3)主存与Cache中各个块的映象对应关系:

(4)Cache的块地址流情况:

B6B2B4B1B4B6B3B0B4B5B7B3

C2C3C0C1C0C2C3C1C0C1C2C3

(5)FIFO中Cache的块命中率:

3/12=25%

(6)LFU中Cache的块命中率:

4/12=33.3%

(7)改为全相联映象后:

FIFO中块命中率:

4/12=33.3%

LFU中块命中率:

3/12=25%

(8)这时Cache的命中率:

1-8/(16×12)=95.8%

[习题5.8]用一条5个功能段的浮点加法器流水线计算F=

。

每个功能段的延迟时间均相等,流水线的输出端与输入端之间有直接数据通路,而且设置有足够的缓冲寄存器。

要求用尽可能短的时间完成计算,画出流水线时空图,计算流水线的实际吞吐率、加速比和效率。

[解答]

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

21

吞吐率:

加速比:

S=9*5/21=15/7

效率:

[习题5.11]一条有4个功能段的非线性流水线,每个功能段的延迟时间都相等,都为20ns,它的预约表如下:

(1)写出流水线的禁止集合和初始冲突向量。

⑵画出调度流水线的状态图。

⑶求流水线的最小启动循环和最小平均启动距离。

⑷求平均启动距离最小的恒定循环。

⑸求流水线的最大吞吐率。

⑹按照最小启动循环连续输入10个任务,求流水线的实际吞吐量。

⑺画出该流水线各功能段之间的连接图。

[解答]禁止向量:

(6,4,2)初始冲突向量:

(101010)

状态图:

7

101010

715737

101111

101011

111111

5

3

5

简单循环

平均启动距离

7

7

5

5

1,7

4

3,7

5

5,7

6

3,5

4

5,3,7

5

恒定循环:

5

最小循环:

1+7=4

最大吞吐率:

实际吞吐率:

S2

S3

S4

S1

in

out

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机系统 结构 课后 资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《包身工》教案设计精选文档.docx

《包身工》教案设计精选文档.docx