ISE入门教程.docx

ISE入门教程.docx

- 文档编号:24137218

- 上传时间:2023-05-24

- 格式:DOCX

- 页数:12

- 大小:945.83KB

ISE入门教程.docx

《ISE入门教程.docx》由会员分享,可在线阅读,更多相关《ISE入门教程.docx(12页珍藏版)》请在冰豆网上搜索。

ISE入门教程

ISE整体开发流程:

建工程→编写工程代码→检查语法错误→行为仿真→综合→管脚约束→实现→时序仿真→生成bit流文件→下载到板子上调试;

实验是用ISE10.1做的,与ISE9.1不同的地方在文中也有相关说明。

一:

建工程

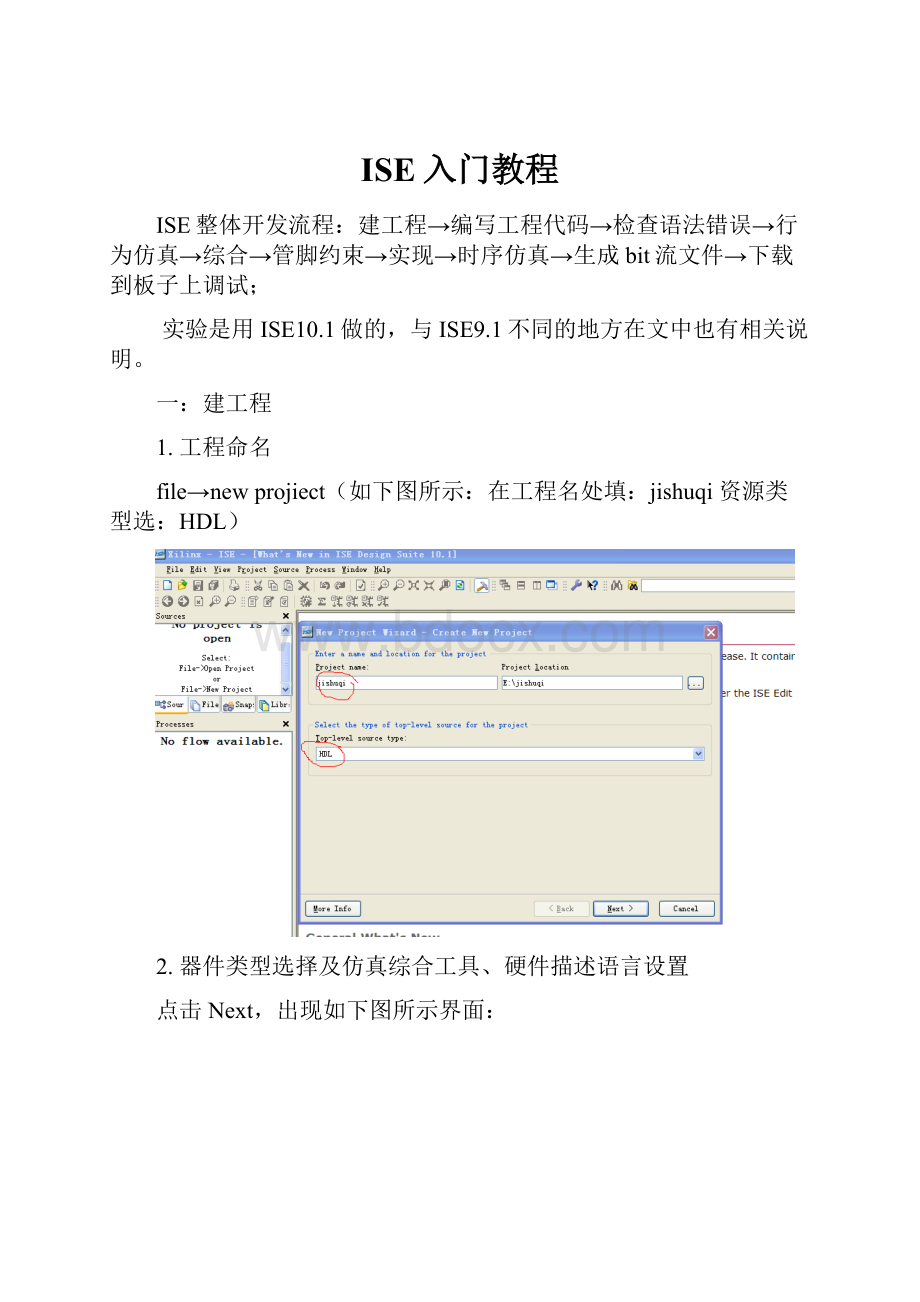

1.工程命名

file→newprojiect(如下图所示:

在工程名处填:

jishuqi资源类型选:

HDL)

2.器件类型选择及仿真综合工具、硬件描述语言设置

点击Next,出现如下图所示界面:

图中设置的有:

Family:

virtex2P;Device:

XC2VP30;Package:

FF896;Speed:

-7(这个是根据VIRTEX2P开发板设置的数据,不同的开发板设置的数据不一样)。

3.完成工程的建立

.一直点击next,出现如下图界面后,点Finish完成工程的建立:

二.编写HDL代码(工程此部分是在Implementation下完成的)

1.在Sources区域点击右键选择newsource,出现如下图所示的界面,按照如下图设置,然后一直点Next,一直到Finish完成代码文件界面:

3.接下来开始HDL代码编写,这里是一个简单的十进制计数器的编写:

代码编写好后,点击保存,然后检查看编写代码是否有错误,如上图所示,CheckSyntax点击检查后是绿色的勾,则代码没有语法错误,可以进行下一步功能仿真;

modulejishuqi(clk,rst,q);

inputclk,rst;

output[3:

0]q;

reg[3:

0]q;

always@(posedgeclk)

begin

if(rst==0)

q<=4'b0;

else

begin

if(q==4'b1010)

q<=0;

else

q<=q+1;

end

end

endmodule

三、行为(功能)仿真

1.同样在Sources区域右键添加NewSource如下图所示,添加图形仿真文件:

2.一直点Next,最后finish掉到如下图所示的,时钟设置界面:

如上图所示:

1.选择RisingEdge时钟上升沿有效;2.选择对应设计的时钟信号;

3.设置clk的频率,高低电平持续时间;4.设置仿真时间为1000ns;

3.点Finish进入波形编辑界面,如下图所示:

(rst是要编辑的波形)

编辑之后波形如下所示:

点击保存;

3.如下图选择:

在Sourcesfor选择BehavioralSimulations

4.依次点击1,2,然后双击,待运行后,最后出现如下图的仿真结果:

到此时完成了行为仿真。

四、综合

先单击1,然后双击2,待运行正确后,再双击运行3则可以看到右边用HDL描述出来的RTL电路,如下图所示:

五、管脚约束

先点击1,之后双击2,再在3区域设置Viertex2P开发板对应的时钟管脚设置(clk设置为aj15),设置完成后保存!

下面是ISE9.1的界面:

六、实现

实现是把设计的电路映射到FPGA中,生成相应的工程文件;其包括三个步骤:

翻译、映射、布局布线。

操作:

先单击1,然后双击ImplementDesign,出现如下图中2处1则正确!

七、时序仿真

时序仿真是看设计的时序是否符合要求:

操作:

现在1处选择后仿真,然后单击2,再双击3,待运行后出现了右边的仿真结果:

如上图所示,可以分析时序仿真与行为仿真的不同:

时序仿真有延时t,还有4处的毛刺!

八、生成比特流文件(配置FPGA文件)

双击2处,生成编程文件:

九、配置FPGA

双击红线处,进行相应的IMPACT配置,并连接好开发板后才能配置到FPGA中。

NOTE:

文中第九节配置FPGA具体怎么配置没有提到,其涉及到其他软件的使用,此次主要是熟悉ISE软件;这个将在大家后续进一步学习中会用到!

此为我以我的理解写的一个简单的教程,主要目的是让刚入门的同学熟悉用ISE开发FPGA的一个整体流程,所以比较具体但不深入,还有很多细节的东西,希望大家在学习的时候注意,多查下资料和书本,这方面的资料很多!

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ISE 入门教程

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《包身工》教案设计精选文档.docx

《包身工》教案设计精选文档.docx