基于FPGA的加法器设计范文.docx

基于FPGA的加法器设计范文.docx

- 文档编号:23960161

- 上传时间:2023-05-22

- 格式:DOCX

- 页数:13

- 大小:1,001.73KB

基于FPGA的加法器设计范文.docx

《基于FPGA的加法器设计范文.docx》由会员分享,可在线阅读,更多相关《基于FPGA的加法器设计范文.docx(13页珍藏版)》请在冰豆网上搜索。

基于FPGA的加法器设计范文

基于FPGA的加法器设计

一、实验目的

1.熟悉用Quartus编译Verilog语言的方法。

2.掌握用VerilogHDL语言描述加法器的方法。

3.利用nios核建立加法器。

二、实验原理

1.半加器器设计

1)半加法器

a.b为加数和被加数,s.c为和和进位。

(1)半加法器真值表

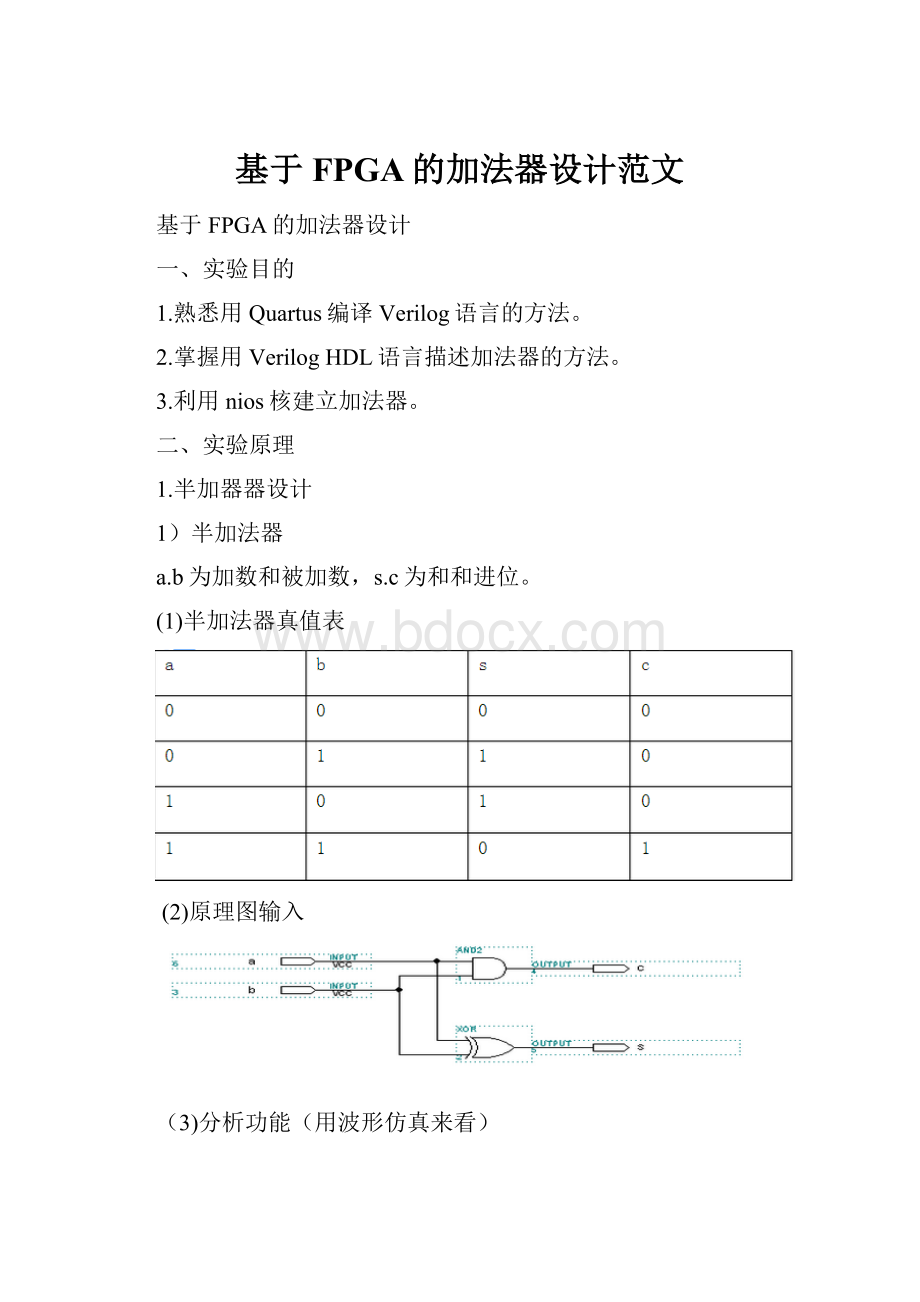

(2)原理图输入

(3)分析功能(用波形仿真来看)

(4)VHDL语言编程

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hjfq is

port(a,b:

in std_logic;

s,c:

out std_logic);

end hjfq;

architecture behave of hjfq is

begin

s<=not(a xor (not b));

c<=a and b;

end behave;

2、全加法器

a.b.c为加数、被加数和低位进位,so.co为和与进位。

(1)全加法器真值表

(2)全加法器原理图:

(3)波形仿真时序图:

(4)VHDL语言编程:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jfq is

port(a,b,c:

in std_logic;

so,co:

out std_logic);

end jfq;

architecture behave of jfq is

signal bb:

std_logic_vector(2 downto 0);

begin

bb<=a&b&c;

process(b)

begin

case b is

when "000"=>co<='0';so<='0';

when "001"=>co<='0';so<='1';

when "010"=>co<='0';so<='1';

when "011"=>co<='1';so<='0';

when "100"=>co<='0';so<='1';

when "101"=>co<='1';so<='0';

when "110"=>co<='1';so<='0';

when "111"=>co<='1';so<='1';

when others => null;

end case;

end process;

end behave;

三、实验步骤

(1)打开QuartusⅡ软件,熟悉软件界面及窗口命令。

(2) 选择File < New Project Wizard弹出对话框,该对话框显示Wizard所包含的各项内容,在弹出的窗口中输入项目的名称和存储位置。

如果选中Don’t show me this introduction again。

那么在下一次在新建项目是可以不再显示本对话框。

点击Next按钮。

(3)选择实验板的具体型号,芯片型号。

选择设置参数完成后显示如图,点击finish按钮完成工程建立。

(4)选择tools< MegaWizardplug-InManager建立加法器

(5)利用nios核建立加法器,选择Arithmetic< ALTFP_ADD_SUB

(6)在“File=>New”的窗口中选择建立Verilog文件。

(7)单击OK后,在Quartus窗口的右方看到该文件,写入代码后选择“File=>Save”,将文件保存在与项目文件同样的位置即可。

然后可以看到如下状态:

(8)设置仿真Assignments< settings

(9)选择Processing< start< StartTestBenchTemplateWriter波形进行编译,打开simulation写仿真文件

(10)设置仿真波形Tools-runEDAsimulationtool-EDARTLsimulation

查看加法器仿真波形

4、实验结果

整个实验过程就是一个提成方案,描述方案,找到问题,解决问题的过程,并且通过这个过程来找到实验的意义。

通过这次实验,主要是对浮点数的运算用verilog代码来描述有了更加深刻的认识,同时也为其他的数据算法用verilog描述有了进一步的心得。

为用verilog构建复杂的数据模块奠定基础,对今后的数字电路设计有深刻的影响。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA 加法器 设计 范文

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《公务员财产申报制度》.docx

《公务员财产申报制度》.docx