EDA作业1秒表.docx

EDA作业1秒表.docx

- 文档编号:23794569

- 上传时间:2023-05-20

- 格式:DOCX

- 页数:12

- 大小:108.74KB

EDA作业1秒表.docx

《EDA作业1秒表.docx》由会员分享,可在线阅读,更多相关《EDA作业1秒表.docx(12页珍藏版)》请在冰豆网上搜索。

EDA作业1秒表

EDA作业一--秒表循环

一、设计任务及要求

1.设计数码管显示的秒表。

2.能够准确的计时并显示。

3.开机显示00.00.00。

4.用户可以随时清零、暂停、计时。

5.最大记时59.59.99分钟,最小精确到0.01秒。

二、设计总体框图

秒表计时器常常用于体育竞赛及各种其他要求有较精确时间的各领域中。

其中启/停开关的使用方法与传统的机械计时器相同,即按一下启/停开关,启动计时器开始计时,再按一下启/停开关计时终止。

而复位开关可以在任何情况下使用,即使在计时过程中,只要按一下复位开关,计时应立即终止,并对计时器清零。

具体框图见附录一。

三、硬件电路设计与程序设计

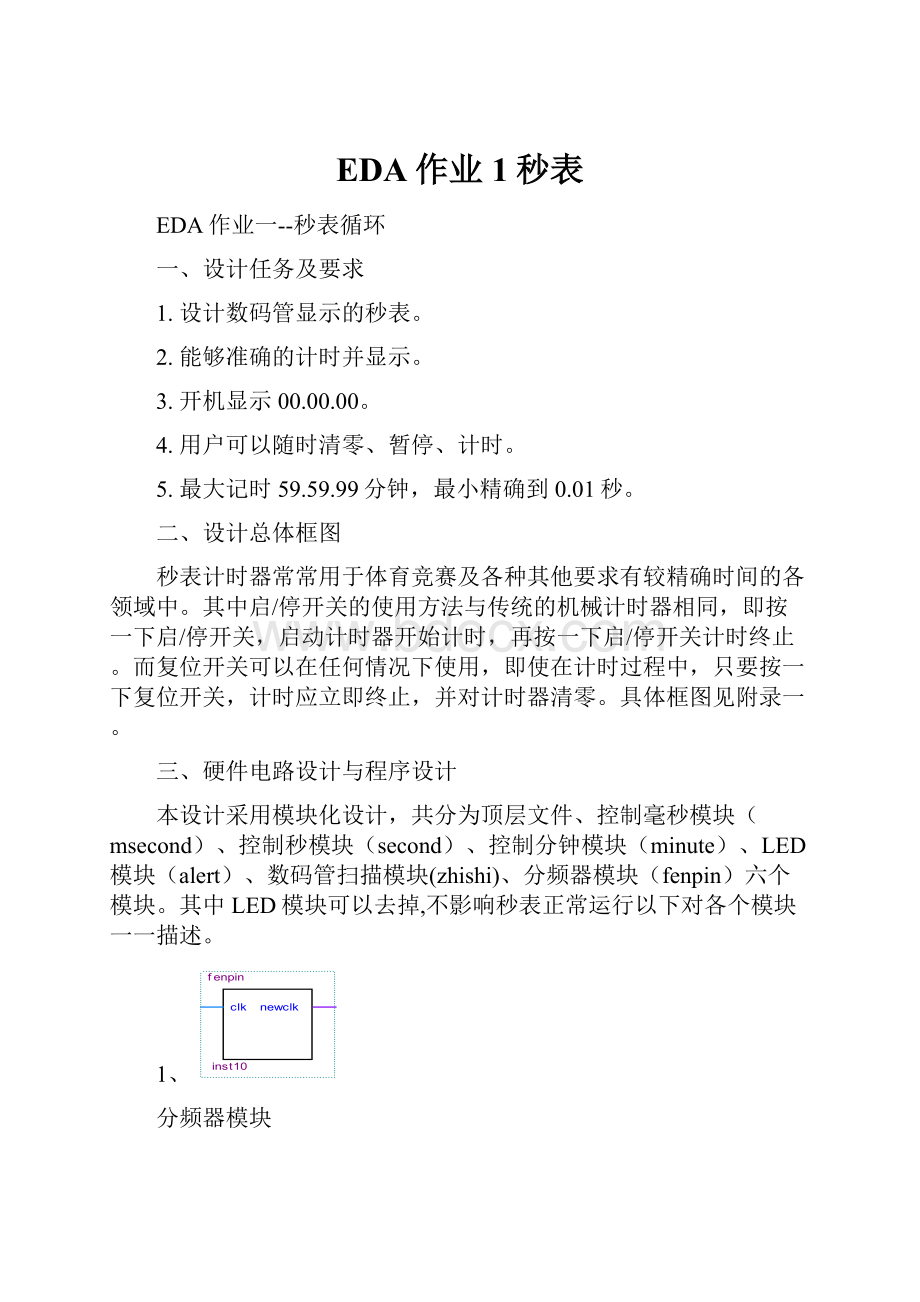

本设计采用模块化设计,共分为顶层文件、控制毫秒模块(msecond)、控制秒模块(second)、控制分钟模块(minute)、LED模块(alert)、数码管扫描模块(zhishi)、分频器模块(fenpin)六个模块。

其中LED模块可以去掉,不影响秒表正常运行以下对各个模块一一描述。

1、

分频器模块

系统的输入时钟为4100HZ,用来驱动显示电路;同时输入时钟通过41分频,可以产生100HZ的频率来驱动计数电路,即为0.01秒,程序见附录二。

2.控制毫秒模块

对这个功能模块用一个进程语句描述。

clk、reset和调秒的setsec(暂停\启动)为输入信号程序见附录二。

3.控制秒模块

程序见附录二

4.控制分模块

程序见附录二

5.数码管模块

该模块的功能是选择个计数端口来的数据,当相应的数据到来时数据选择器选择器数据后输出给数码管,并由数码管显示。

程序见附录二

四、编译仿真

下面使用QuartusII对本设计进行编译和仿真。

首先创建工程,使用文本编辑器输入本设计的所有模块的源程序,把G-1DE.vhd设为顶层文件。

把本设计中的所有设计文件添加进工程后,先对每个模块进行编译纠错,然后把各个模块连接在一起保存然后在全程编译,通过之后就可以进行仿真。

先进行软件仿真每一部分的仿真从略,下面只说明系统的整体仿真波形。

系统工作时的仿真波形附录三所示。

五、心得体会

通过两周的努力,课程设计任务终于完成了,如果老师不给我们框架的话,我想就算给我两周的时间我也不可能做的出来.通过这次课程设计,对VHDL的语言有了更深刻的认识,对课题设计的基本流程有了一定的认识,同时也是一次把原来所学的书本知识和实践相联系的过程。

并通过实践,建立起了学习EDA的浓厚兴趣。

在设计中也深刻体会到了团队精神的重要性!

此次设计是一个人完成的,真的花费了很大经历。

团结协作是我们实习成功的一项非常重要的保证。

对EDA的设计平台QuartusⅡ有了熟练的使用。

掌握了本次设计所用的EDA试验箱用法,为以后更好的学习EDA打下了基础。

通过这次课程设计,我意识到了我对这门课掌握还有一定的不足,还有许多的知识我不了解;有的是一知半解;有的即使原理懂了,但在应用方面却是丝毫不知。

所以在今后的学习中,我会更加努力,不仅要学好理论知识,还要把它应用到实践中去,使两者很好的结合起来,互补互助。

附录1:

原理图

附录2:

程序

一、分频器

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYfenpinIS

port(

clk:

INSTD_LOGIC;

newclk:

OUTSTD_LOGIC);

ENDentityfenpin;

ARCHITECTUREfunOFfenpinIS

signalenter:

integer;

begin

process(clk)is

begin

ifclk’eventandclk=’1’then

ifenter=40thenenter<=0;

elseenter<=enter+1;

endif;

endif;

endprocess;

process(enter)is

begin

ifenter=40thennewclk<=’1’;

elsenewclk<=’0’;

endif;

endprocess;

endfun;

二、毫秒模块:

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYmsecondIS

port(

clk,reset,setsec:

INSTD_LOGIC;

ensec:

OUTSTD_LOGIC;

daout:

OUTstd_logic_vector(7downto0));

ENDentitymsecond;

ARCHITECTUREfunOFmsecondIS

SIGNALcount:

STD_LOGIC_VECTOR(7downto0);

begin

daout<=count;

process(clk,reset,setsec)

begin

if(reset=’0’)then

count<=“00000000”;

elsif(setsec=’0’)then

elsif(clk‘eventandclk=’1’)then

if(count(3downto0)=”1001”)then

if(count<16#A0#)then

if(count=”10011001”)then

ensec<=’1’;

count<=”00000000”;ELSE

count<=count+7;

endif;

else

count<=”00000000”;

endif;

elsif(count<16#A0#)then

count<=count+1;

ensec<=’0’;

else

count<=”00000000”;

endif;

endif;

endprocess;

ENDfun;

三、秒模块:

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYsecondIS

port(

clk,reset,setsec:

INSTD_LOGIC;

enmin:

OUTSTD_LOGIC;

daout:

outstd_logic_vector(6downto0));

ENDentitysecond;

ARCHITECTUREfunOFsecondIS

SIGNALcount:

STD_LOGIC_VECTOR(6downto0);

begin

daout<=count;

process(clk,reset,setsec)

begin

if(reset=’0’)then

count<=“0000000”;

elsif(setsec=’0’)then

elsif(clk’eventandclk=’1’)then

if(count(3downto0)=”1001”)then

if(count<16#60#)then

if(count=”1011001”)then

enmin<=’1’;

count<=”0000000”;ELSE

count<=count+7;

endif;

else

count<=”0000000”;

endif;

elsif(count<16#60#)then

count<=count+1;

enmin<=’0’;--

else

count<=”0000000”;

endif;

endif;

endprocess;

ENDfun;

四、分钟模块

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYminuteIS

port(

clk,reset,setmin:

INSTD_LOGIC;

daout:

outstd_logic_vector(6downto0));

ENDentityminute;

ARCHITECTUREfunOFminuteIS

SIGNALcount:

STD_LOGIC_VECTOR(6downto0);

begin

daout<=count;

process(clk,reset,setsec)

begin

if(reset=’0’)then

count<=“0000000”;

elsif(setmin=’0’)then

elsif(clk’eventandclk=’1’)then

if(count(3downto0)=”1001”)then

if(count<16#60#)then

if(count=”1011001”)then

count<=”0000000”;

else

count<=count+7;

endif;

else

count<=”0000000”;

endif;

elsif(count<16#60#)then

count<=count+1;

else

count<=”0000000”;

endif;

endif;

endprocess;

ENDfun;

五、数码管模块

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

ENTITYzhishiIS

port

(clk1,reset:

INSTD_LOGIC;

msec,sec:

INSTD_LOGIC_VECTOR(6downto0);

minute:

instd_logic_vector(6downto0);

daout:

OUTSTD_LOGIC_vector(3downto0);

sel:

outstd_logic_vector(2downto0));

ENDzhishi;

ARCHITECTUREfunOFzhishiIS

SIGNALcount:

STD_LOGIC_vector(2downto0);--?

begin

sel<=count;

process(clk1,reset)

begin

if(reset=’0’)then

count<=“000”;

elsif(clk1‘eventandclk1=’1’)then

if(count>=“101”)then

count<=“000”;

else

count<=count+1;

endif;

endif;

casecountis

when“000”=>daout<=msec(3downto0);--?

when“001”=>daout(3)<=‘0’;

daout(2downto0)<=msec(6downto4);

when“010”=>daout<=sec(3downto0);

when“011”=>daout(3)<=‘0’;

daout(2downto0)<=sec(6downto4);

when“100”=>daout<=minute(3downto0);

whenothers=>daout(3)<=‘0’;

daout(2downto0)<=minute(6downto4);

endcase;

endprocess;

endfun;

附录3:

仿真波形

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 作业 秒表

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《酒店人力资源管理》教案.docx

《酒店人力资源管理》教案.docx