东北大学微机原理考试复习题.docx

东北大学微机原理考试复习题.docx

- 文档编号:23750645

- 上传时间:2023-05-20

- 格式:DOCX

- 页数:21

- 大小:61.46KB

东北大学微机原理考试复习题.docx

《东北大学微机原理考试复习题.docx》由会员分享,可在线阅读,更多相关《东北大学微机原理考试复习题.docx(21页珍藏版)》请在冰豆网上搜索。

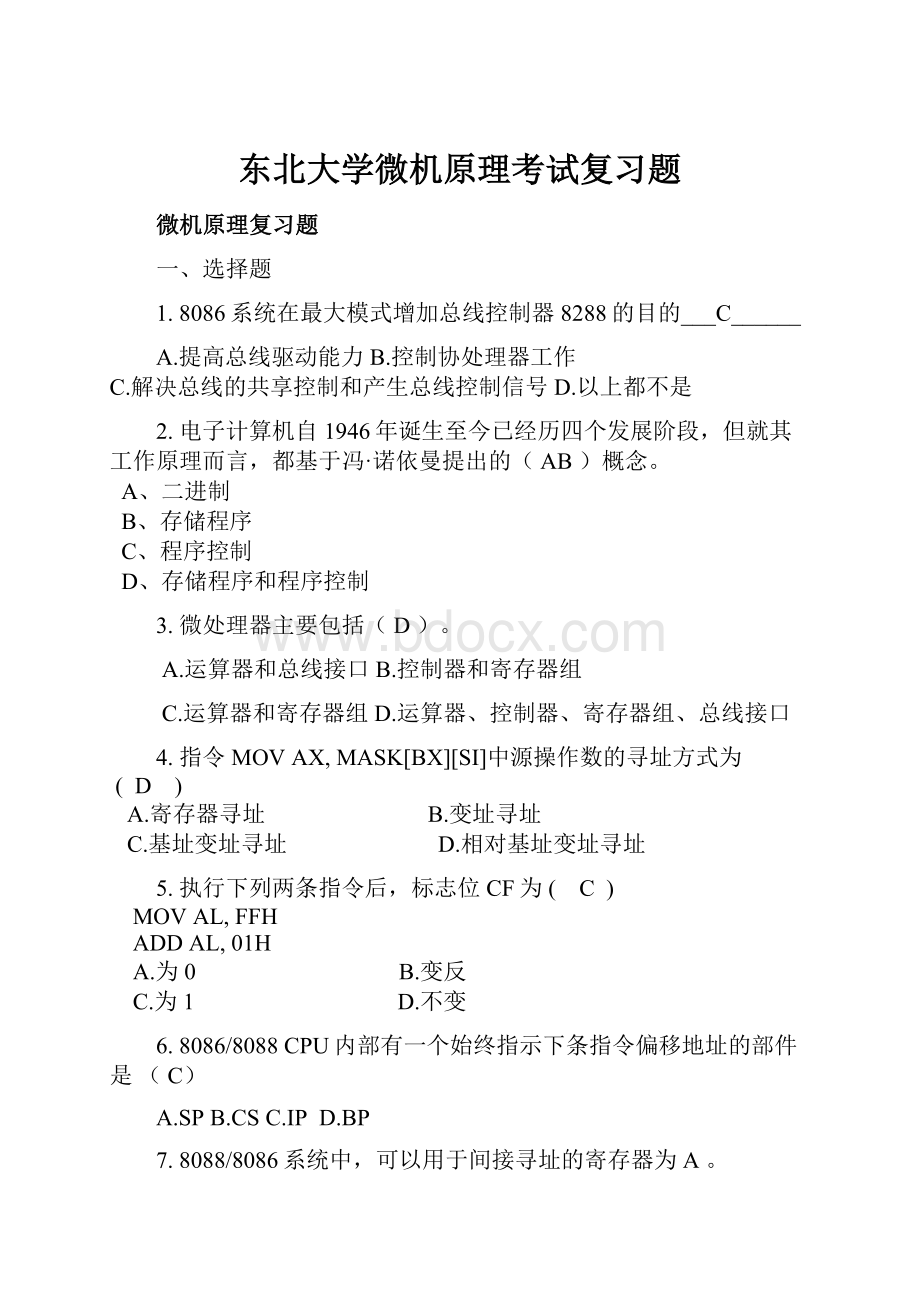

东北大学微机原理考试复习题

微机原理复习题

一、选择题

1.8086系统在最大模式增加总线控制器8288的目的___C______

A.提高总线驱动能力B.控制协处理器工作

C.解决总线的共享控制和产生总线控制信号D.以上都不是

2.电子计算机自1946年诞生至今已经历四个发展阶段,但就其工作原理而言,都基于冯·诺依曼提出的(AB)概念。

A、二进制

B、存储程序

C、程序控制

D、存储程序和程序控制

3.微处理器主要包括(D)。

A.运算器和总线接口B.控制器和寄存器组

C.运算器和寄存器组D.运算器、控制器、寄存器组、总线接口

4.指令MOV AX, MASK[BX][SI]中源操作数的寻址方式为 ( D )

A.寄存器寻址 B.变址寻址

C.基址变址寻址 D.相对基址变址寻址

5.执行下列两条指令后,标志位CF为 ( C )

MOV AL, FFH

ADD AL, 01H

A.为0 B.变反

C.为1 D.不变

6.8086/8088 CPU内部有一个始终指示下条指令偏移地址的部件是 (C)

A.SPB.CSC.IP D.BP

7.8088/8086系统中,可以用于间接寻址的寄存器为A。

A.BX,SI,DI,BPB.AX,SI,CX,BPC.AX,BX,CX,DX

8.在DMA方式下,将内存数据传送到外设的路径是 ( B )

A.CPU→DMAC→外设 B.内存→数据总线→外设

C.内存→CPU→总线→外设 D.内存→DMAC→数据总线→外设

9.从8086CPU的内部结构看,其是由C两部分组成

A.控制器和20位物理地址加法器B.运算器和总线接口

C.执行单元和总线接口单元D.控制器和运算器

10.RESET信号有效后,8086CPU的启动地址C。

A.0FFFFFHB.0FFFFHC.0FFFF0HD.00000H

11.CPU响应INTR和NMI中断时,相同的必要条件是 ( A )

A.当前指令执行结束 B.允许中断

C.当前访问内存结束 D.总线空闲

12.通常,中断服务程序中的一条STI指令目的是 ( D )

A.允许低一级中断产生 B.开放所有可屏蔽中断

C.允许同级中断产生 D.允许高一级中断产生

13.指令MOVAX,[3070H]中源操作数的寻址方式为C。

A.寄存器间接寻址B.立即寻址C.直接寻址D.变址寻址

14.8088 CPU用来区分是访问内存还是访问I/O端口的控制信号是 ( C )

A.MRDC(非) B.RD(非)

C.M(非)/IO D.M/IO(非)

15.CPU与外设间数据传送的控制方式有( D)

A.中断方式 B.DMA方式

C.程序控制方式 D.以上三种都是

16.下列哪种表示正确_____B____。

A.有效地址确定内存单元在整个寻址范围内的位置

B.物理确定内存单元在整个寻址范围内的位置

C.偏移地址确定内存单元在整个寻址范围内的位置

D.有效地址就是物理地址

17.8086CPU内标志寄存器中的控制标志位占( C)

A.9位 B.6位

C.3位 D.16位

18.8086CPU中,(B)引脚信号是决定最大或最小工作模式的控制信号。

A、M/IO B、MN/MX C、DT/R D、BHE/S7

19.8086系统中,中断优先级最低的是D。

A.INTnB.NMIC.INTRD.单步中断

20.主机与外设传送数据时,采用____C_____,CPU的效率最高。

A.程序查询方式B.中断方式C.DMA方式D.同步方式

21.8086CPU对I/O接口编址采用C。

A、I/O端口和存储器统一编址B、I/O端口和寄存器统一编址

C、I/O端口单独编址D、输入和输出口分别编址

22.下列那种方法可用于存放在AX和[BX]内两个无符号数比较B。

A.执行CMPAX,[BX]指令,根据S标志位判断两个数大小

B.执行CMPAX,[BX]指令,根据C标志位判断两个数大小

C.执行CMPAX,[BX]指令,根据O和S标志位判断两个数大小

D.执行CMPAX,[BX]指令,根据O标志位判断两个数大小

23.CPU响应中断请求和响应DMA请求的本质区别是( B )

A.中断响应靠软件实现

B.响应中断时CPU仍然仍控制总线,而响应DMA请求时,CPU要让出总线

C.速度慢

D.控制简单

24.关于内部中断的叙述哪个是正确的_____B_______。

A.中断源来自INTR引脚的硬件信号

B.执行INTn软中断指令后,可以产生一次内部中断

C.内部中断服务程序入口地址不需要存放在中断向量表内

D.CLI指令可以关闭内部中断

25.堆栈的工作方式是( D)

A.先进先出 B.随机读写

C.只能读出,不能写入 D.后进先出

26.在下列伪指令中定义字节变量的是(A)。

A)DBB)DWC)DDD)DT

27.在异步通信方式中,通信双方能同时进行收发的传送方式,称为( C )

A.单工通信方式

B.半双工通信方式

C.全双工通信方式

D.并行通信方式

28.指令(C)的源操作数的寻址方式为直接寻址。

A)MOV[2000H],ALB)INAL,DX

C)XORAL,[2000H]D)MOVAX,2000H

29.8086在响应外部HOLD请求后,(D)。

A)转入特殊中断服务程序B)进入等待周期

C)只接收外部数据D)所有三态引脚处于高阻,CPU放弃对总线控制权。

30.现行数据段位于存储器BOOOOH到BOFFFH字节单元,则段寄存器DS的内容及该段长度(字节数)分别为:

(C)

A)BOOOH,1000HB)O0OOH,OFFFHC)BOOOH,OFFFHD)BOOOH,OOFFH

31.在远距离串行数据传输中,接收端配置MODEM是为了( C )

A.将串行数据转换成并行数据

B.进行电平转换

C.把模拟信号转换成数字信号

D.提高传输速率

32.8086在最小模式下,分时使用AD0-AD15,所以必须外接地址锁存器,当总线上为地址信息时,通过(B)将地址送入地址锁存器。

A)DENB)ALEC)BHED)DT/R

33.程序查询流程总是按(A)次序完成一个字符的传输。

A.读状态端口,写数据端口B.写数据端口,读状态端口,写数据端口

C.写控制端口,读状态端口,写数据端口D.随I/O接口的具体要求而定

34.8086/8088CPU响应硬件中断INTR请求的必要条件除IF=1外,还需满足(B)。

A.访存储器操作结束B.当前指令执行完

C.无软件中断请求D.无内部中断请求

35.8088/8086系统中,可以用于间接寻址的寄存器为(A)。

A.BX,SI,DI,BPB.AX,SI,CX,BPC.AX,BX,CX,DX

36.CPU与I∕O设备间传送的信号有____D_________。

A.数据信息 B.控制信息C.状态信息 D.以上三种都是

37.CPU进行中断处理,保留断点时,共占用堆栈区(B)字节。

A.6个B.4个C.2个

38.如果AL的内容为50H,执行TESTAL,01H指令后,AL的内容为(C)。

A.49HB.4FHC.50HD.01H

39.8086CPU包括B。

A.运算器、控制器和存储器B.运算器、控制器和寄存器

C.运算器、控制器和接口部件D.运算器、控制器和累加器

40.8086的I/O寻址空间为C字节。

A.1024个B.1M个C.64K个D.32K个

34.以下说法中,D是错误的。

A.逻辑段允许在整个存储空间内浮动。

B.一个程序可以有代码段、数据段和堆栈段。

C.段与段之间可以连续,也可以重叠。

D.段与段之间可以连续,不可以重叠。

35.中断向量可以提供___C___。

A.被选中设备的起始地址B.传送数据的起始地址

C.中断服务程序入口地址D.主程序的断点地址

36.在中断响应周期内,将IF置0是由___A____来处理的。

A.硬件自动完成的B.用户在编制中断服务程序时设置的C.关中断指令完成的

37.一片8259A只占两个I/O地址,可以用地址码A1来选择端口,如果其中一个端口地址

为92H,则另一个端口地址为_____A_____。

A.90HB.91HC.93HD.94H

38.当多片8259A级联使用时,对于主8259A,信号CAS0~CAS是__B______。

A.输入信号B.输出信号C.输入/输出信号

39.8259A中的中断服务寄存器用于B。

A.指示外设向CPU发中断申请B.指示有中断正在进行C.开放或关闭中断系统

40.通常情况下,一个外中断服务程序的第一条指令是STI,其目的是____C_____.

A.开放所有的屏蔽中断B.允许低一级中断产生C.允许高一级中断产生D.允许同一级中断产生

41.PC采用向量中断方式处理8级中断,中断号依次是08H~0FH,在RAM中0:

2CH单元依次存放23H、FFH、00H和F0H四个字节,该向量对应的中断号好中断程序入口地址是__B_____。

A.0CH,23FF:

00F0HB.0BH,F000:

FF23H

C.0BH,00F0:

23FFHD.0CH,F000:

FF23H

42.CPU响应外部中断请求是___A_____。

A.在一条指令执行结束时B.在一个机器周期结束时C.一旦请求,立即响应D.由中断类型码n引起

43.IF可以屏蔽的中断类型有___C____。

A.内部中断B.外部中断

C.外部中断的可屏蔽中断D.外部中断和内部中断均可屏蔽

44.在DMA方式下,CPU与总线的关系是___C________。

A.只能控制数据总线B.只能控制地址总线

C.成隔离状态D.成短接状态

45.软中断INTn(n=10~FFH)的优先级排列原则是D。

A.n值越小级别越高B.无优先级别

C.n值越大级别越高D.随应用而定

二、填空题

1.8086 CPU通过

(1)CS寄存器和

(2)IP寄存器能准确找到指令代码。

2.8086从功能上分为两部分:

总线接口单元和(4)执行单元。

3.8086输入输出指令间接寻址必须通过DX寄存器。

4.总线周期是指每当CPU要从存储器或I/O端口存取一个字节就是一个总线周期。

一个总线周期通常包括4个时钟周期。

5.打印机是输出设备,扫描仪是输入设备。

6.从CPU的NMI引脚产生的中断叫做非屏蔽中断,它的响应不受可屏蔽中断控制位IF的影响。

7.8086CPU访问存储器的读写规则是以字为单位进行,并且均从偶地址开始。

8.设当前的SP=2000H,执行PUSHAX指令后,SP=(10)1FFEH,若改为执行IRET指令后,则SP=__(11)___2000_____H。

9.外设与CPU交换数据主要有以下几种(12)程序控制(无条件、查询、中断)方式和DMA方式;其中(13)_____DMA_____方式速度最快

10.模/数转换时,若输入模拟信号的最高有效频率为20kHz,采样频率最小为(14)40kHz,应选用转换时间为(15)25us的A/D转换器。

9.8086CPU内部数据总线宽度为___16___位,外部数据总线宽度为___16___位。

10.8088CPU内部数据总线宽度为___16___位,外部数据总线宽度为__8____位。

11.8086CPU地址总有__20__位,寻址范围是__1M字节____。

12.当存储器的读出时间大于CPU所要求的时间,为保证CPU与存储器的周期配合,就需要用___READY_____信号,使CPU插入一个__TW___状态。

13.若访问存储器对堆栈进行操作,段基值一般来源于___SS_寄存器,偏移量来源于__SP__寄存器

14.中断返回的指令是IRET,关中断的指令是CLI。

15.类型码为___16H____的中断所对应的中断向量存放在0000H:

0058H开始的4个连续单元中,若这4个单元的内容分别为___80H,70H,60H,50H____,则相应的中断服务程序入口地址为5060H:

7080H。

16.如CS:

IP=0100H:

0100H,则物理地址为01100H。

17..CPU 在指令的最后一个时钟周期检测INTR引脚,若测得INTR为____高电平_____且IF为__1__,则CPU在结束当前指令后响应中断请求。

18.执行XORAX,AX后,AX寄存器的值为0。

19.CPU从I/O接口的状态寄存器中获取外设的“忙”,“空闲”和“准备好”等信息,而从I/O接口的控制寄存器向外设发“启动”或“停止”等信号。

20.指令MOVBX,0中的源操作数为(立即)寻址,指令执行后ZF为

(1)。

21.一个中断类型码为71H的中断服务程序存放在0000H:

0200H开始的内存中,则中断服务程序入口地址IP值将填入中断向量表(①1C4)H至(②1C5)H单元中。

若需进行中断嵌套,则应在中断服务程序中设置(③STI)指令,且最后一条指令为(④IRET)。

22.在OUT50H,AL指令的执行中,一定有一个(①I/O端口写)总线周期,在该总线周期内,地址总线上传送的是(②50H)地址,控制线(③WR和IO/M)有效。

23.8086中地址/数据线分时复用,为保证总线周期内地址稳定,应配置(3)地址锁存器,为提高总线驱动能力,应配置(4)总线驱动器

26.在8086CPU中,总线接口部件(BIU)的功能是负责与M、I/O端口传送数据,执行部件(EU)的功能是负责指令的执行。

28.在8086/8088最小模式中,总线控制信号是由CUP产生,而在最大模式中,总线控制信号是由总线控制器产生。

29.堆栈是按照先进后出原则组织的一段内存区域,指针SP始终指向堆栈段的顶部(栈顶)。

30.8086系统中,主频若为10MHz,一个基本的总线周期为0.00000004秒。

31.已知某存储单元的段基值为2500H,偏移地址为3600H,该单元的物理地址是28600H。

32.CPU响应中断需满足三个条件:

在现行指令周期内无总线请求;(中断允许标志IF=1;现行指令执行完毕

33.硬件中断可分为可屏蔽中断和非屏蔽中断两种。

34.CPU响应可屏蔽中断的条件是IF=1、有中断请求、现行指令执行完毕。

35.8259A有两种中断触发方式,分别是电平触发方式和边沿触发方式。

36.8259A可编程控制器,当其单片使用时可同时接受__8__个外设的中断请求;当级联使用时,其主片的IR端应与从片的INT连接。

37.若外设的中断类型码为3AH,则该中断源的中断请求信号应连在8259A的IR2端,且对应的中断向量地址为00E8H。

38.CPU与I/O接口间的信息一般包括数据信息、状态信息和控制信息3种类型。

39.一般I/O端口的编址方式可分为单独编址和统一编址。

三、简答题

1.8086/8088的最大和最小模式工作模式由什么决定?

两种工作模式的最主要的区别?

答:

最大和最小模式由MN/MX引脚决定。

MN/MX引脚接高电平工作在最小模式,接地工作在最大工作模式。

2.什么是指令周期?

总线周期?

时钟周期?

说明三者之间的关系。

答:

CPU执行一条指令的时间(包括取指令和执行指令所需的全部时间)称为指令时间;CPU通过外部总线对存储器或I/O端口进行一次读/写操作的过程称为总线周期;系统主时钟频率的倒数称为时钟周期。

一个指令周期由若干个总线周期组成,而一个总线周期由若干个时钟周期组成。

3.在8086/8088系统中,存储器是怎样组织的?

整个存储空间有多大?

最大逻辑长度为多大?

至少可将存储器分为多少个段?

段起始于什么位置?

偏移地址是什么?

怎样计算20位物理地址?

①分段组织②1兆字节③64K字节④至少分成16段⑤起始于最后四位二进制数都为0的位置⑥偏移地址是相当于段起始位置的偏移量⑦段地址×16+偏移地址

4.系统总线分为哪几组?

各自传送的方向如何?

①分成3组:

数据部线、地址总线、控制总线②数据总线和控制总线都是双向的,地址总线始终由CPU发出

5.8086微处理器分为哪几个部分?

它们之间采用什么工作方式?

其中状态寄存器由几类标志组成?

与中断有关的是哪一位?

①分成2部分:

总线接口部件、执行部件②并行工作方式③2类:

状态标志、控制标志④IF位,IF置1,响应外部可屏蔽中断

6.复位信号RESET到来后,8086/8088CPU的内部状态有何特征?

系统从何处开始执行指令?

答:

RESET复位信号来到后,CPU便结束当前操作,并对处理器标志寄存器、IP、DS、SS、ES及指令队列清零,而将CS设置为FFFFH。

当复位信号变为低电平时,CPU从FFFF0H开始执行程序。

7.8086系统中为什么一定要有地址锁存器?

需要锁存哪些信息?

答:

8086/8088CPU的地址/数据和地址/状态总线是分时复用总线,即CPU在进行总线操作时,总是在T1状态首先送出访问存储器或I/O端口的地址信息,随后又用这些引脚传送数据和状态信号,而对存储器或I/O端口进行读/写操作时,要求在整个读/写总线周期内保持地址稳定。

因而地址信息必须锁存。

除20位地址信息外BHE信号也要锁存。

8.CPU的READY和RESET信号有什么作用?

答:

READY“准备好”信号输入:

用于解决CPU与外设的速度匹配,RESET复位信号输入,复位信号来到后,CPU便结束当前操作,并对处理器标志寄存器、IP、DS、SS、ES及指令队列清零,而将CS设置为FFFFH。

当复位信号变为低电平时,CPU从FFFF0H开始执行程序。

9.8086和8088怎样解决地址线和数据线的复用问题的?

ALE信号何时处于有效电平?

10.什么是接口?

什么是端口?

接口有哪些功能?

接口中传送的信息有哪几类?

答:

(1)I/O接口是位于系统与外设间、用来协助完成数据传送和控制任务的逻辑电路。

(2)接口中那些CPU可直接访问的寄存器又被称为I/O端口(Port)、外设端口或端口。

一个接口中包含多个端口,如数据端口、状态端口和控制端口。

一般数据端口可被CPU进行读写操作,而状态端口则只能读,控制端口只能写。

(3)传送信息有三类:

1.数据信息,一般由外设通过接口传递给系统的。

2.状态信息,由外设通过接口往CPU传送的。

3.控制信息,是CPU通过接口传送给外设的。

11.CPU与外设之间的输入输出数据传输方式有哪几种?

何谓程序控制方式?

它有哪几种基本方式?

实际选择某种传送方式的最主要的依据是什么?

答:

程序控制方式(包括无条件传送、查询方式、中断方式)和DMA方式。

程序控制方式是指CUP依靠执行一定的指令代码完成与外设间的输入输出。

程序控制方式包括无条件传送方式、状态查询传送方式和中断传送方式。

选择的依据主要包括实时性、数据量、CPU利用率以及传输速度等要求。

12.I/O端口的寻址方式有哪些?

在8086/8088微机系统中,CPU是如何实现对I/O端口寻址的?

答:

I/O端口的编址方式有两种:

I/O端口和存储器统一编址,I/O端口独立编址。

Intel8086就是采用的独立编址方式,访问存储器用MOV指令,而输入输出则使用专用的I/O指令:

从I/O端口输入用IN,向端口输出用OUT。

13.逻辑地址与物理地址是如何定义的?

差别在那里?

答:

逻辑地址是由段基址和段内偏移地址组成的地址。

段基址和段内偏移地址都是16位的无符号二进制数,在程序设计时使用。

物理地址:

存储器的绝对地址(20位的实际地址),范围从00000H~FFFFFH,是由CPU访问存储器时由地址总线发出的地址。

每个存储单元只有唯一的物理地址。

但可由不同的段地址和不同的偏移地址组成,即逻辑地址可以不同。

14.8086指令队列的作用是什么?

答:

在执行指令的同时从内存中取了一条指令或下几条指令,取来的指令放在指令队列中这样它就不需要象以往的计算机那样让CPU轮番进行取指和执行的工作,从而提高CPU的利用率。

15.什么是中断向量?

中断向量表是什么?

非屏蔽中断的类型为多少?

8086中断系统优先级顺序怎样?

答:

①所谓中断响量,实际上就是中断处理子程序的入口地址,每个中断类型对应一个中断响量

②中断向量按照中断类型的顺序在内存0段0单元开始有规则排列的一张表③类型02H

④内部中断>非屏蔽中断>可屏蔽中断>单步中断

16.8259有几种中断结束方式?

应用场合如何?

答:

1.中断自动结束方式,不需要设置中断结束命令,在单片系统中且不会出现中断嵌套时用。

2.一般中断结束方式,在全嵌套方式下用。

3.特殊中断结束方式,在任何场合均可使用。

17.在一个8086CPU和单片8259A组成的系统中,试说明:

(1)8086CPU在响应可屏蔽中断的条件是什么?

(2)8086CPU在响应中断过程中,连续执行两个INTA周期,其作用是?

(3)假如8259A已被编程,ICW2=0AH,若连接在8259A的IR3端的外设提出中断申请,它的中断向量的存放地址是什么?

答:

(1)8086/8088在当前指令执行完且IF=1的情况下可以响应一个外部INTR中断请求。

(2)8086/8088响应INTR中断请求时,首先在连续的两个总线周期中发出INTA#负脉冲,在第二个INTA#信号期间,中断源经数据总线向8088/8088进出一字节中断向量“类型码”

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 东北大学 微机 原理 考试 复习题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《公务员财产申报制度》.docx

《公务员财产申报制度》.docx