逻辑电路基础实验指导.docx

逻辑电路基础实验指导.docx

- 文档编号:23675721

- 上传时间:2023-05-19

- 格式:DOCX

- 页数:12

- 大小:39.29KB

逻辑电路基础实验指导.docx

《逻辑电路基础实验指导.docx》由会员分享,可在线阅读,更多相关《逻辑电路基础实验指导.docx(12页珍藏版)》请在冰豆网上搜索。

逻辑电路基础实验指导

基础实验部分

实验一集成逻辑门电路逻辑功能的测试

一、实验目的

1、熟悉数字逻辑实验箱的结构、基本功能和使用方法。

2、掌握常用非门、与非门、或非门、与或非门、异或门的逻辑功能及其测试方法。

二、实验仪器及设备

1、数字逻辑实验箱1台

2、元器件:

74LS0074LS0474LS2874LS86HD74LS86P各一块

导线若干

三、实验内容

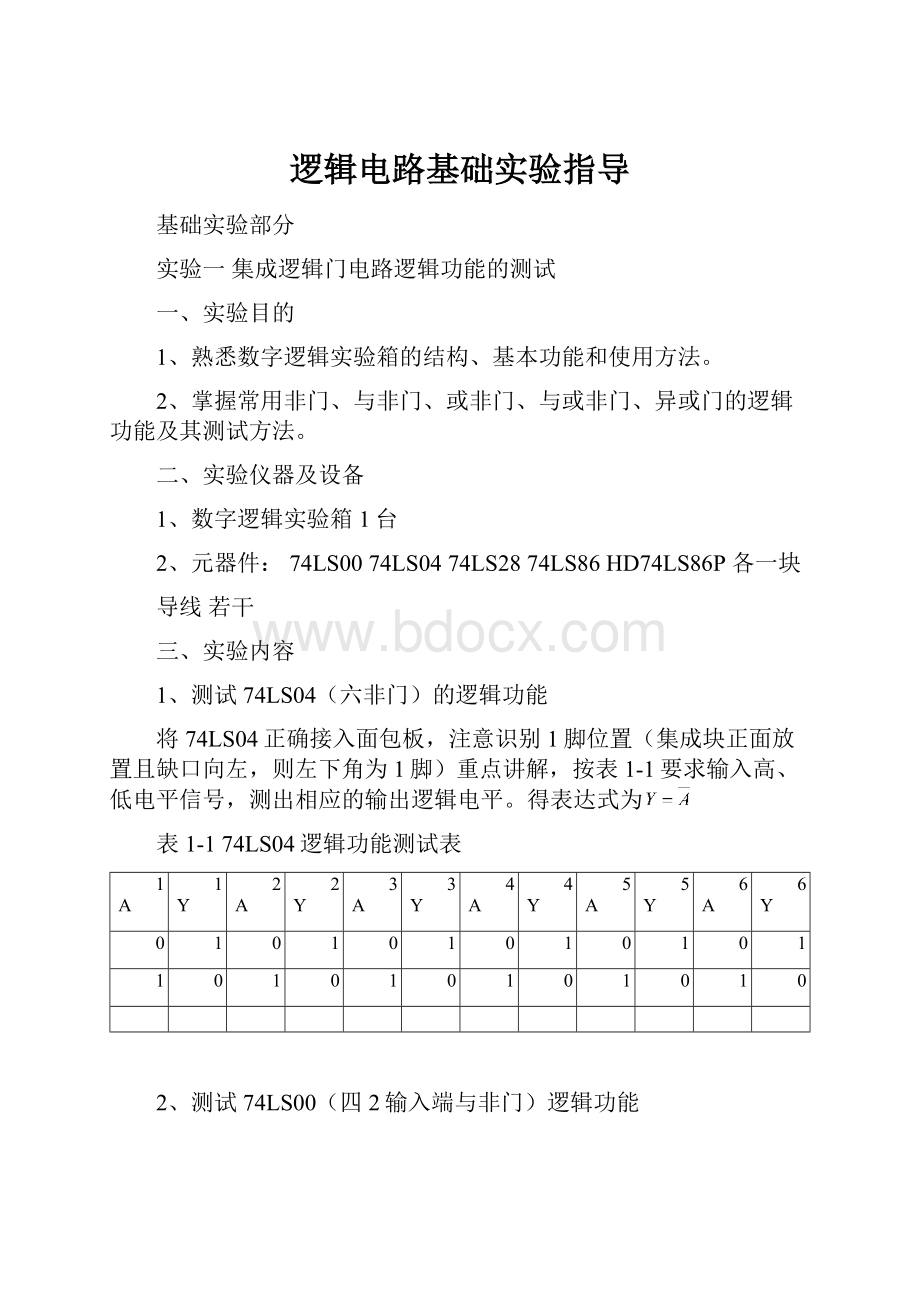

1、测试74LS04(六非门)的逻辑功能

将74LS04正确接入面包板,注意识别1脚位置(集成块正面放置且缺口向左,则左下角为1脚)重点讲解,按表1-1要求输入高、低电平信号,测出相应的输出逻辑电平。

得表达式为

表1-174LS04逻辑功能测试表

1A

1Y

2A

2Y

3A

3Y

4A

4Y

5A

5Y

6A

6Y

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

0

1

0

2、测试74LS00(四2输入端与非门)逻辑功能

将74LS00正确接入面包板,注意识别1脚位置,按表1-2要求输入高、低电平信号,测出相应的输出逻辑电平。

得表达式为

表1-274LS00逻辑功能测试表

1A

1B

1Y

2A

2B

2Y

3A

3B

3Y

4A

4B

4Y

0

0

1

0

0

1

0

0

1

0

0

1

0

1

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

3、测试74LS28(四2输入端或非门)逻辑功能

将74LS28正确接入面包板,注意识别1脚位置,按表1-3要求输入信号,测出相应的输出逻辑电平,填入表中。

(表中仅列出供抽验逻辑功能用的部分数据)

表1-374LS28逻辑功能测试表

1A

1B

1Y

2A

2B

2Y

3A

3B

3Y

4A

4B

4Y

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

本器件的逻辑表达式应为:

Y=

与实侧值相比较,功能正确。

4、测试74LS86(四异或门)逻辑功能

将74LS86正确接入面包板,注意识别1脚位置,按表1-4要求输入信号,测出相应的输出逻辑电平。

得表达式为Y=A⊕B

表1-474LS86逻辑功能测试表

1A

1B

1Y

2A

2B

2Y

3A

3B

3Y

4A

4B

4Y

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

四、实验结果分析(回答问题)

若测试74LS55的全部数据,所列测试表应有256种输入取值组合。

用实验箱、万用表作一个实验示范,并强调测试方法及万用表的用法。

实验二组合逻辑电路的实验分析

一、实验目的

1、学会组合逻辑电路的实验分析方法。

2、验证半加器、全加器的逻辑功能。

二、实验仪器及设备

1、数字逻辑实验箱1台

2、元器件:

74LS00、74LS04、74LS86、74LS28各一块

电阻及导线若干

三、实验线路图

四、实验内容

1、测试用与非门构成的电路的逻辑功能

按图3-1接线。

按下表要求输入信号,测出相应的输出逻辑电平,并填入表中。

分析电路的逻辑功能为半加器,写出逻辑表达式为:

Y=A⊕BZ=AB

2、测试用异或门和与非门组成的电路的逻辑功能

按图3-2接线。

按下表要求输入信号,测出相应的输出逻辑电平,并填入表中。

分析电路的逻辑功能为半加器,写出逻辑表达式为

Sn=A⊕BCn=AB

A

B

Y

Z

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

A

B

Sn

Cn

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

3、测试用异或门、非门和与或非门组成的电路的逻辑功能

按图3-3接线。

按下表要求输入信号,测出相应的输出逻辑电平,并填入表中。

分析电路的逻辑功能为半加器,写出逻辑表达式为:

Sn=A⊕B⊕CCn=AB+(A⊕B)C

An

Bn

Cn-1

Sn

Cn

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

五、实验结果分析(回答问题)

1、总结用实验来分析组合逻辑电路功能的方法为:

按图接线,将输入的所有取值组合对应输出测出来,得到该电路的真值表,进而写出逻辑函数表达式,概述电路的逻辑功能

实验三数据选择器

一、实验目的

1、进一步熟悉用实验来分析组合逻辑电路功能的方法。

2、了解中规模集成四选一数据选择器74LS153的应用。

3、了解组合逻辑电路由小规模集成电路设计和由中规模集成电路设计的不同特点

二、实验仪器及设备

1、数字逻辑实验箱1台

2、元器件:

74LS00、74LS04、74LS153

导线若干

三、实验线路图

四、实验内容(简单实验步骤、实验数据及波形)

1、利用数字逻辑实验箱测试74LS153四选一数据选择器的逻辑功能,按图5-1接线,将实验结果记录在下表中。

选通

地址输入

数据输入

输出

A1

A0

D0

D1

D2

D3

Y

1

X

X

X

X

X

X

0

1

0

0

0

D0

X

X

X

D0

0

1

X

D1

X

X

D1

1

0

X

X

D2

X

D2

1

1

X

X

X

D3

D3

用四选一数据选择器组成八选一数据选择器,用数字逻辑实验箱测试该八选一数据选择器的逻辑功能。

将实验结果记录在下表中:

选通

地址输入

数据输入

输出

A2

A1

A0

D0

D1

D2

D3

D4

D5

D6

D7

Y

1

X

X

X

X

X

X

X

X

X

X

X

0

1

0

0

0

0

D0

X

X

X

X

X

X

X

D0

0

0

1

X

D1

X

X

X

X

X

X

D1

0

1

0

X

X

D2

X

X

X

X

X

D2

0

1

1

X

X

X

D3

X

X

X

X

D3

1

0

0

X

X

X

X

D4

X

X

X

D4

1

0

1

X

X

X

X

X

D5

X

X

D5

1

1

0

X

X

X

X

X

X

D6

X

D6

1

1

1

X

X

X

X

X

X

X

D7

D7

交通灯红用R、黄用Y、绿用G表示,亮为1,灭为0。

只有当其中一只亮时为正常Z=0,其余状态均为故障Z=1。

该交通灯故障报警电路如图5-1,接线并检查电路的逻辑功能,将结果记录在下表中,可得表达式为:

Z(R,Y,G)=∑m(0,3,5,6,7)

R

Y

G

Z

0

0

0

1

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

3、有一密码电子锁,锁上有四个锁孔A、B、C、D,按下为1,否则为0,当按下A和B、或A和D、或B和D时,再插入钥匙,锁即打开。

若按错了键孔,当插入钥匙时,锁打不开,并发出报警信号,有警为1,无警为0。

设计出电路如图5-3,按图接线并检查电路的逻辑功能,列出表述其功能的真值表,记录实验数据如下表,可得表达式为:

F(AB,C,D)=∑m(0,1,2,3,4,6,7,8,10,11,13,14,15)

A

B

C

D

F

A

B

C

D

F

0

0

0

0

1

1

0

0

0

1

0

0

0

1

1

1

0

0

1

0

0

0

1

0

1

1

0

1

0

1

0

0

1

1

1

1

0

1

1

1

0

1

0

0

1

1

1

0

0

0

0

1

0

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

0

1

0

1

1

1

1

1

1

1

1

1

五、实验结果分析(回答问题)

1、由以上实验测试结果,可知74LS153四选一的功能正常。

2、用中规模集成电路设计逻辑函数的特点为:

较小规模集成电路更便于修改设计,且设计中多使用最小项表达式,设计思想可以更加清晰。

实验四触发器的功能及应用

一、实验目的

1、学会测试触发器逻辑功能的方法。

2、进一步熟悉RS触发器、集成JK触发器和D触发器的逻辑功能及触发方式。

3、进一步熟悉数字逻辑实验箱中单脉冲和连续脉冲发生器的使用方法。

二、实验仪器及设备

1、数字逻辑实验箱1台

2、双踪示波器XJ4328\XJ4318一台

3、元器件:

74LS00、74LS74、74LS73A各1块

导线若干

三、实验线路图

四、实验内容(简单实验步骤、实验数据及波形)

1、基本RS触发器逻辑功能测试

利用数字逻辑实验箱测试由与非门组成的基本RS触发器的逻辑功能,R、S接电平开关,Q、Q接电平显示,将结果记录在下表中。

步骤

Q

功能

0

0

0

1

1

不定

1

0

1

0

1

置0

2

1

1

0

1

保持

3

1

0

1

0

置1

4

1

1

1

0

保持

2、集成JK触发器逻辑功能测试

CP

J

K

×

1

1

1

1→0

0

1

1

0→1

0

1

1→0

1

1

0

0→1

1

1

0

1→0

1→0

1

1

0→1

0→1

0/1

1/0

(1)直接置0和置1端的功能测试

(2)JK逻辑功能的测试

按下表测试并记录JK触发器的逻辑功能(表中CP信号由实验箱操作板上的单次脉冲发生器提供)。

J

K

CP

0

0

0→1

0/1

0/1

1→0

0/1

0/1

0

1

0→1

0/1

0/1

1→0

0/1

0

1

0

0→1

0/1

0/1

1→0

0/1

1

1

1

0→1

0/1

0/1

1→0

0/1

1/0

(3)JK触发器计数功能测试

使触发器处于计数状态(J=K=1),CP信号由实验箱操作板中的连续脉冲(矩形波)发生器提供,可分别用低频(f=1~10HZ)和高频(f=20~150KHZ)两档进行输入,分别用实验箱上的LED电平显示器和XJ4328双踪示波器观察工作情况,记录CP与Q的工作波形,Q状态更新发生在CP的下降沿。

Q信号的周期是CP信号周期的两倍。

3、集成D触发器逻辑功能测试

(1)D触发器逻辑功能的测试

按下表测试并记录D触发器的逻辑功能(表中CP信号由实验箱操作板上的单次脉冲发生器提供)。

D

CP

0

0→1

0/1

0

1→0

0/1

0/1

1

0→1

0/1

1

1→0

0/1

0/1

(2)D触发器计数功能测试

使触发器处于计数状态(D=),CP端由实验箱操作板中的连续脉冲(矩形波)发生器提供,可分别用低频(f=1-10HZ)和高频(f=20-150KHZ)两档进行输入,分别用实验箱上的LED电平显示器和XJ4318/XJ4328双踪示波器观察工作情况,记录CP与Q的工作波形,Q状态更新发生在CP的上升沿。

Q信号的周期是CP信号周期的两倍。

五、实验结果分析(回答问题)

1、画出工作波形图。

2、比较各种触发器的逻辑功能及触发方式:

基本RS触发器:

置0、置1、保持功能,有不定状态;低电平触发。

JK触发器:

置0、置1、保持、计数功能,有低电平有效的直接置0、置1端;下降沿触发。

D触发器:

置0、置1、保持、功能,有低电平有效的直接置0、置1端;上升沿触发。

六、思考题

将一个带直接置0/1端的JK触发器置为0有以下几种方法:

CP

J

K

×

×

×

1

0

↓

0

1

1

1

↓(1次或2次)

1

1

1

1

将一个带直接置0/1端的JK触发器置为1有以下几种方法:

CP

J

K

×

×

×

1

0

↓

1

0

1

1

↓(1次或2次)

1

1

1

1

将一个带直接置0/1端的D触发器置为0有以下几种方法:

CP

D

×

×

1

0

↓

0

1

1

↓(1次或2次)

1

1

将一个带直接置0/1端的D触发器置为1有以下几种方法:

CP

D

×

×

0

1

↓

1

1

1

↓(1次或2次)

1

1

讲解小规模计数器的应用及组成原理。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 逻辑电路 基础 实验 指导

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《酒店人力资源管理》教案.docx

《酒店人力资源管理》教案.docx