cadence约束规则设计.docx

cadence约束规则设计.docx

- 文档编号:23671679

- 上传时间:2023-05-19

- 格式:DOCX

- 页数:12

- 大小:505.67KB

cadence约束规则设计.docx

《cadence约束规则设计.docx》由会员分享,可在线阅读,更多相关《cadence约束规则设计.docx(12页珍藏版)》请在冰豆网上搜索。

cadence约束规则设计

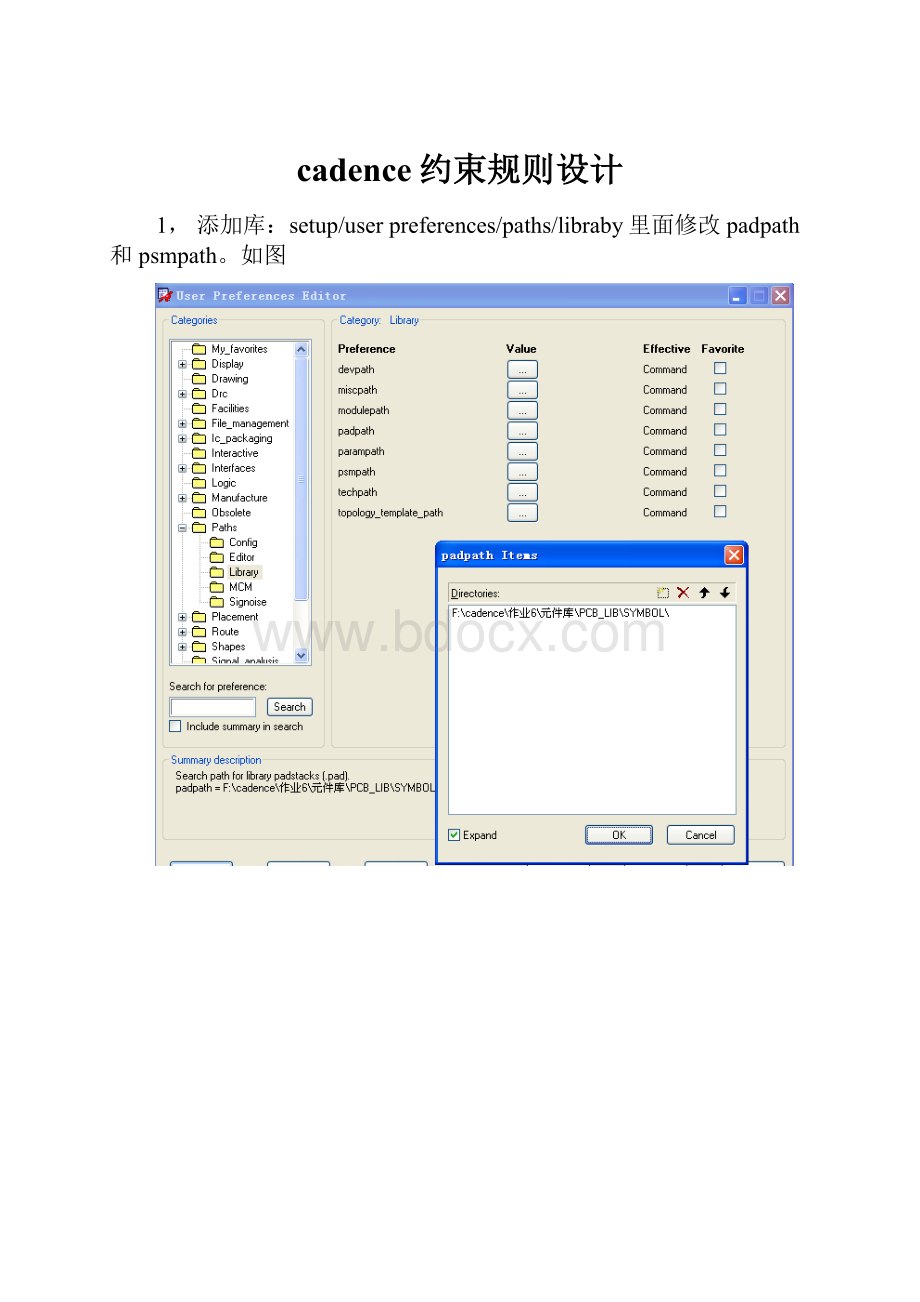

1,添加库:

setup/userpreferences/paths/libraby里面修改padpath和psmpath。

如图

2,线宽约束

默认线宽DEFUALT:

8mil,过孔选择:

VIA100-50-120

电源线宽:

20mil

Setup/constraints/physical/alllayersoption/create/physicalcset/LW_20MIL。

把电源网络,地线,晶振管脚设置成LW_20MIL

在net/alllayers下,将VCC12N,VCC12P,VCC1V2,VCC3V3,VCC5V,GND,GND1V2,CYVDD,OSC_POWER设置成LW_20MIL

LW_12MIL的线宽同上。

过孔为VIA60-35-95,将CS4272_LRCLK,CS4272_MCLK,CS4272_SCLK,DSP_CLKIN,MCBSP_CLKIN设置成LW_12MIL

3,线间距约束

在spacingconstraintsset/alllayers下创建Space_12mil和space_20mil属性。

option/create/spacingcset/space_12MIL和space_20mil。

在net/alllayers下

将CS4272_LRCLK,CS4272_MCLK,CS4272_SCLK,DSP_CLKIN,MCBSP_CLKIN设置成SPACE_12MIL。

将OSC_CLK,REFIN,REF_OUT,REF2_OUT,REF4_OUT设置为SPACE_20MIL。

4,Xnet设置

Analyze/SIEMIsim/modelbrowser,点击librarymgmt

点击setsearchpath后出现对话框,点击adddirectory,把minisystem中的sigxp.run加进来。

然后选中选中加进来的路径,点击checklib。

下一步,Analyze/SIEMIsim/modelassignment,对

的模型进行修改。

点击findmodel,选中RARRAY33,点击assign。

点击OK,Xnet设置完成。

5,设置总线

将EA2~EA20设置为ADDR_BUS,将ED0~ED31设置为DATA_BUS。

(选中后右击,create/bus就可以了)

6,T型拓扑

在约束管理器中的electrical/net/routing/wiring中,选中EA2,右击点sigXplorer。

在sigXplorer界面中画出拓扑结构。

然后set/constraints中的wiring里

然后set/constraints中的wiring里设置如下

然后选set/optionalpins,点击U8,右击END,将U8设置为可选器件。

最后点file/updateconstraintmanager.

在Electricalconstraintsset里把约束名字改为ECSET_ADDR.回来,选中EA3~EA20右击,constraintsetreferences,在对话框里选中ECSET_ADDR

数据总线T型拓扑同上。

7,线长约束

在Electricalconstraintsset里,右击地址总线,打开sigxplorer。

然后set/constraints中的propdelay里设置如下:

点击ADD。

然后OK。

然后file/updateconstraintmanager.

在net/ruting/min/maxpropdelays里可以看到设置后效果。

数据线设置同上。

Mindelay2000milmaxdelay:

3000mil

8,相对延迟

在Electricalconstraintsset里,右击地址总线,打开sigxplorer。

然后set/constraints中的relpropdelay里设置如下:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- cadence 约束 规则 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《酒店人力资源管理》教案.docx

《酒店人力资源管理》教案.docx

民宿酒店项目融资商业计划书PPT文档格式.pptx

民宿酒店项目融资商业计划书PPT文档格式.pptx