eda程序.docx

eda程序.docx

- 文档编号:23608944

- 上传时间:2023-05-19

- 格式:DOCX

- 页数:18

- 大小:32.64KB

eda程序.docx

《eda程序.docx》由会员分享,可在线阅读,更多相关《eda程序.docx(18页珍藏版)》请在冰豆网上搜索。

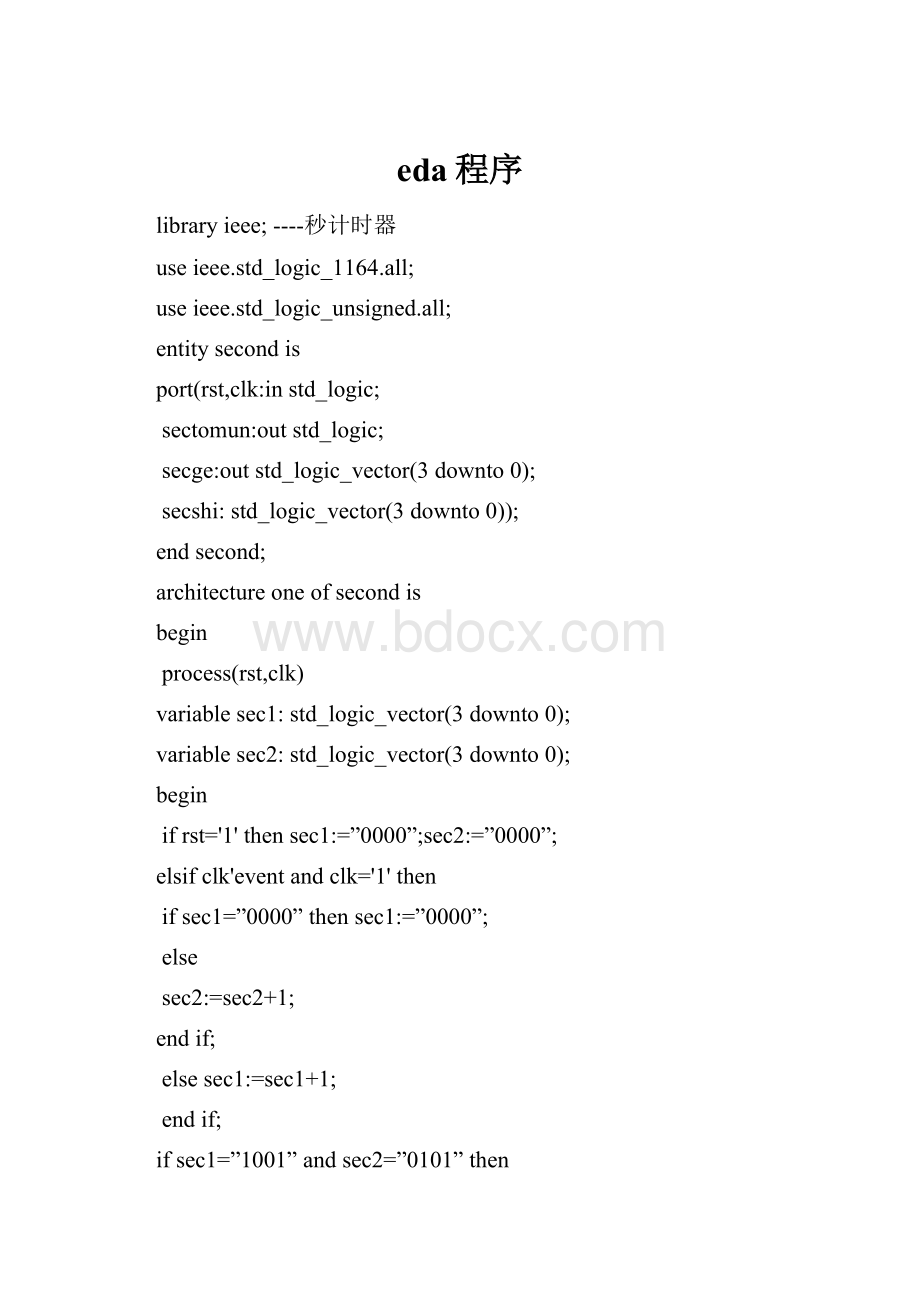

eda程序

libraryieee;----秒计时器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitysecondis

port(rst,clk:

instd_logic;

sectomun:

outstd_logic;

secge:

outstd_logic_vector(3downto0);

secshi:

std_logic_vector(3downto0));

endsecond;

architectureoneofsecondis

begin

process(rst,clk)

variablesec1:

std_logic_vector(3downto0);

variablesec2:

std_logic_vector(3downto0);

begin

ifrst='1'thensec1:

=”0000”;sec2:

=”0000”;

elsifclk'eventandclk='1'then

ifsec1=”0000”thensec1:

=”0000”;

else

sec2:

=sec2+1;

endif;

elsesec1:

=sec1+1;

endif;

ifsec1=”1001”andsec2=”0101”then

sectomun<='1';

elsesectomun<='0';

endif;

endif;

endprocess;

secge<=sec1;

secshi<=sec2;

end;

libraryieee;--分计时器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityminuteis

port(rst:

instd_logic;

sectomun:

instd_logic;

muntohour:

outstd_logic;

munge:

outintegerrange0to9;

munshi:

outintegerrange0to5);

endminute;

architectureoneofminuteis

begin

process(rst,sectomun)

variablemun1:

integerrange0to9;

variablemun2:

integerrange0to5;

begin

ifrst='1'thenmun1:

=0;mun2:

=0;

elsifsectomun'eventandsectomun='1'then

mun1:

=mun1+1;

ifmun1=10thenmun1:

=0;

mun2:

=mun2+1;

endif;

ifmun2=6thenmun2:

=0;

muntohour<='1';

else

muntohour<='0';

endif;

endif;

munge<=mun1;

munshi<=mun2;

endprocess;

end;

libraryieee;---小时计时器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityhouris

port(rst:

instd_logic;

muntohour:

instd_logic;

hourge:

outintegerrange0to9;

hourshi:

outintegerrange0to2);

endhour;

architectureoneofhouris

begin

process(rst,muntohour)

variablehour1:

integerrange0to9;

variablehour2:

integerrange0to2;

begin

ifrst='1'thenhour1:

=0;hour2:

=0;

elsifmuntohour'eventandmuntohour='1'then

hour1:

=hour1+1;

ifhour1=10thenhour1:

=0;

hour2:

=hour2+1;

endif;

ifhour1=4andhour2=2then

hour1:

=0;hour2:

=0;

endif;

endif;

hourge<=hour1;

hourshi<=hour2;

endprocess;

end;

libraryieee;-----设置时钟

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitysettimeis

port(s1,s0:

instd_logic;

hourge,munge:

bufferintegerrange0to9;

hourshi:

bufferintegerrange0to2;

munshi:

bufferintegerrange0to5);

endentitysettime;

architectureoneofsettimeis

signalsets:

std_logic_vector(1downto0);

begin

sets<=s0&s1;---相并;

process(sets)

variablehn1,min1:

integerrange0to9;

variablehn2:

integerrange0to2;

variablemin2:

integerrange0to5;

begin

casesetsis

when"01"=>hourshi<=hn2;hourge<=hn1;

when"10"=>munshi<=min2;munge<=min1;

when"11"=>hourshi<=hn2;hourge<=hn1;munshi<=min2;munge<=min1;

whenothers=>null;

endcase;

endprocess;

end;

libraryieee;-----7段译码器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityled_7is

port(ain:

inintegerrange0to9;

led7s:

outstd_logic_vector(0to6));

endentityled_7;

architecturebehavofled_7is

begin

process(ain)

begin

caseainis

when0=>led7s<="1111110";

when1=>led7s<="0110000";

when2=>led7s<="1101101";

when3=>led7s<="1111001";

when4=>led7s<="0110011";

when5=>led7s<="1011011";

when6=>led7s<="1011111";

when7=>led7s<="1110010";

when8=>led7s<="1111111";

when9=>led7s<="1111011";

whenothers=>led7s<="0000000";

endcase;

endprocess;

endbehav;

libraryIEEE;----分频计

useIEEE.std_logic_1164.all;

useIEEE.std_logic_arith.all;

useIEEE.std_logic_unsigned.all;

entityfenpinis

port(rst,clk:

inSTD_LOGIC;

pin:

outSTD_LOGIC);

endfenpin;

architectureaoffenpinis

signalcount:

integerrange0to4;

signalt:

std_logic;

begin

process(rst,clk)

begin

ifrst='1'thencount<=0;

elsifclk'eventandclk='1'then

count<=count+1;t<=t;

ifcount=4thencount<=0;t<=nott;

endif;

endif;

pin<=t;

endprocess;

enda;

libraryieee;----闹钟

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityalarmis

port(pin,muntohour:

instd_logic;

alarm:

outstd_logic);

endentityalarm;

architectureoneofalarmis

begin

process(muntohour,pin)

begin

ifmuntohour='1'then

alarm<=pin;

elsealarm<='0';

endif;

endprocess;

end;

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityshuzizhongis

port(RST_T,CLKK:

instd_logic;

S1,S0:

instd_logic;

ALARM1:

outstd_logic;

SEC_1,MIN_1,HOUR_1:

bufferintegerrange0to9;

SEC_2,MIN_2:

bufferintegerrange0to5;

HOUR_2:

bufferintegerrange0to2;

LEDXS:

outstd_logic_vector(0to6));

endentityshuzizhong;

architectureoneofshuzizhongis

componentsecond

port(rst,clk:

instd_logic;

sectomun:

outstd_logic;

secge:

outintegerrange0to9;

secshi:

outintegerrange0to5);

endcomponent;

componentminute

port(rst:

instd_logic;

sectomun:

instd_logic;

muntohour:

outstd_logic;

munge:

outintegerrange0to9;

munshi:

outintegerrange0to5);

endcomponent;

componenthour

port(rst:

instd_logic;

muntohour:

instd_logic;

hourge:

outintegerrange0to9;

hourshi:

outintegerrange0to2);

endcomponent;

componentsettime

port(s1,s0:

instd_logic;

hourge,munge:

bufferintegerrange0to9;

hourshi:

bufferintegerrange0to2;

munshi:

bufferintegerrange0to5);

endcomponent;

componentfenpin

port(rst,clk:

inSTD_LOGIC;

pin:

outSTD_LOGIC);

endcomponent;

componentled_7

port(ain:

inintegerrange0to9;

led7s:

outstd_logic_vector(0to6));

endcomponent;

componentalarm

port(pin,muntohour:

instd_logic;

alarm:

outstd_logic);

endcomponent;

signalSECCO,MINCO:

std_logic;

signalSETKEY:

logic_vector(1downto0);

signalPIN:

std_logic;

begin

U1:

secondportmap(clk=>CLKK,rst=>RET_T,sectomun=>SECCO,

secge=>SEC_1,secshi=>SEC_2);

U2:

minuteportmap(rst=>RET_T,muntohour=>MINCO,sectomun=>SECCO,

munge=>MIN_1,munshi=>MIN_2);

U3:

hourportmap(rst=>RET_T,muntohour=>MINCO,hourge=>HOUR_1,hourshi=>HOUR_2);

U4:

settimeportmap(s1=>S1,s0=>S0,secge=>SEC_1,secshi=>SEC_2,

munge=>MIN_1,munshi=>MIN_2,hourge=>HOUR_1,hourshi=>HOUR_2);

U5:

fenpinportmap(clk=>CLKK,rst=>RET_T,pin=>PIN);

U6:

alarmportmap(pin=>PIN,muntohour=>MINCO,alarm=>ALARM1);

U7:

led_7portmap(ain=>SEC_1,ain=>SEC_2,ain=>MIN_1,ain=>MIN_2,ain=>HOUR_1,ain=>HOUR_2);

ENDone;

libraryieee;----秒计时器

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitysecondis

port(rst,clk:

instd_logic;

sectomun:

outstd_logic;

secge:

outstd_logic_vector(0to3);

secshi:

outstd_logic_vector(0to3));

endsecond;

architectureoneofsecondis

begin

process(rst,clk)

variablesec1:

std_logic_vector(0to3);

variablesec2:

std_logic_vector(0to2);

begin

ifrst='1'thensec1:

="0000";sec2:

="0000";

elsifclk'eventandclk='1'then

sec1:

=sec1+1;

ifsec1="1010"thensec1:

="0000";

sec2:

=sec2+1;

endif;

ifsec2="110"thensec2:

="0000";

endif;

ifsec1="0000"andsec2="1010"then

sectomun<='1';

elsesectomun<='0';

endif;

endif;

secge<=sec1;

secshi<=sec2;

endprocess;

end;

libraryieee;--分计时器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityminuteis

port(rst:

instd_logic;

sectomun:

instd_logic;

muntohour:

outstd_logic;

munge:

outstd_logic_vector(0to3);

munshi:

outstd_logic_vector(0to3);

endentity;

architectureoneofminuteis

begin

process(rst,sectomun)

variablemun1:

std_logic_vector(0to3);

variablemun2:

std_logic_vector(0to3);

begin

ifrst='1'thenmun1:

=0;mun2:

=0;

elsifsectomun'eventandsectomun='1'then

mun1:

=mun1+1;

ifmun1=10thenmun1:

=0;

mun2:

=mun2+1;

endif;

ifmun2=6thenmun2:

=0;

muntohour<='1';

else

muntohour<='0';

endif;

endif;

munge<=mun1;

munshi<=mun2;

endprocess;

end;

libraryieee;---小时计时器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityhouris

port(rst:

instd_logic;

muntohour:

instd_logic;

hourge:

outstd_logic_vector(0to3);

hourshi:

outstd_logic_vector(0to2);

endhour;

architectureoneofhouris

begin

process(rst,muntohour)

variablehour1:

std_logic_vector(0to3);

variablehour2:

std_logic_vector(0to2);

begin

ifrst='1'thenhour1:

=0;hour2:

=0;

elsifmuntohour'eventandmuntohour='1'then

hour1:

=hour1+1;

ifhour1=10thenhour1:

=0;

hour2:

=hour2+1;

endif;

ifhour1=4andhour2=2then

hour1:

=0;hour2:

=0;

endif;

endif;

hourge<=hour1;

hourshi<=hour2;

endprocess;

end;

libraryieee;-----设置时钟

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitysettimeis

port(s1,s0:

instd_logic;

hourge,munge:

bufferstd_logic_vector(0to3);

hourshi:

bufferstd_logic_vector(0to2);

munshi:

bufferstd_logic_vector(0to3));

endentitysettime;

architectureoneofsettimeis

signalsets:

std_logic_vector(1downto0);

begin

sets<=s0&s1;---相并;

process(sets)

variablehn1,min1:

std_logic_vector(0to3);

variablehn2:

std_logic_vector(0to2);

variablemin2:

std_logic_vector(0to2);

begin

casesetsis

when"01"=>hourshi<=hn2;hourge<=hn1;

when"10"=>munshi<=min2;munge<=min1;

when"11"=>hourshi<=hn2;hourge<=hn1;munshi<=min2;munge<=min1;

whenothers=>null;

endcase;

endprocess;

end;

libraryieee;-----7段译码器

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityled_7is

port(ain:

instd_logic_vector(0to3);

led7s:

outstd_logic_vector(0to6));

endentityled_7;

architecturebehavofled_7is

begin

process(ain)

begin

caseainis

when0=>led7s<="1111110";

when1=>led7s<="0110000";

when2=>led7s<="1101101";

when3=>led7s<="1111001";

when4=>led7s<="0110011";

when5=>led7s<="1011011";

when6=>led7s<="1011111";

when7=>led7s<="1110010";

when8=>led7s<="1111111";

when9=>led7s<="1111011";

whenothers=>led7s<="0000000";

endcase;

endprocess;

endbehav;

libraryIEEE;----分频计

use

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- eda 程序

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《公务员财产申报制度》.docx

《公务员财产申报制度》.docx