ed11a14f4a7302768f99392d.docx

ed11a14f4a7302768f99392d.docx

- 文档编号:23258986

- 上传时间:2023-05-15

- 格式:DOCX

- 页数:105

- 大小:9.82MB

ed11a14f4a7302768f99392d.docx

《ed11a14f4a7302768f99392d.docx》由会员分享,可在线阅读,更多相关《ed11a14f4a7302768f99392d.docx(105页珍藏版)》请在冰豆网上搜索。

运放稳定性连载1119

运放稳定性连载11:

电容性负载稳定性:

RISO、高增益及CF、噪声增益

(2)

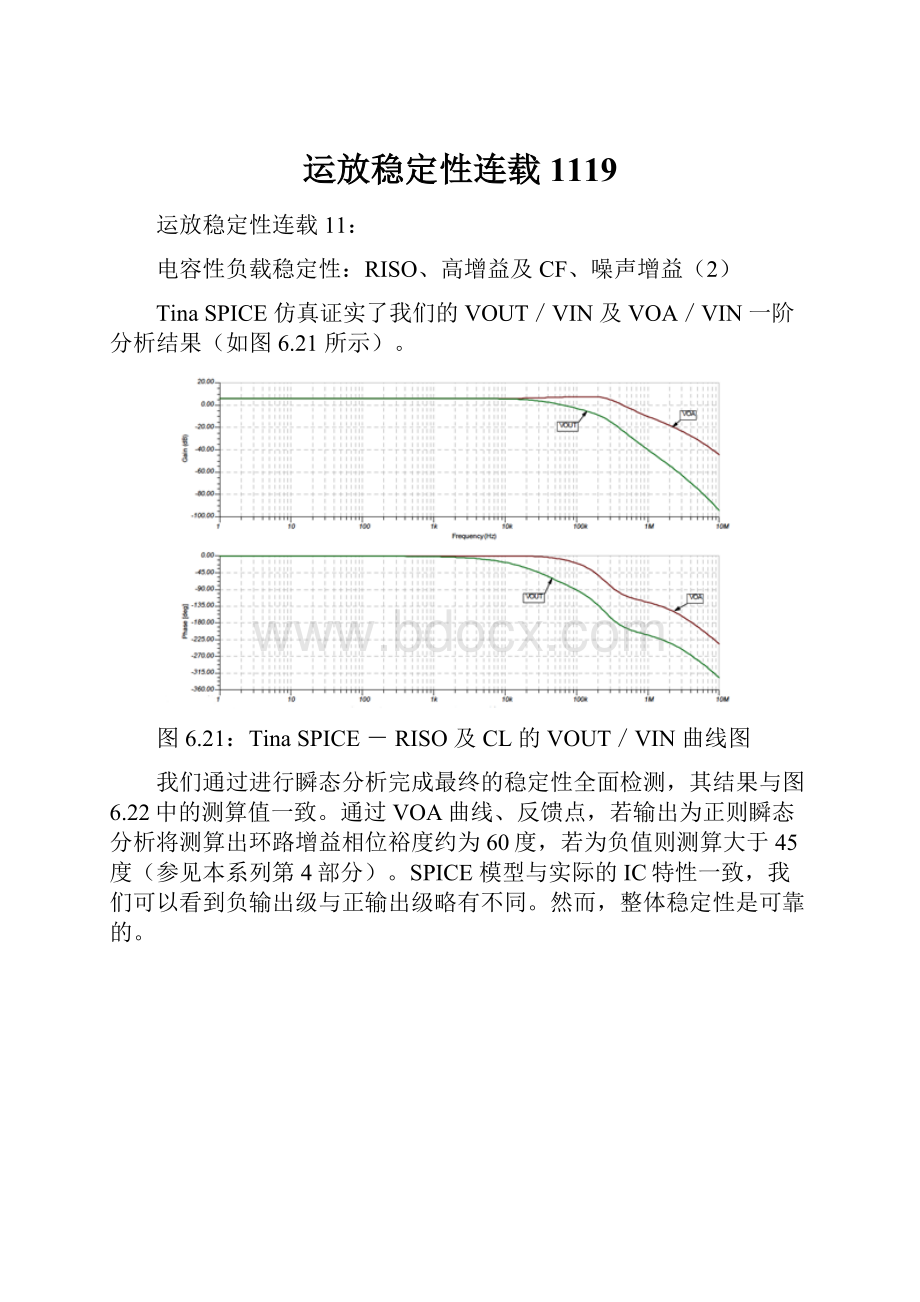

TinaSPICE仿真证实了我们的VOUT/VIN及VOA/VIN一阶分析结果(如图6.21所示)。

图6.21:

TinaSPICE-RISO及CL的VOUT/VIN曲线图

我们通过进行瞬态分析完成最终的稳定性全面检测,其结果与图6.22中的测算值一致。

通过VOA曲线、反馈点,若输出为正则瞬态分析将测算出环路增益相位裕度约为60度,若为负值则测算大于45度(参见本系列第4部分)。

SPICE模型与实际的IC特性一致,我们可以看到负输出级与正输出级略有不同。

然而,整体稳定性是可靠的。

图6.22:

TinaSPICE-RISO及CL的VOUT/VIN瞬态分析

高增益及CF补偿

用于稳定可驱动容性负载的运算放大器的第二种方法是,采用高增益与反馈电容器CF。

该拓扑如图6.23所示。

为了更好地理解该方法的工作原理,我们将绘制带有第二个极点(由RO及CL形成)的“Aol修正”曲线图。

在1/β图中,我们将在相对应的频率位置增加一个极点,该频率位置将导致1/β曲线与闭合速率为20dB/decade的Aol修正曲线相交。

图6.23:

高增益及CF补偿

用一阶分析在Aol修正曲线中绘制第二个极点fp01(如图6.24所示)。

我们通过添加CF在1/β图中增加了一个极点。

请注意如何选择fp1才能确保1/β曲线与Aol修正曲线在闭合速率为20dB/decade时相交。

使用电容器CF作为运算放大器的反馈元件,1/β的最小值经检查为1(0dB),原因是CF对高频短路且VOUT直接反馈到运算放大器的负输入端。

通过一阶分析,我们可以测算出稳定电路,而因为直接反馈至CL故VOUT/VIN传递函数无误差。

因为CF与RF的相互作用,我们测算的VOUT/VINAC传递函数只有一个位于fp1(8.84kHz)处的下降单极点。

该曲线将继续以-20dB/decade的闭合速度下降直至环路增益为零的fcl处,随后VOUT/VIN将随Aol修正曲线继续下降。

图6.24:

一阶分析-高增益及CF

图6.25为用于高增益及CF环路测试的TinaSPICE电路。

同样,断开运算放大器负输入端的环路有助于精确绘制Aol修正曲线。

图6.25:

TinaSPICE-高增益及CF环路

1/β及Aol修正曲线如图6.26所示,两个曲线与一阶测算的第二个Aol极点fp(大致位于5.45kHz)及1/β极点fp1(大致位于8.84kHz)直接相关。

请注意,1/β曲线从8.84kHz继续以-20dB/decade的闭合速度下降直到与0dB点相交,随后从0dB起保持平坦。

图6.26:

TinaSPICE-高增益及CF的Aol修正与1/β曲线图

如图6.27所示,环路增益稳定性及相位裕度良好,从DC至fcl的相位大于45度,这正是我们所需要的。

在fcl点的相位裕度为38.53度。

让我们观察一下闭环AC响应及瞬态分析等情况,以确定该电路是否符合我们的要求。

图6.27:

TinaSPICE-高增益及CF环路增益

我们将采用图6.28中的TinaSPICE电路来进行VOUT/VIN测试。

图6.28:

TinaSPICE-高增益及CF的VOUT/VIN电路

VOUT/VINAC传递函数是我们用一阶分析法测算出来的,如图6.29所示。

下降单极点大致位于10kHz处,VOUT

/VIN以-40dB/decade的闭合速度下降,到100Khz点(此处的环路增益为零)后,VOUT/VIN随Aol修正曲线继续下降。

在100kHz附近有一小段平坦区域,可根据具有过渡区域的Aol修正曲线图上的实际1/Beta曲线测算出本区域的位置。

图6.29:

TinaSPICE-高增益及CF的VOUT/VIN曲线

TinaSPICE瞬态VOUT/VIN分析(如图6.30)显示了无任何过冲或振铃(ringing)的稳定电路。

图6.30:

TinaSPICE-高增益及CF瞬态分析

噪声增益补偿

对于稳定驱动容性负载的运算放大器而言,我们采用的第三种方法是噪声增益。

该拓扑如图6.31所示。

通过绘制由RO及CL形成的第二个极点的“Aol修正”曲线,我们可以了解该方法的工作原理。

我们在1/β曲线上增加一个极点和零点,这样来提高高频段的1/β增益,使其超过Aol修正曲线的第二个极点的位置。

1/β曲线上增加的极点fpn的位置由Rn及Cn设定(如图所示)。

不需要计算零点fzn的位置,因为我们可以通过绘图(从fpn点开始并以20dB/decade的闭合速度下降直至DC1/β值)来确定。

因为该方法的确增加了运算放大器电路的整体噪声增益,故称为噪声增益法。

任何运算放大器的内部噪声(通常指的是输入)会随着1/β曲线频率增益的增加而增加,并反映到输出端。

对于反向噪声增益(InvertingNoiseGain)配置而言,我们可将该拓扑看作加法放大器。

这就很容易看出,VOUT/VIN就是RF/RI。

Cn-Rn网络接地的额外累加对输出电压没有帮助,但却因修正1/β曲线而限制了电路的整体带宽。

这凸显了这样一个事实:

要提高运算放大器电路的稳定性就必须以牺牲其带宽为代价。

对于非反向噪声增益(Non-InvertingNoiseGain)配置而言,必须确保输入信号源阻抗Rs至少比Rn小10倍,才能保证由Rn来决定高频1/β增益的设置。

非反相输入噪声增益拓扑并不一定得出VOUT/VIN=1+RF/RI。

能得到一个推论就很不错了。

图6.31:

噪声增益补偿

从图6.32中,我们推导出非反相输入噪声增益拓扑的VOUT/VINAC传递函数。

为了简化分析,我们为Rn-Cn网络指定一个单变量名Zn。

使用叠加(Superposition)(参见本系列第4部分)及标准运算放大器增益理论,我们将运算放大器视作加法放大器就可以得出VOUT。

结果是:

对任何非反相输入运算放大器配置而言,VOUT/VIN就等于1+RF/RI增益比率。

然而Rn-Cn将影响1/β并降低VOUT/VIN的带宽,还会增加电路的整体噪声增益。

图6.32:

非反相输入噪声增益补偿推论

在图6.33中,我们完成了噪声增益示例的一阶分析。

首先创建Aol修正曲线。

已知DC1/β为10(20dB)。

为了与Aol修正曲线在20dB/decade闭合速度区段相交,我们需要将高频1/Beta设置为100(40dB)。

该值是由RF/Rn设定的。

我们选择将fpn设为比fcl小十倍频程。

在温度、工作环境以及IC工艺发生变化时,这一选择可以确保实现相应的Aol移位。

经验丰富的IC设计师告诉我,在工艺、温度、工作环境等因素变化时,Aol的移位小于½的十倍频程。

而我更倾向于易于记住的、保守的十倍频程经验法则。

如果Aol修正曲线向左偏移一个十倍频程,那么将造成40dB/decade的闭合速度,且出现不稳定现象!

!

通过从fpn点绘制闭合速度为20dB/decade的斜线,直至该斜线与低频1/β相交,我们就可以轻松得到如图所示的fzn。

对于在1/β曲线上配置极点与零点的许多十倍频程经验法则,我们从各方面都觉得非常适合,因为这能实现良好的稳定设计。

VOUT/VIN从DC到环路增益为零的fcl点是平坦的。

从fcl点开始,VOUT/VIN将随着频率的增加相应跟随Aol修正曲线下降。

图6.33:

一阶分析-噪声增益补偿

在图6.34中使用TinaSPICE电路来绘制1/β、Aol修正曲线图及环路增益图以检验一阶分析是否正确。

如以前一样,将环路在运算放大器的负输入端断开,以便绘制Aol修正曲线图。

图6.34:

TinaSPICE-噪声增益环路

TinaSPICE结果再次与我们的一阶测算相符。

图6.35的Aol修正曲线包含第二个极点(大致位于55.45kHz处)。

1/β曲线在低频段为20dB,在高频段为40dB,并包含一个位于1.94kHz左右的极点以及位于194Hz左右的零点。

fcl约为20kHz,其闭合速度为20dB/decade。

图6.35:

TinaSPICE-噪声增益Aol修正及1/β曲线图

图6.36的环路增益曲线证实了在fcl处相位裕度为63.24度的电路是稳定的。

在100Hz与1kHz之间有相位略低于45度的情况,但因数值较小可以不用考虑。

图6.36:

TinaSPICE-噪声增益环路增益

图6.37中的电路用于VOUT/VINAC传递测试及瞬态测试。

图6.37:

TinaSPICE-噪声增益的VOUT/VIN电路

图6.38中的VOUT/VINAC传递函数显示其在响应过程中几乎未出现突峰情况。

正如测算的一样,我们在从~20kHz(在此处环路增益为零)到~50kHz(在此处Aol修正曲线再次以-40dB/decade的闭合速度突变)期间测算出了闭合速度为-20dB/decade的斜率。

图6.38:

TinaSPICE-噪声增益VOUT/VIN

在图6.39中,根据微小的过冲及无下冲情况,瞬态VOUT/VIN测试的相位裕度与约60度的相位裕度相关联(参见本系列第4部分对真实瞬态稳定性测试及二阶瞬态曲线的详细解释)。

图6.39:

TinaSPICE-噪声增益的VOUT/VIN瞬态分析

本部分介绍了“保持容性负载稳定的六种方法”中的三种,即RISO、高增益及CF以及噪声增益。

对于每种方法,我们都能够针对可驱动容性负载的运算放大器进行稳定电路的分析、合成及仿真。

第7部分将介绍噪声增益与CF以及输出引脚补偿方法。

第8部分将介绍第六种方法,即具有双通道反馈的RISO。

运放稳定性连载12:

RO何时转变为ZO?

(1)

作者:

TimGreen,德州仪器Burr-Brown产品线线性应用工程经理

在写“保持容性负载稳定的六种方法”部分时发生了一件有趣的事情。

我们选择了具有“轨至轨”输出的CMOS运算放大器并测量了ROUT,但在高频区域没有环路增益,因而无法确定RO。

根据RO测量结果,我们预测了在1μF容性负载情况下放大器“Aol修正曲线图”中第二个极点的位置。

令我们大吃一惊的是,TinaSPICE仿真在“Aol修正”曲线图进行x5处理时关闭了!

基于先前的第一轮分析结果,这个错误完全超出了可以接受的限度,因而我们对放大器输出阻抗进行了仔细研究。

本系列刊文的第7部分,即本部分将针对两种最常用于小信号放大器的输出拓扑重点讨论放大器的开环输出阻抗ZO。

对于传统的双极性射极跟随器(bipolaremitter-follower)而言,放大器输出级ZO性能良好,并且在整个放大器的单位增益带宽范围内主要呈现为阻性(RO)。

然而,对于许多CMOS轨至轨输出放大器而言,在该放大器的单位增益带宽范围内,ZO同时呈现容性和阻性。

本文并不针对“全NPN输出”的双极性技术(bipolartopology)进行分析,其最常用于功率运算放大器,一种能够提供从50mA至超过10A电流的、在线性区域工作的放大器。

具备丰富的输出阻抗知识非常重要,将有助于正确预测“Aol修正图”,同时也是网络综合技术中用于稳定放大器电路的基本工具。

双极性射极跟随器输出放大器的ZO

图7.1显示了射极跟随器拓扑的典型双极性输出级。

在此类型的输出级中,RO(小信号、开环输出电阻)通常是ZO(小信号、开环输出阻抗)的主要组成部分。

对于既定的DC电流负载,RO一般为常数。

我们先分析一些射极跟随器RO的经验法则,然后借助这些法则来预测不同DC输出电流值对应的RO。

我们最后将用TinaSPICE仿真程序来检验预测值是否正确。

图7.1:

OPA542的关键参数——典型射极跟随器、双极性输出放大器

图7.2显示了典型射极跟随器、双极性输出放大器的参数。

当输入偏置电流为nA级(如10nA)时,采用这种拓扑的器件能够实现极低的噪声与偏移输入参数等优异特性。

某些双极性放大器在输入级中采用JFET使输入偏置电流降低至很低的pA级。

该常用模式的输入级范围一般是两个电源均为2V左右。

输出电压摆幅通常被限制在任一电源轨电压的2V范围内或稍高,采用双电源(如+/-5V~+/-15V)的放大器通常可获得最佳性能。

图7.2:

示例参数:

射极跟随器、双极性输出放大器

高级射极跟随器、双极性放大器的简化模型采用两个GM(电流增益)级,其后跟随了一个晶体管电压输出器输出级,如图7.3所示。

开环输出阻抗ZO主要由RO决定,对于该放大器的单位增益带宽而言是常数。

图7.3:

两级简化模型:

射极跟随器、双极性输出放大器

对于大多数放大器而言,放大器输出端空载时,输出级的AB类偏置电流约为整个放大器静态电流的½。

双极晶体管的RO与1/gm成正比,其中gm为晶体管的电流传输比(currenttransferratio)或电流增益。

由于gm与集电极电流IC成正比,因而RO与IC成反比。

当IC从空载输出电流向满负载输出电流增加时,RO将会降低。

这可能会使人有这样的推测,即当输入电流高到一定极限时RO将为零。

然而,由于晶体管的物理特性、内部驱动以及偏置排列(biasarrangement)等原因,上述推测不成立。

我们将测量最高可用负载电流下的RO值,并把它定义为RX。

然后测量空载电流下的RO值,并得出给定放大器电路的常数KZ,该常数可用于预测任何负载电流下的RO变化情况。

从图7.4中,我们可清楚了解,如何用射极跟随器的输出项描述从前端gm级到放大器输出引脚之间的路径。

图7.4:

ZO定义:

射极跟随器、双极性输出放大器

图7.5详细描述了常数为RX的射极跟随器ZO模型,测量环境为:

满负载电流、传输函数为KZ/IC的串联式电流控制电阻器。

由于器件具有推(PNP晶体管)和拉(NPN晶体管)输出级,所以ZO模型包括每个输出级的等价RO模型。

回馈至输出引脚的有效小信号AC输出阻抗等于推输出级与拉输出级阻抗的并联组合。

对于ZO小信号AC模型而言,VCC及VEE两个电源均对AC短路。

图7.5:

ZO模型:

射极跟随器、双极性输出放大器

并不是放大器的所有SPICE宏模型都相同。

要研究输出阻抗ZO的所有仿真,必须在使用真实器件正确建立输出模型的宏模型上完成,以及需要相匹配的A-B类偏置电路对真实器件进行精确建模。

我们通常无法判断制造商提供的模型是否完备。

在过去4年中,Analog&RFModels()公司的W.K.Sands为德州仪器(TI)Burr-Brown产品部开发的高精度放大器创建了大部分SPICE模型。

如上所示,这些放大器SPICE模型极致诠释了真实的硅芯片放大器,其中包含了详细的功能列表,如输出级的正确建模以及AB类偏置电路等。

参见图7.6。

图7.6:

并非所有的SPICE放大器模型都相等!

由于我们无法找到具有精确A-B类偏置及真实晶体管输出的双极性射极跟随器放大器宏模型,来进行真实环境下的准确性能分析,所以我们自建了测评模型。

在这里,我们可以看到一个由开环增益为160dB(x100E6)的压控电压源实施的理想前端。

输出晶体管QP及QM位于简化的A-B类偏置电路中。

我们将放大器的最大输出电流设为27mA。

因此,若需找出RO参数RX,我们就要采用+27mA的负载电流进行测试。

通过使用“输入电阻”RL及“反馈”电感LF,可以在TinaSPICE中轻松建立简单的ZO测试电路。

如图7.7所示。

我们可以将DC环境下的电感器视为短路,而RL上施加了电压VDC,形成了如下所示的DC负载电流。

凭借理想的1T-Henry(1E12Henry)电感器,我们可以实现DC闭环路径,以使SPICE能够找到工作点(operatingpoint),但对于任何目标AC频率则为开路。

现在,如果我们用1A的AC电流源Itest来激励电路,则经过dB数学转换后VOUT成为ZO。

请注意,在这种重负载情况下,IOUT=+27mA,即QM(实际处于“关闭”状态)和QP(处于“开启”状态)决定了输出阻抗。

图7.7:

ZO、重负载IOUT=+27mA

图7.7显示了双极性射极跟随器输出放大器在当IOUT=+27mA时ZO的测量结果。

SPICE的初始结果将绘制在“线性dB”区域。

如果我们对y坐标轴取“对数”,则会直接产生ZO的欧姆值。

y坐标轴上的对数标尺对我们查看其他频率带宽不为常数(如CMOSRRO)的ZO图很有帮助。

图7.8:

ZOAC图、重负载IOUT=+27Ma

图7.9显示了IOUT=+27mA时的大等效负载ZO模型。

RX的测量值为6.39Ω。

我们假定,使用的QP及QM输出晶体管性能接近,并因此赋予这两个输出晶体管相同的RX值。

如有需要,我们可以重新进行分析并测量IOUT=-27mA时的RX值。

结果将会非常接近,以致可以忽略其中的差别。

根据此模型,我们可以假定RMim为高阻抗,不会干扰RO的测量。

此外,我们假定RPip比RX小得多。

图7.9:

重负载ZO模型

图7.10详细描述了A-B类偏置射极跟随器的无输出负载环境。

我们将A-B类偏置电流IAB设为1.08mA。

对于无输出负载的情况,两个输出晶体管QP及QM均处于开启状态且对ZO产生的影响相同。

图7.10:

ZO、空载IOUT=0mA

如图7.11所示,空载ZO的测量值为14.8Ω。

凭借这些信息以及ZO的重负载值(由RX推算),我们通过计算常数KZ可以完成对小信号ZO的建模。

图7.11:

ZOAC图、空载IOUT=0mA

在图7.12中,我们使用空载条件下的射极跟随器ZO模型。

我们使用重负载条件下得到的结果并为RX填入相应值。

现在,我们需要求出空载条件ZO的KZ值,并假定两个输出晶体管QP及QM的参数相近。

详细的推导过程如上图所示,我们发现KZ值为0.0250668。

图7.12:

空载ZO模型

现在,让我们测试射极跟随器ZO模型。

我们将使用QP提供的约为2倍IAB大小的DC电流,即A-B类偏置电流的两倍。

这样就得关闭QM,并迫使QP的RO成为ZO的主要部分。

从图7.13可以看出这基本是正确的。

这也恰当地解释了A-B类偏置方案在真实环境中是如何发挥作用的。

我们了解到,当负载电流呈正增长时,所有A-B类偏置电流开始向正输出晶体管QP偏移。

当负载电流变为负值时,全部A-B类偏置电流开始向QM偏移,直至QP在负的重负载电流作用下完全关闭。

图7.13:

ZO、轻负载IOUT=+2xIAB(2.16mA)

图7.14显示了射极跟随器轻负载ZO模型。

使用已知的RX及KZ值,我们可以计算出需要的等价ZO值,然后采用下图结果运行TinaSPICE仿真。

我们计算得出轻负载下ZO值为13.2326Ω,而SPICE的测量结果为12.85Ω。

两个结果非常相近,适用于各种相关分析。

如果投入时间研究,我们会发现QP及QM的参数不完全一样。

图7.14:

轻负载ZO模型

图7.15中显示了轻负载时ZO的TinaSPICE仿真结果。

图7.15:

ZOAC图、轻负载IOUT=+2.16mA

运放稳定性连载13:

RO何时转变为ZO?

(2)

现在我们可以建立如图7.16所示的、完整的射极跟随器ZO曲线图集。

从图7.16中我们可以看出,ZO由RO决定,RO对于放大器的单位增益带宽而言是常数,其会随着负载电流的上升而下降。

请注意,ZO是根据源极和漏极电流在轻负载条件下以及重负载条件下源极或漏极ZO无显著差别的情况下得出的。

在双极性射极跟随器放大器产品说明书中应包含了这些重要的ZO曲线。

图7.16:

完整的ZO曲线:

双极性射极跟随器

双极性射极跟随器输出放大器的ZO及容性负载

对于射极跟随器输出级的容性负载,我们将采用图7.17中的模型。

我们可以从产品说明书中查询参数,也可以通过测量放大器无容性负载下的Aol曲线获得参数。

在放大器的空载Aol曲线上,RO与CL相互作用形成第二个极点fp2。

图7.17:

双极性射极跟随器ZO及容性负载

我们将在射极跟随器双极性放大器上施加许多不同的容性负载,并测出RO及CL相互作用形成的极点fp2。

图7.18中的电路使用LT作为DC短路器来建立DC工作点。

LT对于任选的AC频率实现开路,因而我们可以观察到已修正的Aol曲线。

CT对DC开路但对任何频率的目标AC短路,并且CT还起到将AC测试源VG与电路连接的作用。

通过检验我们发现Aol=VOA/VM。

图7.18:

用于测量修正Aol曲线的TinaSPICE电路

图7.19显示了多种不同容性负载情况下的最终修正Aol曲线。

图7.19:

不同CL值的修正Aol曲线

图7.20详细描述了RO及CL引起的fp2极点在修正Aol曲线中的预测位置。

图中还显示了对应于每个fp2的实际的TinaSPICE测量位置。

由于采用了稳定的综合技术,TinaSPICE测量的fp2实际值与我们的预测值并无显著差异。

图7.20:

不同CL的fp2位置:

预测值及实际值

双极性射极跟随器输出放大器ZO的总结

图7.21汇总了双极性射极跟随器放大器ZO的关键参数。

在放大器的单位增益带宽范围内,ZO由RO决定,且相对频率而言为常数。

当DC输出负载电流增加时,RO降低并与IOUT成反比。

容性负载、CL与RO相互作用以在原先的放大器Aol曲线上形成第二个极点fp2。

我们可以使用修正Aol曲线,来综合考虑适当的闭环补偿值以获得更好的稳定性。

RO会随过程与温度的变化而相应发生变化。

对应于过程及温度变化的经验法则是0.65*ROtyp(-55C)~1.5*ROtyp(125C),其中ROtyp为25C时的RO典型值。

我们业已开发的经验法则不总是适用于双极性射极跟随器放大器的开环输出阻抗。

可从放大器制造商处获得最完整和最精确的ZO数据,经测量也能获得。

图7.21:

双极性射极跟随器ZO的总结

CMOSRRO(轨至轨输出)放大器的ZO

图7.22显示了典型的CMOSRRO放大器拓扑。

此类输出级中,RO(小信号、开环输出电阻)通常是ZO(小信号、开环输出阻抗)的主要组成部分。

RO与大多数DC负载电流成反比。

然而在轻负载电流情况下,RO与DC负载电流成正比。

在中低频区域,ZO通常呈现为容性。

由于RL(输出端的阻性负载)与ZO容性部分相互作用,因而放大器Aol曲线在低频区域将受到影响。

图7.22:

典型的CMOSRRO放大器

图7.23以CMOSRRO放大器为例列出了相关参数。

OPA348也是一种RRI(轨至轨输入)放大器。

CMOSRRIO(轨至轨输入/输出)拓扑理想适用于具有以下特性的单电源应用:

输入和输出轨上的摆幅很小、极低的静态电流以及极低的输入偏置电流。

其噪声通常比双极性射极跟随器放大器要高得多。

图7.23:

示例参数:

CMOSRRIO放大器

图7.24是我们针对典型CMOSRRO放大器绘制的简化模型,该放大器使用可控制电流源GM2的电压输出差分前端GM2驱动RO,从而产生可控制输出电流源GMO的电压。

电容CO反馈至RO、GM2结点。

从这个简化模型可以看出,在高频段ZO=RO。

当频率从高频向中、低频变化时,我们将看到CO产生的作用,ZO也因此呈现容性。

图7.24:

简化模型:

CMOSRRO放大器

如图7.25所示,

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ed11a14f4a7302768f99392d

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#全自动电容电感测试仪.docx

#全自动电容电感测试仪.docx