数码管显示实验说明.docx

数码管显示实验说明.docx

- 文档编号:23017265

- 上传时间:2023-04-30

- 格式:DOCX

- 页数:21

- 大小:1.89MB

数码管显示实验说明.docx

《数码管显示实验说明.docx》由会员分享,可在线阅读,更多相关《数码管显示实验说明.docx(21页珍藏版)》请在冰豆网上搜索。

数码管显示实验说明

“单数码管显示实验”的实验步骤

1.利用新建工程向导创建一个新工程。

打开建立新工程管理窗口。

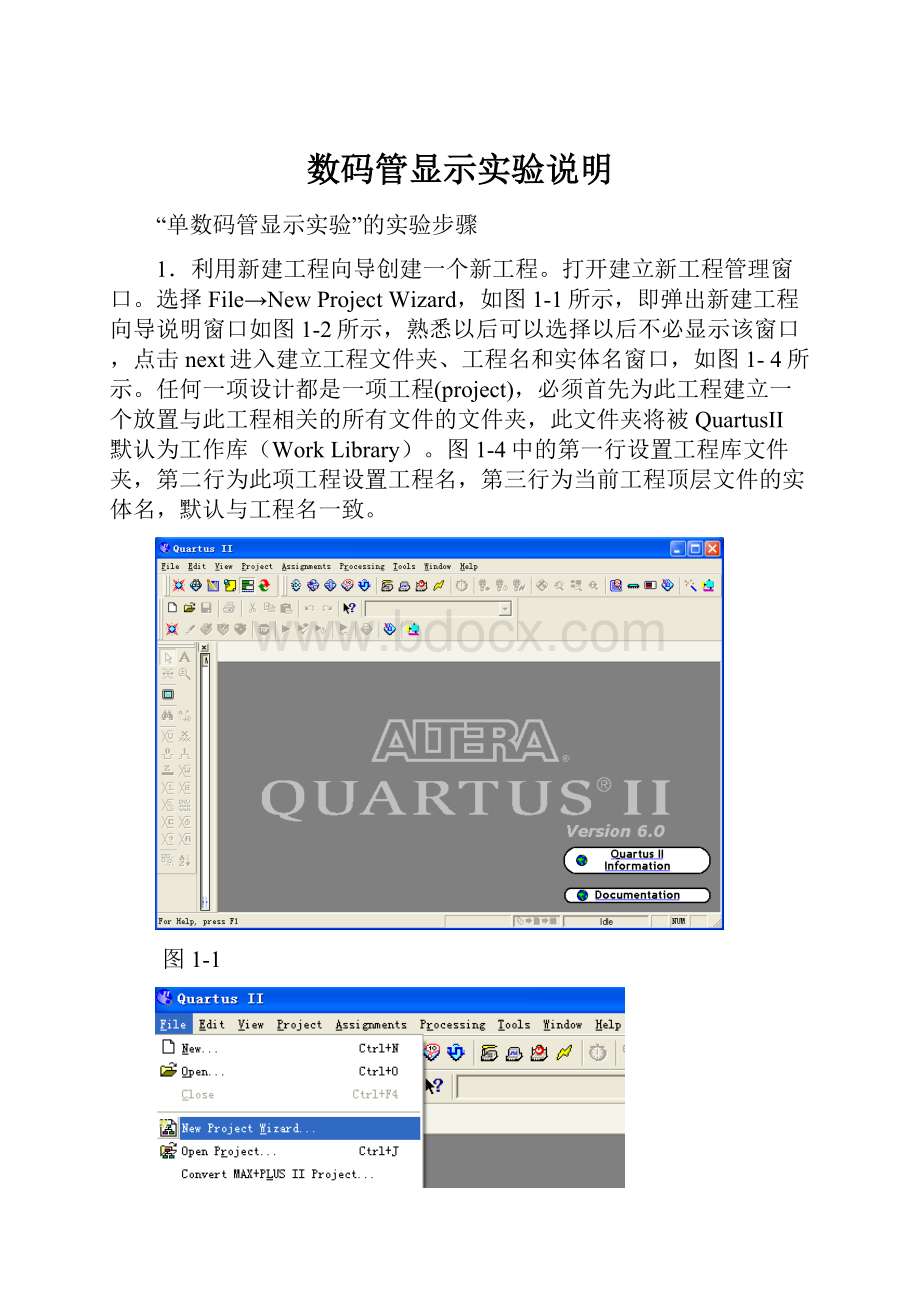

选择File→NewProjectWizard,如图1-1所示,即弹出新建工程向导说明窗口如图1-2所示,熟悉以后可以选择以后不必显示该窗口,点击next进入建立工程文件夹、工程名和实体名窗口,如图1-4所示。

任何一项设计都是一项工程(project),必须首先为此工程建立一个放置与此工程相关的所有文件的文件夹,此文件夹将被QuartusII默认为工作库(WorkLibrary)。

图1-4中的第一行设置工程库文件夹,第二行为此项工程设置工程名,第三行为当前工程顶层文件的实体名,默认与工程名一致。

图1-1

图1-2

图1-3

图1-4

2.将设计文件加入工程。

如果此前已经设计了一些此工程的设计文件,则可点击图1-5File栏右边的按钮,查找与工程相关的所有设计文件加入到工程中。

如果没有,则直接点击Next进入下一步。

图1-5

3.选择目标器件。

在如图1-6所示窗口中,首先在Family下拉列表框中选择芯片系列。

在右侧的Package栏选择芯片的封装方式,在Pincount栏选择芯片的管脚数,在Speedgrade栏选择芯片速度级别。

在Availabledevices框中将显示符合以上条件的一些芯片,从中选择与EDA实验开发箱上一致的FPGA芯片,然后点击Next进入下一步。

图1-6

4.设置其它EDA工具。

在如图1-7所示的窗口中,有3项选择:

DesignEntry/Synthesis用于选择输入的HDL类型和综合工具;Simulation用于选择仿真工具;TimingAnalysis用于选择时序分析工具。

这是除QuartusII自含的所有设计工具以外,还可以外加的工具。

如果都不选择,就表示仅使用QuartusII自含的所有设计工具,点击Next进入下一步。

图1-7

5.结束设置。

在如图1-8所示的窗口中,列出了此项工程相关的设置情况。

最后单击Finish按钮,就设定好了此工程,并出现seg7_4的工程管理窗口(图1-9)Projectnavigator。

可以选择View→UtilityWindow→Projectnavigator开/关此管理窗口。

在工程管理窗口的Hierarchy页,主要显示芯片资源占用情况;在Files页,显示工程中设计文件和仿真文件等;在DesignUnites页,主要显示本工程项目的层次结构和各层次的实体名;

图1-8

图1-9

6.新建VHDL设计文件并保存。

选择File→New得到如图1-10的文件选择窗口,在DesignFiles中选择VHDL,点击OK进入VHDL文本编辑窗口如图1-11所示。

在VHDL文本编辑窗口中键入设计文件,保存时注意文件名与实体名必须一致。

如图1-12所示。

图1-10

图1-11

图1-12

VHDL源文件如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

Entityseg7_4is

PORT(BCD_in:

INSTD_LOGIC_VECTOR(3DOWNTO0);--输入四位BCD码

SG_out:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));--输出七位字形码

END;

ARCHITECTUREoneOFseg7_4IS

BEGIN

PROCESS(BCD_in)

BEGIN

CASEBCD_inIS

WHEN"0000"=>SG_out<="0111111";

WHEN"0001"=>SG_out<="0000110";

WHEN"0010"=>SG_out<="1011011";

WHEN"0011"=>SG_out<="1001111";

WHEN"0100"=>SG_out<="1100110";

WHEN"0101"=>SG_out<="1101101";

WHEN"0110"=>SG_out<="1111101";

WHEN"0111"=>SG_out<="0000111";

WHEN"1000"=>SG_out<="1111111";

WHEN"1001"=>SG_out<="1101111";

WHEN"1010"=>SG_out<="1110111";

WHEN"1011"=>SG_out<="1111100";

WHEN"1100"=>SG_out<="0111001";

WHEN"1101"=>SG_out<="1011110";

WHEN"1110"=>SG_out<="1111001";

WHEN"1111"=>SG_out<="1110001";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

END;

7.启动全程编译。

设置编译焦点如图1-13所示。

QuartusII编译器是由一系列处理模块构成,包括:

对设计项目检错、逻辑综合、结构综合、输出结果的编辑配置,以及时序分析。

在这一过程中,将设计项目适配到FPGA/CPLD目标器件中,同时产生多种用途的输出文件,如功能和时序信息文件、器件编程目标文件等。

选择Processing→StartCompilation启动全程编译,如图1-14所示。

QuartusII将对设计项目进行多项处理,其中包括:

排错,数据网表文件提取、逻辑综合、适配、装配文件(仿真文件与编程配置文件)生成,以及基于目标器件的工程时序分析等。

图1-13

图1-14

编译过程中,要注意工程管理窗口下方的Processing栏中的编译信息,如果设计文件有错误,将会在其中用红色字显示出来。

对于Processing栏显示的语句格式错误,可以双击此条信息,即弹出对应的VHDL文件,在深色标记处即为文件中的错误所在,改正后再次启动编译,直至排除所有错误,显示编译成功如图1-15。

图1-15

8.逻辑功能仿真。

首先建立仿真波形文件,选择File→New,在New窗口的Verification/DebuggingFiles项目中选择VectorWaveformFile,可以打开如图1-16所示的波形文件编辑器。

添加需要观察的输入、输出节点或总线。

在波形文件编辑窗口的左区NAME下方点击鼠标右键,在弹出的菜单中选择Insert→InsertNodeorBus,弹出添加节点或总线窗口如图1-17所示,在其中点击NodeFinder后弹出图1-18所示窗口,在Filter栏选择Pins:

all,点击List后将在NodesFound栏列出所有的输入输出引脚信号,可以选择全部或一部分进行观察。

点击OK后进入下一步添加多个项目如图1-19,点击OK完成添加。

图1-16

图1-18

图1-19

设置仿真时间区域,通常设置在数十微秒间。

选择Edit→EndTime弹出图1-20所示窗口,本次设计输入信号只有八种组合,所以可将时间区域设置为1微秒。

编辑输入波形(即输入激励信号)。

选择View→FitinWindow即可在波形编辑窗口内看见整个时间区域(先前已经设置为1微秒)。

在输入信号a的幅度设定区,按下鼠标左键向右拖,被选定范围颜色变深,再用左键点击窗口左侧画图工具栏中的高电平或低电平,设置好的输入波形如图1-21所示。

图1-20

图1-21

仿真器参数设置。

选择Assignment→Setting命令,在Setting窗口的Category→SimulationSetting下选择Timing(即时序仿真),并选择仿真激励文件seg7_4.vwf。

选择SimulationOptions栏,确认选定Simulationcoveragereporting复选框:

毛刺检测为1ns宽度;选中RunSimulationunitallvectorstimuliareused复选框等。

启动仿真器。

选择Processing→StartSimulation命令,直到出现Simulationwassuccessful,仿真结束,得到图1-22所示的仿真结果。

图1-22

9.引脚锁定。

为了对所设计的七段显示译码器进行硬件测试,应将其输入输出信号锁定在芯片确定的引脚上,编译后下载。

选择Assignment→Pins进入图1-23所示管脚编辑窗口PinPlanner。

在Location栏的下拉框中选择相应的引脚号。

图1-23

图1-24

10.编程下载。

打开编程窗口,选择Tool→Programmer命令,弹出图1-25所示窗口。

在Mode下拉列表框中选择JTAG模式(默认)。

设置编程器。

若是初次安装QuartusⅡ,必须进行编程器选择操作。

单击HardwareSetup按钮可设置下载接口方式,在图1-26所示的HardwareSetup对话框中,设置USB-Blaster方式,利用计算机的USB口直接对FPGA进行配置。

选择需要下载的文件,点选Program/Configure下的方框,如图1-27所示。

单击Start按钮,即开始下载,下载完成后如图1-31所示。

图1-25

图1-26

图1-27

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数码管 显示 实验 说明

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《地质测量图绘制细则》.docx

《地质测量图绘制细则》.docx