太原理工大学EDAFPGA八路抢答器应用设计课程设计.docx

太原理工大学EDAFPGA八路抢答器应用设计课程设计.docx

- 文档编号:22995623

- 上传时间:2023-04-29

- 格式:DOCX

- 页数:14

- 大小:377.11KB

太原理工大学EDAFPGA八路抢答器应用设计课程设计.docx

《太原理工大学EDAFPGA八路抢答器应用设计课程设计.docx》由会员分享,可在线阅读,更多相关《太原理工大学EDAFPGA八路抢答器应用设计课程设计.docx(14页珍藏版)》请在冰豆网上搜索。

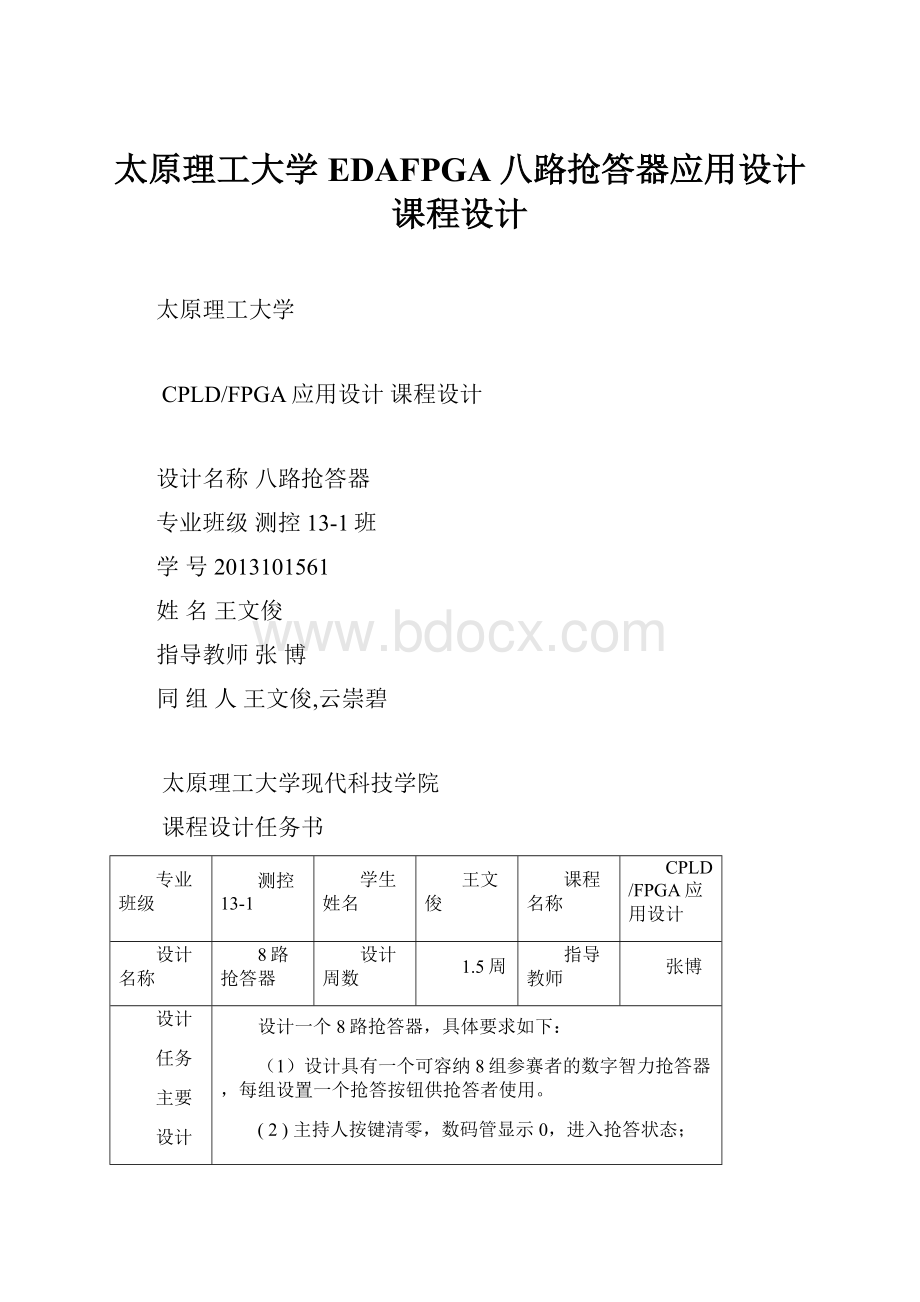

太原理工大学EDAFPGA八路抢答器应用设计课程设计

太原理工大学

CPLD/FPGA应用设计课程设计

设计名称八路抢答器

专业班级测控13-1班

学号2013101561

姓名王文俊

指导教师张博

同组人王文俊,云崇碧

太原理工大学现代科技学院

课程设计任务书

专业班级

测控13-1

学生姓名

王文俊

课程名称

CPLD/FPGA应用设计

设计名称

8路抢答器

设计周数

1.5周

指导教师

张博

设计

任务

主要

设计

参数

设计一个8路抢答器,具体要求如下:

(1)设计具有一个可容纳8组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(2)主持人按键清零,数码管显示0,进入抢答状态;

(3)主持人发出开始命令,8人开始抢答,若有人先按下抢答按钮,数码管显示该组号码,其他人再按抢答按钮,系统不再响应;

(4)设置记分电路,可显示每组选手的分数;

(5)设置计时显示。

设计内容

设计要求

(1)根据选题要求,进行方案比较,画出系统框图;

(2)使用VHDL语言描述各单元电路;

(3)利用QuartusII10.0软件对单元电路进行编译,仿真,引脚锁定,下载调试;

(4)撰写课程设计任务书。

主要参考

资料

1张文爱.EDA技术与FPGA应用设计.电子工业出版社,2013

2贾秀美.数字电路硬件设计实践.高等教育出版社,2008

学生提交

归档文件

课程设计说明书,主要包括以下内容:

(1)设计方案,系统框图,原理分析;

(2)系统各模块的VHDL源程序;

(3)综合编程部分,包括各模块的综合结果,仿真分析,系统管脚定义,下载验证结果;

(4)设计总结部分,指出设计系统的特点及选用方案优缺点,提出改进意见及展望,总结设计收获,体会;

(5)参考文献。

指导教师签名:

日期:

一、设计目的

1、加深对VHDL语言设计的理解;

2、通过对抢答器的设计加深对CPLD/FPG课程理解

3、通过对抢答器的设计了解简易集成电路的设计思路。

二、设计要求

1.设计具有一个可容纳8组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

2.主持人按键清零,数码管显示0,进入抢答状态;

3.主持人发出开始命令,8人开始抢答,若有人先按下抢答按钮,数码管显示该组号码,其他人再按抢答按钮,系统不再响应;

4.设置记分电路,可显示每组选手的分数;

5.设置计时显示。

三、设计方案

根据系统设计要求可知,系统的输入信号有:

各组的抢答按钮A、B、C、D、E、F、G、H,系统清零信号CLR,系统时钟信号CLK,计分复位信号RET,加分按钮信号ADD,计时预置控制信号LDN,计时使能信号EN,计时预置调整信号按钮AN、BN,系统的输出信号有:

4个组抢答成功与否的指示灯控制信号输出口LEDA、LEDB、LEDC、LEDD、LEDE、LEDF、LEDG、LEDH,4个组抢答时的计时数码管显示控制信号若干,抢答成功组别显示的控制信号若干,各组计分动态显示的控制信号若干。

本次课程设计的主要目的旨在通过独立完成一个“抢答器”的设计,达到对EDA技术的熟练掌握,提升对《CPLD/FPGA技术及应用》课程所学内容的掌握和应用。

以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

基于VHDL程序设计中拥有输入设计流程,其包括设计输入,综合,适配,仿真测试和编程下载等方法。

与其他应用软件相比,他提供了更强大、更直观便捷和操作灵活的原理图输入设计功能,同时还配备了更丰富的适用于各种需要的元件库,其中包括基本的逻辑元件,宏功能元件,以及类似于IP核的参数可设置的宏功能块LPM库。

设计者不必具备许多诸如编程技术,硬件描述语言等知识就能迅速入门,完成较大规模的电路设计系统。

能进行任意层次的数字系统设计,传统的数字电路实验只能完成单一层次的设计。

能对系统中的任意层次,或任一元件的功能进行精确的时序仿真。

通过时序仿真能迅速定位电路系统中的错误所在,并及时纠正。

四:

设计模块方框图

根据抢答器的功能要求,可以得出如下模块系统结构图:

五模块功能分析

1抢答输入开关电路该电路由8个开关按键组成,每一个选手与一个开关对应。

开关为常开型,即当按下开关时,开关自动的弹开断开,此时输入抢答信号自动变为高电平;当按下抢答开关时,开关闭合,输入抢答信号为低电平。

2锁存器当只要有一个且为任意一个抢答输入信号产生时,触发器电路被触发,在输出端产生相应的开关电平信息,同时为避免之后的抢答开关按钮也按下产生错乱,最先产生的输出电平变化又反馈回来将触发器锁定住,并保持输出的电平信息。

这样就避免了抢答先后发生紊乱不清楚的现象发生。

3编码器编码器的作用是将开关信息转化为8421BCD码,以提供数字显示电路所需要的编码输入。

4译码器译码器的作用是将编码器输出的8421BCD码转化为数码管需要的逻辑状态,译码器由七段共阴二极管组成,高位在左,低位在右,如当输入译码器的信号为“”时,数码管的七个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1,接有高电平的段亮,于是数码管显示为“5”。

5解锁器

当触发锁存电路被锁存后,若要进行下一轮的重新抢答,则需要将锁存器解锁,可通过强迫是复位控制置为1,使锁存处于等待锁存状态,以准备进行下一轮的抢答。

8路抢答器源VHDL程序,(包含倒计时dqs,数码shuma,计分器jfq程序)

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityqiangdaqiis

port(rst:

instd_logic;

clk:

instd_logic;

key:

instd_logic;

en:

instd_logic;

q1,q2,q3,q4,q5,q6,q7,q8:

instd_logic;

shuma:

outstd_logic_vector(6downto0);

led:

outstd_logic_vector(7downto0);

jfq:

outstd_logic_vector(6downto0);

djs:

outstd_logic_vector(6downto0)

);

endqiangdaqi;

architectureBehavioralofqiangdaqiis

signals:

std_logic_vector(3downto0);

signalq:

std_logic_vector(7downto0);

signalmax:

std_logic;

signalb:

std_logic_vector(3downto0):

="0000";

signalA:

std_logic_vector(3downto0):

="0011";

signalcnt:

std_logic_vector(25downto0);

signalclks:

std_logic;

begin

process(rst,clk,clks)

begin

ifrst='0'then

cnt<=(others=>'0');

elsifclk'eventandclk='1'then

cnt<=cnt+1;

endif;

clks<=cnt(24);

endprocess;

process(en,A,clks)

begin

ifclks'eventandclks='1'anden='1'then

caseAis

when"0000"=>djs<="1000000";

when"0001"=>djs<="1111001";

when"0010"=>djs<="0100100";

when"0011"=>djs<="0110000";

whenothers=>null;

endcase;

ifa/="0000"then

a<=a-"0001";

endif;

endif;

endprocess;

process(rst,clk)

begin

q<=q8&q7&q6&q5&q4&q3&q2&q1;

ifrst='0'then

s<="0000";

elsifclk'eventandclk='1'andA="0000"then

caseqis

when"10000000"=>s<="0001";

when"01000000"=>s<="0010";

when"00100000"=>s<="0011";

when"00010000"=>s<="0100";

when"00001000"=>s<="0101";

when"00000100"=>s<="0110";

when"00000010"=>s<="0111";

when"00000001"=>s<="1000";

whenothers=>null;

endcase;

endif;

endprocess;

process(rst,clk,s,A)

begin

ifrst='0'then

max<='0';

elsifclk'eventandclk='1'andA="0000"then

ifs>0then

max<='1';

endif;

endif;

endprocess;

process(rst,max,s,A)

begin

ifrst='0'then

shuma<=(others=>'1');

elsifmax'eventandmax='1'andA="0000"then

ifs(3)='0'ands

(2)='0'ands

(1)='0'ands(0)='0'then

shuma<="1111111";

elsifs(3)='0'ands

(2)='0'ands

(1)='0'ands(0)='1'then

shuma<="1111001";

elsifs(3)='0'ands

(2)='0'ands

(1)='1'ands(0)='0'then

shuma<="0100100";

elsifs(3)='0'ands

(2)='0'ands

(1)='1'ands(0)='1'then

shuma<="0110000";

elsifs(3)='0'ands

(2)='1'ands

(1)='0'ands(0)='0'then

shuma<="0011001";

elsifs(3)='0'ands

(2)='1'ands

(1)='0'ands(0)='1'then

shuma<="0010010";

elsifs(3)='0'ands

(2)='1'ands

(1)='1'ands(0)='0'then

shuma<="0000010";

elsifs(3)='0'ands

(2)='1'ands

(1)='1'ands(0)='1'then

shuma<="1111000";

elsifs(3)='1'ands

(2)='0'ands

(1)='0'ands(0)='0'then

shuma<="0000000";

endif;

endif;

endprocess;

process(rst,max,s,A)

begin

ifrst='0'then

led<=(others=>'0');

elsifmax'eventandmax='1'andA="0000"then

ifs(3)='0'ands

(2)='0'ands

(1)='0'ands(0)='0'then

led<="00000000";

elsifs(3)='0'ands

(2)='0'ands

(1)='0'ands(0)='1'then

led<="00000001";

elsifs(3)='0'ands

(2)='0'ands

(1)='1'ands(0)='0'then

led<="00000010";

elsifs(3)='0'ands

(2)='0'ands

(1)='1'ands(0)='1'then

led<="00000100";

elsifs(3)='0'ands

(2)='1'ands

(1)='0'ands(0)='0'then

led<="00001000";

elsifs(3)='0'ands

(2)='1'ands

(1)='0'ands(0)='1'then

led<="00010000";

elsifs(3)='0'ands

(2)='1'ands

(1)='1'ands(0)='0'then

led<="00100000";

elsifs(3)='0'ands

(2)='1'ands

(1)='1'ands(0)='1'then

led<="01000000";

elsifs(3)='1'ands

(2)='0'ands

(1)='0'ands(0)='0'then

led<="10000000";

endif;

endif;

endprocess;

process(key,b)

begin

ifkey'eventandkey='1'then

b<=b+"0001";

endif;

ifb="1010"then

b<="0000";

endif;

casebis

when"0000"=>jfq<="1000000";

when"0001"=>jfq<="1111001";

when"0010"=>jfq<="0100100";

when"0011"=>jfq<="0110000";

when"0100"=>jfq<="0011001";

when"0101"=>jfq<="0010010";

when"0110"=>jfq<="0000010";

when"0111"=>jfq<="1111000";

when"1000"=>jfq<="0000000";

when"1001"=>jfq<="0010000";

whenothers=>null;

endcase;

endprocess;

endBehavioral;

实验结果图:

实物图显示

六:

调试

引脚锁定完成,便进行硬件下载命令。

试验箱接通电源后,便进行实验验证,按下清零键res,然后按下抢答的开关按钮,当下按的是第几个编号,数码管显示的就是该编号,再按其他的抢答按钮已无反应,表示抢答成功,该锁存模块电路时正确的。

然后再按下清零键rest,再逐一尝试其他的抢答开关按钮,观察是否都能正常工作,如果都正常工作,则表示该8路智能抢答器设计正确。

打开实验箱,讲导线连接到对应的引脚上,按下复位键,此时只有发光二级管是亮的,然后按下一号组,同时显示器上显示1,这时再按下2,显示器仍然显示1.按下复位键,先按2,再按3,显示器显示2。

这个时候实验成功

七、实验心得

通过这次的EDA课程设计,让我熟练地掌握了EDA设计QuartusII10.0软件的操作,使用VHDL语言,对应填写管教,安装硬件驱动,连接EDA实验箱出来结果,之前学会了基本的课程设计以及编译仿真的操作,这次的智能抢答器又让我学到很多,但是其中也遇到了很多困难。

我们小组三个人,由我们共同来完成这个设计实验。

在设计的过程中我进一步了解了设计的步骤和原理,进一步加深了对《CPLD/FPGA应用设计》这门课的理解,增强了以后学习的兴趣,为以后的工作积累了一定的经验。

这让我们知道了以前并不了解的知识。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 太原 理工大学 EDAFPGA 八路 抢答 应用 设计 课程设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《地质测量图绘制细则》.docx

《地质测量图绘制细则》.docx