译码器和数据选择器实验报告Word下载.docx

译码器和数据选择器实验报告Word下载.docx

- 文档编号:22975765

- 上传时间:2023-02-06

- 格式:DOCX

- 页数:10

- 大小:170.70KB

译码器和数据选择器实验报告Word下载.docx

《译码器和数据选择器实验报告Word下载.docx》由会员分享,可在线阅读,更多相关《译码器和数据选择器实验报告Word下载.docx(10页珍藏版)》请在冰豆网上搜索。

74LS00二输入端四“与非”门1片

74LS20四输入端双“与非”门1片

74LS139双2-4先译码器1片

74LS153双4选1数据选择器1片

实验容

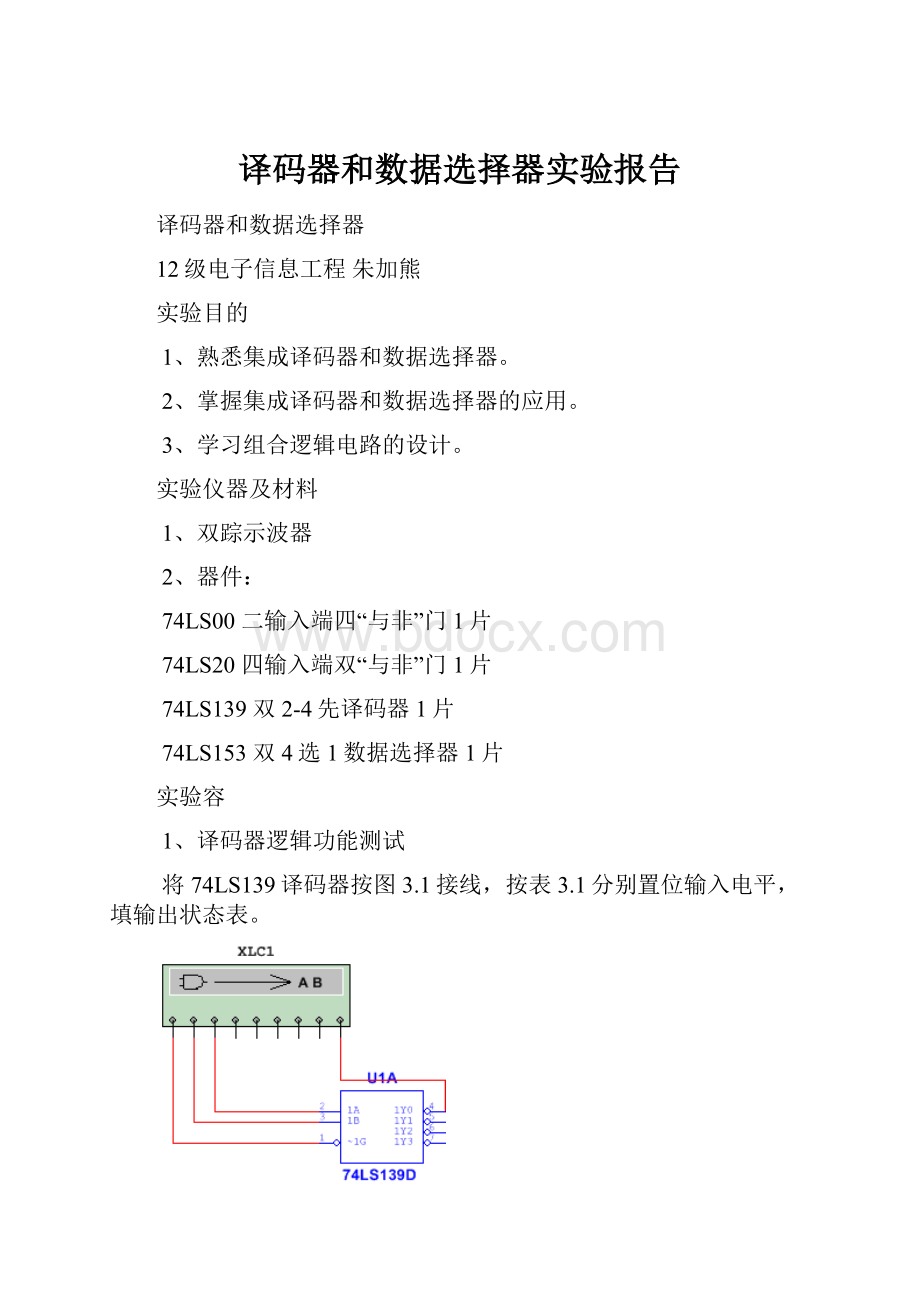

1、译码器逻辑功能测试

将74LS139译码器按图3.1接线,按表3.1分别置位输入电平,填输出状态表。

仿真结果

Y0

Y1

Y2

Y3

2、译码器转换

将双2-4线译码器转换为3-8译码器。

(1)、画出转换电路图。

(2)、在试验箱上接线并验证设计是否正确。

(3)、设计并填写该3-8线译码器逻辑功能表,画出输入、输出波形。

电路图

逻辑功能表

A

B

C

Y

0

0

1

Y1

Y2

Y3

Y4

Y5

Y6

Y7

注:

表中Y=Yi表示Yi=0,其余输出值为1

3、数据选择器的测试及应用

(1)、将双4选1数据选择器74LS153参照图3.2接线,测试其逻辑功能并填写功能表3.2.

(2)、将试验箱上4个不同频率的脉冲信号接到数据选择器4个输入端,将选择端置位,使输入端分别观察到4种不同频率的脉冲信号。

(3)、分析上述实验结果并总结数据选择器的作用。

输出控制

选择端

数据输入端

输出

E

A1A2

D3D2D1D0

H

XX

XXXX

L

LL

XXXL

XXXH

LH

XXLX

XXHX

HL

XLXX

XHXX

HH

LXXX

HH

HXXX

4、应用设计

(1)、用2-4线译码器74LS139和少量逻辑门设计一个一位全减器。

列出真值表和卡诺图,画出原理图,在实验箱上接线并验证设计是否正确。

(2)、用4选1数据选择器74LS153和少量逻辑门设计一个1位全加器。

列出真值表和卡诺图,画出逻辑图,在实验箱上接线并验证设计是否正确。

全减器

逻辑功能表

An

Bn

Cn

Cn+1

Dn

原理图

Cn+1

Sn

全加器

Ai

Bi

Ci

Ci+1

Si

1

仿真结果

Ci+1

组合逻辑电路的设计方法

1.进行逻辑抽象

1)确定输入变量和输出变量;

2)定义逻辑状态的含义;

3)列出逻辑真值表。

2.写出逻辑函数式。

3.选定器件的类型。

4.将逻辑函数化简成适当的形式。

5.根据化简后的逻辑函数式,画出逻辑图。

6.工艺设计。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 译码器 数据 选择器 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx

心理咨询班智力测验新教材PPT推荐.ppt

心理咨询班智力测验新教材PPT推荐.ppt