83线编码器1.docx

83线编码器1.docx

- 文档编号:22779518

- 上传时间:2023-04-27

- 格式:DOCX

- 页数:13

- 大小:454.20KB

83线编码器1.docx

《83线编码器1.docx》由会员分享,可在线阅读,更多相关《83线编码器1.docx(13页珍藏版)》请在冰豆网上搜索。

83线编码器1

8线-3线编码器的设计

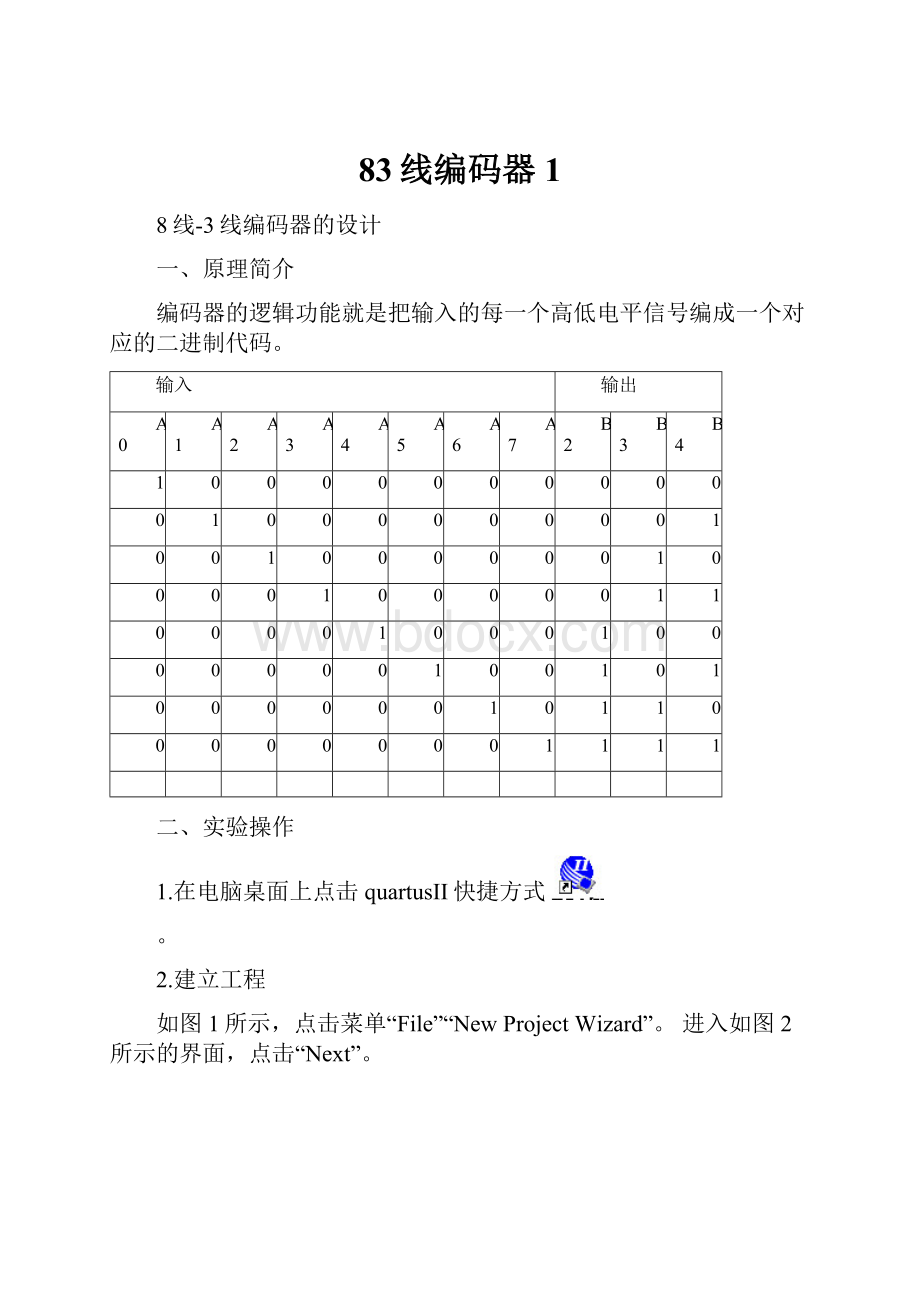

一、原理简介

编码器的逻辑功能就是把输入的每一个高低电平信号编成一个对应的二进制代码。

输入

输出

A0

A1

A2

A3

A4

A5

A6

A7

B2

B3

B4

1

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

0

0

0

1

0

1

1

0

0

0

0

0

0

0

0

1

1

1

1

二、实验操作

1.在电脑桌面上点击quartusII快捷方式

。

2.建立工程

如图1所示,点击菜单“File”“NewProjectWizard”。

进入如图2所示的界面,点击“Next”。

图1

进入如图3所示界面,确定工程项目的路径和名称。

.

图3

点击“Next”,进入如图4所示的界面,点击“Next”,进入如图54所示的界面,选择器件型号。

点击“Finish”完成设置。

图4

图5

3.建立VHDL文件

点击新建文件按钮

,在弹出的如图6所示的界面中,选“VHDLFile”。

图6

输入VHDL代码,如图7所示。

并保存文件,文件名应该与实体名一致,如该例子中为“bm8_3.vhd”,如图8所示。

代码如下:

LibraryIEEE;

UseIEEE.std_logic_1164.All;

Entitybm8_3is

port(a:

instd_logic_vector(7downto0);

b:

outstd_logic_vector(2downto0));

Endbm8_3;

Architectureoneofbm8_3is

begin

process(a)

begin

caseais

when"00000001"=>b<="000";

when"00000010"=>b<="001";

when"00000100"=>b<="010";

when"00001000"=>b<="011";

when"00010000"=>b<="100";

when"00100000"=>b<="101";

when"01000000"=>b<="110";

whenothers=>b<="111";

endcase;

endprocess;

endone;

图7

图8

4.编译文件

在项目导航栏“ProjectNegatior”中选择文件,点击鼠标右键,选“SetasTop-LevelEntity”。

如图9所示,点击编译按钮

。

图10为编译成功提示。

图9

图10

5.引脚设置

点击菜单

的

,如图22所示。

图22

进入如图23所示界面,在

栏中设置引脚,如图23所示。

图23

引脚设置如下:

a[7]PIN_7

a[6]PIN_8

a[5]PIN_9

a[4]PIN_10

a[3]PIN_11

a[2]PIN_12

a[1]PIN_13

a[0]PIN_14

b[2]PIN_39

b[1]PIN_40

b[0]PIN_41

点击

,再次编译,图24为编译成功提示。

图24

7.下载代码

点击菜单

的

,如图25所示。

进入如图26所示界面。

点击

,在图27界面中设置硬件为

。

图25

图26

图27

将

下面的方框选中,如图28所示。

打开实验箱电源按钮。

点击

下载文件代码到实验箱上,如图29所示。

图28

图29

8.观察实验现象

拨动实验箱的拨码开关SW3(见图30)的IO1~IO8,“ON”为高电平,“OFF”为低电平。

观察输出LED(见图31)中D1~D3的状态。

图30拨码开关

图31输出LED

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 83 编码器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《地质测量图绘制细则》.docx

《地质测量图绘制细则》.docx