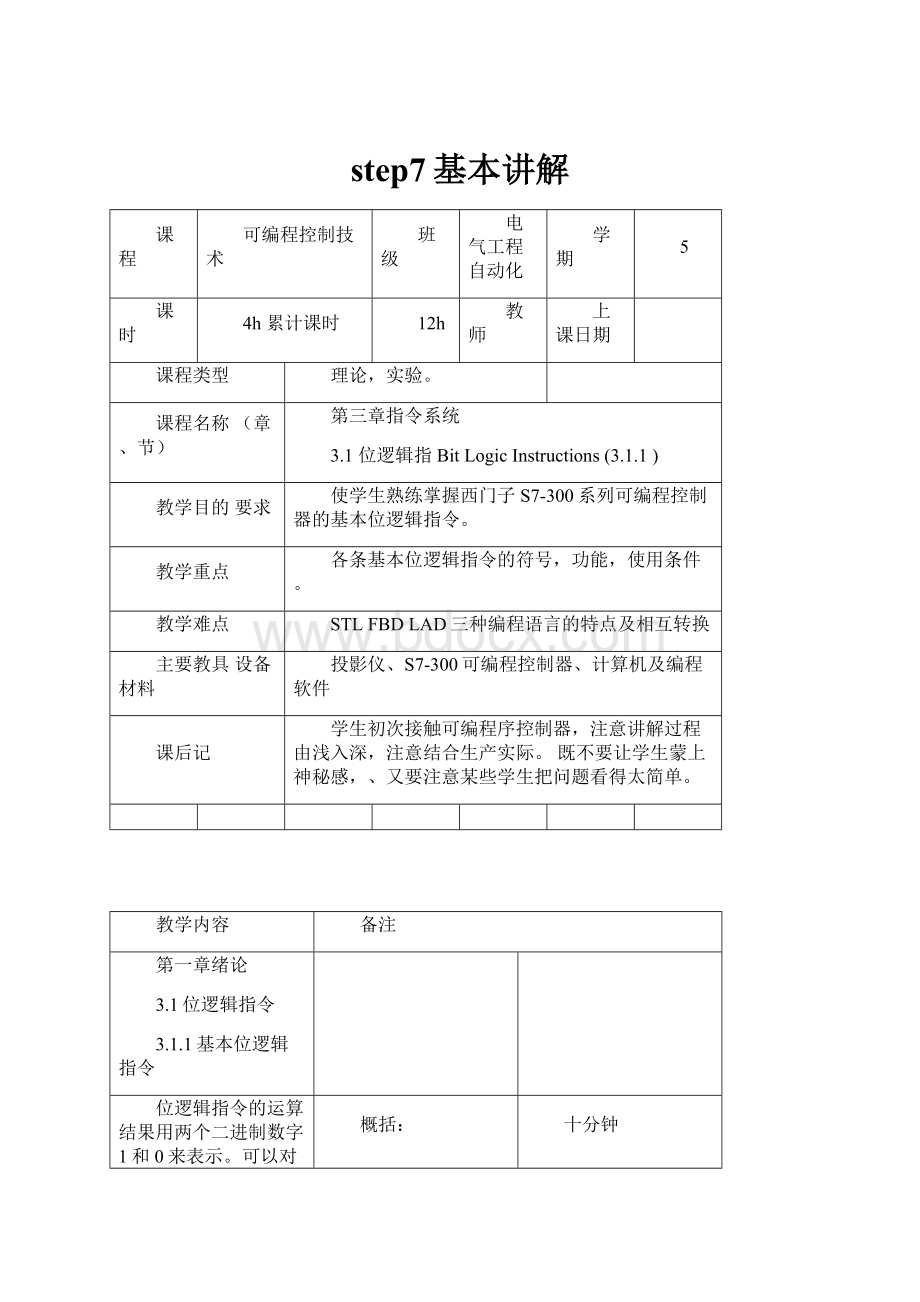

step7基本讲解Word文档下载推荐.docx

step7基本讲解Word文档下载推荐.docx

- 文档编号:22728116

- 上传时间:2023-02-05

- 格式:DOCX

- 页数:20

- 大小:127.45KB

step7基本讲解Word文档下载推荐.docx

《step7基本讲解Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《step7基本讲解Word文档下载推荐.docx(20页珍藏版)》请在冰豆网上搜索。

十分钟

语句表STL表示的基本位逻辑指令

AAnd逻辑“与”

ANAndNot逻辑“与非”

OOr逻辑“或”

ONOrNot逻辑“或非”

XExclusiveOr逻辑“异或”

XNExclusiveOrNot逻辑“异或非”

=Assign赋值指令

NOTNegateRLORLO取反SETSetRLO(=1)RLO=1CLRClearRLO(=0)RLO=0

SAVESaveRLOinBRRegister将RLO的状态保存到BR

边沿信号识别指令。

位逻辑指令的运算规则:

“先与后或”。

可以用括号将需先运算的部分括起来,运算规则为:

“先括号内,后括号外”。

梯形图LAD表示的基本位逻辑指令

---||---NormallyOpenContact(Address)常开触点

---|/卜--NormallyClosedContact(Address)常闭触点

---(SAVE)SaveRLOintoBRMemory

将RLO的状态保存到BR

XORBitExclusiveOR逻辑“异或”

---()OutputCoil输出线圈

---(#)---MidlineOutput中间标志输出

---|NOT|---InvertPowerFlowRLO取反

功能图FBD表示的位逻辑指令将在后面的指令详解中给出

利用投影仪

1•逻辑“与”操作

注意编程语言的三种表达方式及各自的特点。

当所有的输入信号都为“T,则输出为“T;

只要输入信号有一个不为“1”,则输出为“0”。

例3.1.1:

功能图(FBD语言如下:

Q4.Q

=

I0.0

I0.1

梯形图(LAD)语言如下:

10.0I0.1Q4.0

语句表(STL)语言如下:

AI0.0AI0.1

=Q4.0

2•逻辑“或”操作

只要有一个输入信号为“T,则输出为“T;

所有输入信号都为“0”,输出才为“0”。

例3.1.2:

当输入信号I0.0和I0.1有一个以上为“T时,输出信号Q4.0为1”。

当输入信号I0.0和I0.1都为“0”时,输出信号Q4.0才为0”。

10.0Q4.0

I0/1

语句表(STL)语言如下:

OI0.0

OI0.1

3•逻辑异或操作

当两个输入信号其中一个为“1”而另一个为“0”时,输出信号为

1”;

当两个输入信号都为“0”或者都为“T时,输出信号为“0”

XOR

Q3.1

I0.2

引导学生举出生活中异或关系的例子

例3.1.3:

功能图(FBD语言如下:

当输入信号I0.0为“1”而I0.2为“0”或者I0.0为“0”而I0.2为“1”时,输出信号Q3.1为“1”。

当输入信号I0.0和I0.2都为“0”或者I0.0和I0.2都为“1”时,输出信号Q3.1为“0”。

梯形图(LAD)语言如下:

3.1)

XI0.0

XI0.2

=Q3.1

4•逻辑取反操作

逻辑取反操作对逻辑运算结果RLO取反。

功能图(FBD符号:

梯形图(LAD符号:

TNOTI---

语句表(STL)符号:

NOT

例3.1.4:

只有当I1.0和I1.1相与的结果为“0”并且I1.2和I1.3相与的结果为“1”或I1.4为“1”时,输出Q4.0才为“1”;

否则Q4.0为“0”。

梯形图(LAD语言如下:

.11.011J

112I1.3

040

HHHnotF

TH1—InotH

Ik4

II——

AI1.0

AI1.1

A(

AI1.2

AI1.3

OI1.4

)

5

特别要讲清楚中间符号的作用

•中间输出符号

中间输出指令用于存储RLO的中间值,该值是中间输出指令前的位逻辑操作结果。

中间输出指令不能用于结束一个逻辑串,因此,中间输出指令不能放在逻辑串的结尾或分支的结尾处。

FED符号;

-address^

LAI>符吕

—

一

例3.1.5

M0.0的缓存器中存放着I1.0

M1.1的缓存器中存放着I1.2

M2.2的缓存器中存放着I1.4

和I1.1相与后取反的结果;

和I1.3相与后取反的结果;

的逻辑运算结果;

M3.3的缓存器中存放上述整个逻辑运算的结果

例3.1.6

J10I11Mt)0I2.2I1I3M1.1M2.2Q+0

pI一II_#1|一IImot卜併卜T#()

M0.0的缓存器中存放着I1.0和I1.1相与的结果;

M1.1的缓存器中存放着I1.0、I1.1、丨1.2和I1.3四个输入信号相与后取反的结果;

M2.2的缓存器中存放着整个逻辑运算的结果。

6•位逻辑操作规则:

重点强调

例3.1.7:

当输入信号I1.0和I1.1都为“1”,或输入信号I1.2和I1.3都为“1”时,输出信号Q3.1为“1”。

否则输出信号Q3.1为“0”。

梯形图(LAD语言如下:

|11.0I11Q3.1

牢记位逻辑运算的规则。

重点是在语句表中

O

例3.1.8:

当输入信号I1.0或I1.1为“T,并且I1.2

为“1”时,

功能图

输出信号Q3.1为“1”。

否则输出信号(FBD语言如下:

Q3.1为

或I1.3

0”。

I1.0

11.1

I1.2

I1.3

梯形图

语句表

A(

OI1.0

OI1.1

OI1.2

OI1.3)

Q3.1

16h

3.1位逻辑指令BitLogicInstructions(3.1.2〜3.1.4)

使学生熟练掌握西门子S7-300系列可编程控制器的置位/复位指令。

置位/复位指令的符号,功能,使用条件。

置位/复位指令的记忆功能。

置位/复位指令对于较熟悉继电一接触器控制的学生来说是个较新的概念。

同时又是非常重要的指令。

注意引导学生结合数字电路的RS触发器以及继

电一接触器系统中的“自保”结构充分理解。

3.1.2置位/复位指令

置位/复位指令根据RLO的值,来决定被寻址位的信号状态是否需要改强调“记忆功

变。

若RLO的值为1,被寻址位的信号状态被置1或清0;

若RLO是0,则被能”寻址位的信号保持原状态不变。

对于置位操作,一旦RLO为1,则被寻址信

号(输出信号)状态置1,即使RLO又变为0,输出仍保持为1;

对于复位操作,一旦RLO为1,则被寻址信号(输出信号)状态置0,即使RLO又变为0,输出仍保持为0。

语句表STL表示的置位/复位指令

RReset复位指令

SSet置位指令

梯形图LAD表示的置位/复位指令

---(S)SetCoil

---(R)ResetCoil

SRSet-ResetFlipRSReset-SetFlip功能图FBD表示的位逻辑指令

注意与普通线圈符号的不同

100

10.1

1.置位/复位线圈指令

例3.1.9:

当I0.0和I0.1输入都为“T或者I0.2输入为“0”时,

Q4.0被置位,即输出为“T;

不满足上述条件时,Q4.0的输出状态不变。

功能图(FBD语言如下:

AI0.0

AI0.1

ONI0.2

SQ4.0

例3.1.10:

当I0.0和I0.1输入都为“T或者I0.2输入为“0”时,Q4.0被复位,即输出为“0”;

ior——

101—

04C

10.2

—|R|

I00ID1Gr4O

1I1I◎I□2

RQ4.0

2.置位/复位双稳态触发器指令

如果置位输入端为“1”,复位输入端为“0”,则触发器被置位。

此

后,即使置位输入端为0,触发器也保持置位不变。

如果复位输入端为1,

置位输入端为“0”,则触发器被复位。

置位优先型RS触发器的R端在S端之上,当两个输入端都为1时,下面的置位输入端最终有效。

既置位输入优先,触发器被置位。

复位优先型SR触发器的S端在R端之上,当两个输入端都为1时,下面的复位输入端最终有效。

既复位输入优先,触发器被复位。

注意讲清楚置位优先型RS触发器和复位优先型SR触发器在功能图和语句表中的表示方法以及适用场合

Io.c

I0.D

ID.1

MD.0

例3.1.11

ad

二

A

RS

R

―C

£

Q4.D

SQ

H=|

3.1.3边沿信号识别指令1.RLC边沿信号识别指令

当信号状态变化时就产生跳变沿,当从0变到1时,产生一个上升沿

此节内容较难懂,适当慢一些。

下降沿信号识别指令

STL指寺裕式j

FN<

bit>

强调“边沿”的概念

(或正跳沿);

若从1变到0,则产生一个下降沿(或负跳沿)。

跳变沿检测的原理是:

在每个扫描周期中把信号状态和它在前一个扫描周期的状态进行比较,若不同则表明有一个跳变沿。

因此,前一个周期里的信号状态必须被存储,以便能和新的信号状态相比较。

-■address^

<

address>

—(N)

若CPU检测到输入有一个负跳沿,将使得输出线圈在一个扫描周期内通电。

对输入扫描的RLO值存放在存储位中。

在OB1的扫描周期中,CPU扫描并形成RLO值,若该RLO值是0且上次RLO©

是1,这说明FN指令检测到一个RLO的负跳沿,那么FN指令把RLO位置1。

如果RLO在相邻的两个扫描周期中相同(全为1或0),那么FN语句把RLO位清0。

1

例3.1.13

AI1,0I1.0_

FNM1.0M1.0

=Q4.0Q4.0

OBINq;

丨’1丨2丨勺丨4丨5丨6丨7丨直丨9|

若CPU检测到输入11.0有一个负跳沿,将使得输出Q4.0的线圈在一个扫描周期内通电。

对输入I1.0常开触点扫描的RLOfi(在本例中,此RLO正好与输入I1.0的信号状态相同)存放在存储位M1.0中。

弄清“上升沿”与“下降沿”的概念与区别

在OB1的扫描周期中,CPU对I1.0信号状态扫描并形成RLOfi,若该RLOfi是0且存放在M1.0中的上次RLOfi是1,这说明FN指令检测到一个RLO的负跳沿,那么FN指令把RLO位置1。

如果RLO在相邻的两个扫描周期中相同(全为1或0),那么FN语句把RLO位清0。

上升沿信号识别指令

STL指令格式:

FP<

hit>

^address*

FBD符昱

P

LAD符导

addres&

>

(P)

若CPU检测到输入有一个正跳沿,将使得输出线圈在一个扫描周期内通电。

对输入扫描的RLOfi存放在存储位中。

在OB1的扫描周期中,CPU扫描并形成RLOfi,若该RLOfi是1且上次RLOfi是0,这说明FN指令检测到一个RLO的正跳沿,那么FP指令把RLO位置1。

如果RLO在相邻的两个扫描周期中相同(全为1或0),那么FP语句把RLO位清0。

例3.1.14

OB1ScanCycltNo:

_J_2|B45|6|7|A9|

若CPU检测到输入I1.0有一个正跳沿,将使得输出Q4.0的线圈在一个扫描周期内通电。

对输入I1.0常开触点扫描的RLOfi(在本例中,此RLO正好与输入I1.0的信号状态相同)存放在存储位M1.0中。

在OB1的扫描周期中,CPU对I1.0信号状态扫描并形成RLOfi,若该RLOfi是1且存放在M1.0中的上次RLOfi是0,这说明FN指令检测到一个RLO的正跳沿,那么FP指令把RLO位置1。

如果RLO在相邻的两个扫描周期中相同(全为1或0),那么FP语句把RLO位清0。

注意与前面指令的区别

2•触点边沿信号识别指令

触点下降沿信号识别指令

<address1、

——MBl"

在0B1的扫描周期中,CPU对<address1>的状态与其上一个扫描周期的状态进行比较(上一个扫描周期的状态保存在<address2>中。

若该

<address1>状态是0且存放在<address2>中的上次状态是1,这说明NEGi指令检测到<address1>的负跳沿,那么NEG指令把RLO位置1。

如果<address1>在相邻的两个扫描周期中状态相同(全为1或0),那么NEG指令把RLO位清0。

例3.1.15

10.3

MEG

1U.4U4.U

Q

HH)

MBIT

10.0I01I0.2

M0..C

当输入信号

I0.0、I0.0、I0.2、I0.4全为“T并且I0.3

一个负跳变,则Q4.0输出一个扫描周期的正脉冲信号

触点上升沿信号识别指令

^addressl1-

POSQ

在OB1的扫描周期中,CPU对<address1>的状态与其上一个扫描周期的状态进行比较(上一个扫描周期的状态保存在<address2>中。

<address1>状态是1且存放在<address2>中的上次状态是0,这说明POS指令检测到<address1>正跳沿,那么POS指令把RLO位置1。

如果<address1>在相邻的两个扫描周期中状态相同(全为1或0),那么POS指令把RLO位清0。

10.010.1102

10S

10.4Q40

POS

—|H)

MC.D——

例3.1.16

当输入信号I0.0、I0.0、I0.2、I0.4全为“T并且I0.3有一个正跳变,则Q4.0输出一个扫描周期的正脉冲信号。

强调尽对RLQB作

3.1.4RLO置位、清零、保存指令

置位指令符号:

SET

功能:

RLO=1

复位指令符号:

CLR

RLO=0

例3.1.17

STLProgram

SignalState

ResultofLogicOperation(RLO)

SET1

=NIDlC

■HIM

=M16.0

CLR

=Miai

=M1Di2

RLO保存指令

符号:

SAVE

(RLO)—BR

说明:

将RLO的状态保存到状态字寄存器中的BR位中

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- step7 基本 讲解

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx