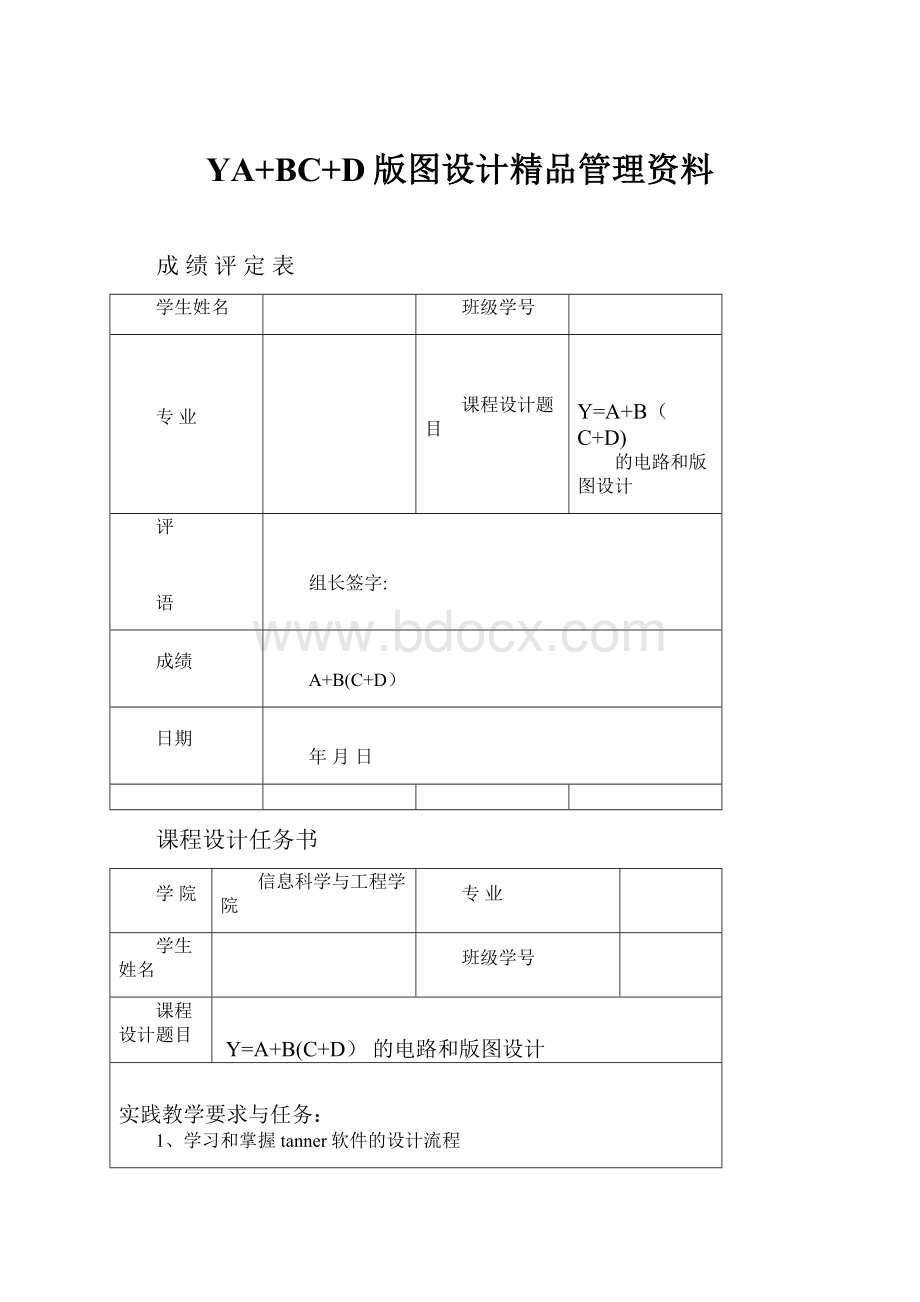

YA+BC+D版图设计精品管理资料Word文件下载.docx

YA+BC+D版图设计精品管理资料Word文件下载.docx

- 文档编号:22632405

- 上传时间:2023-02-04

- 格式:DOCX

- 页数:14

- 大小:372.72KB

YA+BC+D版图设计精品管理资料Word文件下载.docx

《YA+BC+D版图设计精品管理资料Word文件下载.docx》由会员分享,可在线阅读,更多相关《YA+BC+D版图设计精品管理资料Word文件下载.docx(14页珍藏版)》请在冰豆网上搜索。

第一周

周一:

教师布置课设任务,学生收集资料,做方案设计。

周二:

熟悉软件操作方法。

周三~四:

画电路图

周五:

电路仿真。

第二周

周一~二:

画版图.

周三:

版图仿真.

周四:

验证。

周五:

写报告书,验收.

指导教师:

年月日

专业负责人:

学院教学副院长:

1绪论

1。

1设计背景

随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证[2].在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由TannerResearch公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S—Edit,T-Spice,W—Edit,L—Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度.

L—EditPro是TannerEDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件.L—EditPro包含IC设计编辑器(LayoutEditor)、自动布线系统(StandardCellPlace&Route)、线上设计规则检查器(DRC)、组件特性提取器(DeviceExtractor)、设计布局与电路netlist的比较器(LVS)、CMOSLibrary、MarcoLibrary,这些模块组成了一个完整的IC设计与验证解决方案.L—EditPro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

2设计目标

1。

用tanner软件中的原理图编辑器S—Edit编辑Y=A+B(C+D)电路原理图。

2。

用tanner软件中的W-Edit对Y=A+B(C+D)的电路进行仿真,并观察波形。

3。

用tanner软件中的L—Edit绘制Y=A+B(C+D)的版图,并进行DRC验证.

4。

用W-Edit对Y=A+B(C+D)的版图电路进行仿真并观察波形。

5。

用tanner软件中的layout—Edit对Y=A+B(C+D)进行LVS检验观察原理图版图的匹配程度.

2.Y=A+B(C+D)的电路和版图设计

2。

1电路原理图

Y=A+B(C+D)的电路原理如图2。

1所示。

当输入的信号ABCD满足0000、0001,或0010等,即满足上拉网络导通的条件时,输出Y为高电平。

当输入信号为1010或1000等满足下拉网络导通的条件时,输出Y为低电平.实现Y=A+B(C+D)的逻辑运算.通过真值表可以得出当输入信号为0000、0001、0010、0011、0100时输出Y为高电平,其余的输入信号可以的到低电平.

图2。

1Y=A+B(C+D)的电路原理图

2Y=A+B(C+D)的电路仿真观察波形

给Y=A+B(C+D)的输入加激励,高电平为Vdd=5V,低电平为Gnd,将输入信号设置成不同的周期,ABCD信号的周期分别为800ns、400ns、200ns和100ns。

此时能将输入为0000-1111所产生的结果都输出。

并添加输入输出延迟时间,进行仿真,并输出波形;

波形图如图2。

2所示。

当输入为0000、0001、0010、0011、0100时输出为高电平。

其余的输出都为低电平。

由于竞争冒险,所以将上升延时下降延时时间降低。

再将B信号的输入提前10ns输入来去掉竞争冒险产生的毛刺。

图2.2Y=A+B(C+D)电路输入输出波形图

2.3Y=A+B(C+D)的版图绘制

用L—Edit版图绘制软件对Y=A+B(C+D)电路进行版图绘制,同时进行DRC验证,查看输出结果,检查无错误;

版图和输出结果如图2.3所示。

在对节点进行标注时注意输入法的设置要使用美式键盘,否则会在生成网表时产生错误.

图2.3Y=A+B(C+D)与或门电路版图及DRC验证结果

4Y=A+B(C+D)的版图仿真观察波形

与Y=A+B(C+D)电路原理图仿真相同,添加激励、电源和地,同时观察输入输出波形;

波形如图2。

4所示.Y=A+B(C+D)电路的版图仿真波形与原理图的仿真输出波形基本一致,并且符合输入输出的逻辑关系,电路的设计正确无误。

同样为了去掉竞争冒险我将B输入信号提前10ns输入.

图2。

4Y=A+B(C+B)版图输入输出波形图

2.5LVS检查匹配

用layout—Edit对Y=A+B(C+D)电路进行LVS检查验证,首先添加输入输出文件即电路原理图和版图的输出网表分别为.sp文件和。

spc文件,选择要查看的输出,在进行匹配时要现将电路原理图和版图的输入激励进行屏蔽否则会在匹配过程中产生警告。

观察输出结果检电路原理图与版图的匹配程度,输出结果如图2.5所示。

5Y=A+B(C+D)电路的LVS检查匹配图

从以上可以看出完全匹配。

这里为了匹配时无警告已经将输入激励和电源屏蔽掉

总结

经过多次的修改和调试,本次设计经过验证,可以达到所需的功能,达到了设计的要求。

以下是本次试验的心得:

在实验的开始阶段,对所设计的电路进行了波形仿真,发现波形仿真的结果有竞争冒险的毛刺,为了去除竞争冒险我将上升下降延时变小、将时钟周期变大,同时将B信号提前10ns输入。

在进行版图的网表生成时注意网表上标注的节点要使用美式键盘输入否则网表上会出现错误的节点信息。

在进行原理图和版图对比匹配时要注意屏蔽掉输入的电源和激励。

我觉得我们学习不能完全以来波形仿真,否则,出现任何一点小的误差就会导致整个文件系统的编译出错。

总之,模拟集成电路版图设计作为前沿学科,对于我们专业的学生来说,学习对我们知识面以及运用知识的能力的提高有很大的帮助。

相信自己学习的脚步不会停止!

感谢老师孜孜不倦的教诲。

相信在学习过程中自己思维能力、学习能力、思考方式的提高,定会在以后的学习过程中给我带来很大的帮助。

参考文献

[1]廖裕平,陆瑞强。

Tannerpro集成电路设计与布局实战指导。

全华科技图书股份有限公司印行,2006.

[2]张志刚等著。

模拟电路版图的艺术。

科学出版社,2009.

附录一电路原理图网表:

*SPICEnetlistwrittenbyS-EditWin327。

03

*WrittenonJul2,2013at23:

31:

28

*Waveformprobingcommands

*.probe

。

includeD:

\tanner\TSpice70\models\ml2_125.md

.optionsprobefilename=”D:

\tanner\LIE\Module0.dat”

+probesdbfile="

D:

\tanner\LIE\LIE。

sdb”

+probetopmodule=”Module0”

*。

paraml=0。

5u

*VddVddGnd5

*。

tran/op10n800nmethod=bdf

printtranv(A)v(B)v(C)v(D)v(Y)

*vaAGNDPULSE(05400n0。

1n0.1n400n800n)

*vbBGNDPULSE(05210n0。

1n0.1n200n400n)

*vcCGNDPULSE(0590n0.1n0.1n100n200n)

*vdDGNDPULSE(0550n0。

1n0。

1n50n100n)

*Maincircuit:

Module0

M1YBN3GndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M2GndDN3GndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M3N3CGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M4YAGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M5N1AVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M6N2CN1VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M7YBN1VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M8YDN2VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

*Endofmaincircuit:

附录二版图网表:

*CircuitExtractedbyTannerResearch'

sL—EditVersion9.00/ExtractVersion9。

00;

*TDBFile:

D:

\tanner\LIE\lie。

tdb

*Cell:

Cell0Version1。

67

*ExtractDefinitionFile:

.。

\LEdit90\Samples\SPR\example1\lights。

ext

*ExtractDateandTime:

07/05/2013—09:

38

.includeD:

*Warning:

LayerswithUnassignedAREACapacitance。

*〈PDiffResistorID〉

*〈PolyResistorID>

*〈NDiffResistorID〉

*<

Poly2ResistorID〉

*〈PBaseResistorID>

*〈NWellResistorID〉

LayerswithUnassignedFRINGECapacitance。

*〈Poly1—Poly2CapacitorID>

*〈PolyResistorID>

*〈NDiffResistorID>

*<

Poly2ResistorID>

*〈PBaseResistorID〉

*〈NWellResistorID>

*〈PadComment〉

*Warning:

LayerswithZeroResistance。

*〈NMOSCapacitorID>

Poly1—Poly2CapacitorID>

*〈PMOSCapacitorID〉

*〈PadComment>

*NODENAMEALIASES

*1=C(38,—35)

*2=D(30.5,-35)

*3=B(22,-34。

5)

*4=A(14,—34。

*5=GND(8。

5,—18.5)

*6=Vdd(9.5,37.5)

*7=Y(58。

5,7。

optionsprobefilename=”D:

\tanner\LIE\Module0。

dat”

*+probesdbfile=”D:

\tanner\LIE\LIE.sdb”

*+probetopmodule="

Module0"

*vaAGNDPULSE(05400n0。

1n400n800n)

*vbBGNDPULSE(05210n0.1n0。

1n200n400n)

*vcCGNDPULSE(0590n0。

1n0.1n100n200n)

1n0.1n50n100n)

M19C10VddPMOSL=2uW=6u

*M1DRAINGATESOURCEBULK(38164022)

M210DYVddPMOSL=2uW=6u

*M2DRAINGATESOURCEBULK(30163222)

M3YB9VddPMOSL=2uW=6u

*M3DRAINGATESOURCEBULK(22162422)

M49AVddVddPMOSL=2uW=6u

*M4DRAINGATESOURCEBULK(14161622)

M58CGNDGNDNMOSL=2uW=6u

*M5DRAINGATESOURCEBULK(38-1140—5)

M6GNDD8GNDNMOSL=2uW=6u

*M6DRAINGATESOURCEBULK(30-1132-5)

M78BYGNDNMOSL=2uW=6u

*M7DRAINGATESOURCEBULK(22—1124—5)

M8YAGNDGNDNMOSL=2uW=6u

*M8DRAINGATESOURCEBULK(14-1116-5)

*TotalNodes:

10

*TotalElements:

8

*TotalNumberofShortedElementsnotwrittentotheSPICEfile:

0

*ExtractElapsedTime:

0seconds

END

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- YA BC 版图 设计 精品 管理 资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx