EDA课程设计数字抢答器Word文档格式.docx

EDA课程设计数字抢答器Word文档格式.docx

- 文档编号:22273210

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:27

- 大小:344.27KB

EDA课程设计数字抢答器Word文档格式.docx

《EDA课程设计数字抢答器Word文档格式.docx》由会员分享,可在线阅读,更多相关《EDA课程设计数字抢答器Word文档格式.docx(27页珍藏版)》请在冰豆网上搜索。

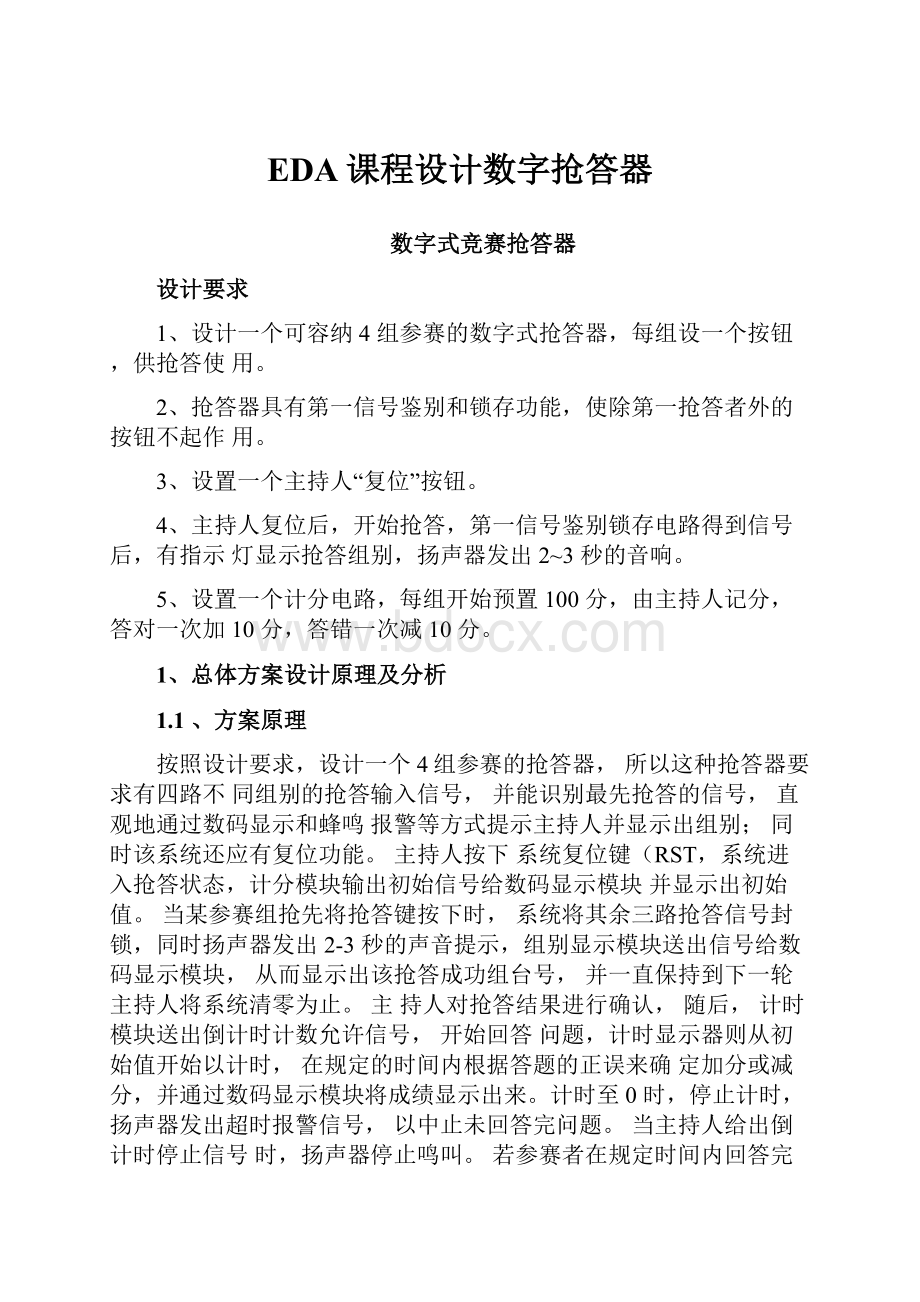

■«

I.4

qdjb

rst

LEDA

EN

LEDB

sO

LEDC

s1

LEDD

s2

false[3..O]

states[3..O]

\inst.

图2抢答鉴别模块框图

2.2、计时模块

在这个模块中主要实现抢答过程中的计时功能,在有组别抢答后开始倒计

时,若在规定时间没人回答,则超时报警。

其中有系统复位信号rst;

抢答使能

信号s;

无人抢答警报信号warn;

计时中止信号stop;

计时十位和个位信号tb,ta。

厂Tq"

"

-—-—-

;

—

elk

warn

ta[3..O]

s

stop

tb[3..O]

inst

图3计时模块框图

2.3、计分模块

抢答计分电路的设计一般按照一定数制进行加减即可,但随着计数数目的增加,要将计数数目分解成十进制并进行译码显示会变得较为复杂。

为了避免该种情况,通常是将一个大的进制数分解为数个十进制以内的进制数,并将计数器级

连。

但随着数位的增加,电路的接口也会相应增加。

因此,本设计采用IF语句

从低往高判断是否有进位,以采取相应的操作,既减少了接口,又简化了设计。

其电路框图如下,该模块输入信号为加分选择信号add和组别选择信号

chose[3..0],其中,加分选择信号add高电平有效,有效时对组别选择信号

chose[3..0]选择的参赛组进行加分;

组别选择输入信号chose[3..0]即抢答鉴

别模块的输出信号states[3..0]。

输出信号分别对应四组竞赛者的得分。

■■i.4b■ab-■・』s.■-・■■l■-■«

a.■-aa

”

aa2[3Oi]

1

a

add

aa1[3..O]

j

F

1chose[3..O]

a^O[3..O]

■a

bb2[3..O]

r

bb1|3..D]

■

bbO13..O]

■fl

cc2[3..O]

cd[3..O]

4

ccO[3..O]

百

dd2|3.Oi]

I

dd1[3.0]

ddO[3..D]

:

?

inst

I•■■■■,*■-!

I•-I!

■■!

■■■■Ia-

1.1.・fr|riv尸・vigrinpvra.i■

•

图4计分模块框图

2.4、译码显示模块

译码显示模块用于显示每组选手的分数,计时的时间等信息。

显示电路的实质就是一个简单的LED共阴极显示模块的译码器。

7段数码管LED常用的一般8字型为a,b,c,d,e,f,g,P,其中P为小数点,共阴LED低电平有效。

在这里我们不需要用到小数点位,因此用位宽为7的矢量表示7段数码管即可。

7段LED共阴极显示模块的框图如图所示。

其中,IN4[3…0]为输入信号,以4位2进制数表示;

OUT7[6…0]为输出信号,将输入的二进制数译码显示为十进制数字的0~9。

\ymxsi

■I

V

¥

•in4[3.r0]

out7[6„0]

jinst

图5译码显示模块框图

2.5、报警模块

在这个模块中主要实现抢答过程中的报警功能,当主持人按下控制键,有限时间内有人抢答,指示灯显示抢答组别,扬声器发出2~3秒的音响。

即有效电平输入信号i;

状态输出信号q。

ALARM

'

CLK

Q

3

■r

二

.•一“一=—

■--■--J.

图6报警模块框图

2.6、整体框图

从上述设计方案中我们可以大致得到数字竞赛抢答器的系统框图,如下图所

示,其中抢答时钟信号clk2;

系统复位信号rst;

抢答使能信号s;

抢答状态显示信号states;

计时十位和个位信号tb,ta。

图7抢答器系统框图

3、仿真结果

3.1、抢答鉴别模块仿真

抢答鉴别模块的仿真波形图如图所示。

当鉴别模块的清零复位信号rst为高电平时,无论四组参赛者谁按下抢答按钮,系统输出均为零,同时组别显示端输出信号也显示为零;

当清零信号rst为低电平时,s0、si、s2、s3四组参赛者谁先按下抢答按钮,其对应的显示灯LEDx亮起,states[3..0]输出抢答成功的选手编号。

RMasieiTimeEI-ac120ns■<

»

|Porta77235nsOnleivd:

79435115Sladl:

End

图8抢答鉴别模块仿真波形图

3.2计时模块

计时模块的仿真波形如图所示。

实现了抢答过程中的计时功能,在有抢答开始后进行30秒的倒计时,并且在30秒倒计时后无人抢答显示超时并报警。

MasterTheBar

12龙5n«

”*|Pontef1127m

ln(ef¥

d:

455psSlail:

End.

Sene

Vtlue

)ps320.0ns610.0ns9G9.0ns1*iii

.28惦1.6he1.92us2.24ue2.56us2.86ms3.!

he3.52us3.64us|j[|1H|111

L9.TI

:

9僭m

J

dlt

Ai

~LTTjriurTTTj-rijjn-jnjj~Tj—Ljri-j—i—n_n_i

A

E

ElOp

k

Qu

A[<

毎E

□tb

JL[i

vara

Al

15

图9计时模块仿真波形图

3.3计分模块仿真

系统设计过程中,当计分复位端RST=1时,并且组别输入信号CHOSE=0000,其中的组别输入信号是抢答鉴别模块的输出信号,计分器复位,此时以上四组都

不会产生加减分操作。

然而当计分复位端RST=0时,此时计分器可以计分。

当

CHOS=000时,组别显示为A组,此时主持人利用计分器对A组进行加减分操作;

当CHOS=001时,组别显示为B组,此时主持人则利用计分器对B组进行加减分操作,以此类推。

下图仿真为A组回答正确,加分。

图10计分模块仿真波形图

3.4译码模块仿真

当in4=

0000"

out7输出"

0111111"

此时数码管显示

0;

II

0001"

0000110"

1;

0010"

1011011"

2;

0011"

1001111"

3;

当in4="

0100"

1100110"

4;

0101"

1101101"

5;

0110"

1111101"

6;

0111"

0000111"

7;

1000"

1111111"

8;

1001"

1101111"

9;

&

72n:

Slat

伽E

阳於

0iiA

rlj

祸

B拠

E〔二

弘同仏绚九御邛5

5勒W血则MOO.T20.0,fflCO

那闵]5ns

]

JD;

(\D0L0\恥\

0:

OJ

JDL01IOLIOjDllljKfflX切I

mi專

1就DC0011011011011\1O011LI1llffl]

[[打山血ii血伽ii址山i:

i?

noun\

mJ

ii11114111111H111111

||

|

111111

11

1!

1I

ii

\1iii■iiiii

11iiiiiii1l<

Iii

iiiiiiiiiiiiiii

11i11ij11

111111111111H1

11111111111111

i1i

iii

i|i

111

II1III

册ntIrte'

^at

图11译码显示模块仿真波形图

3.5、报警模块仿真

在这个模块中主要实现抢答过程中的报警功能,当主持人按下控制键,有限时间内如果人抢答或是计数到时蜂鸣器开始报警,有效电平输入信号i;

状态输出信号q。

仿真如下图。

MsteiTbieBfir17,3?

5ns

0胖Inle胡,

■17.30reStat

/iLiifiit

17.38>

i

1>

]

口

1F1

q

A0

DKK.QH5恸Qps蛆』咋3200MQ.Om刼.[监56D.OK&

40-1?

£

Q.Or.sSW-Oib3BD.QK960.Dns

n.375m

J

图12报警模块仿真波形图

3.6、整体仿真

对电路整体进行仿真,得出如下仿真波形图12。

图中,当复位信号rst为

高电平时,系统所有信号都清零;

当主持人按下开始键,抢答器开始工作。

Valuft

15.&

妙。

El

B

c

屮

dk

kl

cll£

ki

35

<

>

6

e

f

妙号

13巾

A[i

n

k1

JOTlt

lyIS

也T

*1目

11

Ai

L^19

e2

s3

MastsTimeBar.

15.675rwj►

Pointer.

975196usInleivjl.

975.54usSlst:

327.68ue

655.36us

9B3.04us

163Bns

1.96&

ms

Jps

1075ns

_Li~

「ril

imi

iiiil

j【iii

2.294ms

-rLrLrLrLrL-L-LrLrLrLrLr-T-rLrLrLrLrLrLrLrL-LrLrL

iiiiimirni

III

JII|;

;

l~7r-LJLT-LJLJ^

图13整体仿真波形图

4、原理连线图

根据系统设计要求,将各模块连线得到如下系统框图。

主持人按下使能端

EN抢答器开始工作。

四位抢答者谁先按下抢答按钮,则抢答成功,对应的显示

灯亮起,并通过显示电路模块显示参赛编号。

抢答成功的选手进入答题阶段,如果正确回答问题,则加分信号add有效,给相应的参赛组加分。

如果复位信号rst有效,使得抢答器在下一轮抢答前,其抢答成功的组别判断恢复为初始状态,开始新一轮抢答。

图14原理连线图

5、致谢

对于此次课程设计,首先我得诚挚的感谢我的指导老师,从设计、整改及论文的定稿过程中,自始至终都倾注着老师的心血。

老师以严谨的治学之道、宽厚仁慈的胸怀、积极乐观的生活态度,兢兢业业的工作作风为我树立了学习的典范,他们的教诲与鞭策将激励我在学习和生活的道路上励精图治,开拓创新。

他们渊

博的知识、开阔的视野和敏锐的思维给了我深深的启迪。

我真诚地谢谢老师们的指导和关怀。

于个人,通过这次课程设计,我进一步加深了对电子设计自动化的了解。

并

进一步熟练了对Quartusll软件的操作。

EDA这门课程也不像学习理论般那么空洞,有了更加贴切的了解及运用。

做课程设计时,先查阅相关知识,把原理吃透,确定一个大的设计方向,在按照这个方向分模块的把要实现的功能用流程图的形式展示。

最后参照每个模块把输入和输出引脚设定,运用我们所学的VHDL语言

进行编程。

总之,通过这次的设计,进一步了解了EDA技术,收获很大,对软件编程、排错调试、相关仪器设备的使用技能等方面得到较全面的锻炼和提高。

6、详细仪器清单

名称

型号

数量

计算机

联想

QuartusII开发软件

9.0

EDA/SOP实验开发系统

GW48-PK2

参考文献

[1]孙俊逸.EDA技术课程设计.华中科技大学出版社.2008.2-12

[2]潘松.EDA应用技术.北京理工大学出版社.2003

[3]徐志军.EDA技术与PLD设计[M].北京科学出版社.2002

[4]黄仁欣.EDA技术实用教程.清华大学出版社.2004

[5]崔建明.电工电子EDA仿真技术.北京高等教育出版社,2004

[6]

.2007

曹昕燕、周风臣、聂春燕.EDA技术试验与课程设计.清华大学出版社

[7]谢自美.电子线路设计实验测试.华中科技大学出版社.1999

[8]赵世强、许杰.电子电路EDA技术.西安电子科技大学出版社.2001

[9]江国强.EDA技术习题与实验.电子工业出版社.2012

[10]高有堂.EDA技术及应用实践.清华大学出版社.2006-08

附录

VHDL程序

1)抢答鉴别模块

libraryieee;

useieee.std_logic_1164.all;

entityqdjbis

port(rst:

instd_logic;

EN:

s0,s1,s2,s3:

LEDA:

outstd_logic;

LEDB:

LEDC:

LEDD:

false:

outstd_logic_vector(3downto0);

states:

outstd_logic_vector(3downto0));

endqdjb;

architectureoneofqdjbis

signaltmp:

std_logic_vector(3downto0);

signaltag:

std_logic;

begintmp<

=s0&

s1&

s2&

s3;

process(rst,EN,s0,s1,s2,s3,tmp)begin

ifrst='

1'

THENstates<

="

LEDA<

='

0'

LEDB<

LEDC<

LEDD<

false<

tag<

elsifEN='

then

ifs0='

false(3)<

endif;

ifs1='

thenfalse

(2)<

endif;

ifs2='

false

(1)<

ifs3='

thenfalse(0)<

else

false<

iftag='

iftmp="

states<

elsiftmp="

endprocess;

endone;

2)计时模块

useieee.std_logic_unsigned.all;

entityjsis

port(clk,rst,s,stop:

warn:

ta,tb:

bufferstd_logic_vector(3downto0));

endjs;

architectureoneofjsissignalco:

std_logic;

beginp1:

process(clk,rst,s,stop,ta)

begin

orstop='

thenta<

elsifclk'

eventandclk='

thenco<

ifs='

thenifta="

co<

elseta<

=ta-1;

endprocessp1;

p2:

process(co,rst,s,stop,tb)begin

then

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 课程设计 数字 抢答

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx

AQL及抽样方案PPT课件下载推荐.ppt

AQL及抽样方案PPT课件下载推荐.ppt