485总线设计方案加上位机扩展Word格式文档下载.docx

485总线设计方案加上位机扩展Word格式文档下载.docx

- 文档编号:22256814

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:8

- 大小:366.46KB

485总线设计方案加上位机扩展Word格式文档下载.docx

《485总线设计方案加上位机扩展Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《485总线设计方案加上位机扩展Word格式文档下载.docx(8页珍藏版)》请在冰豆网上搜索。

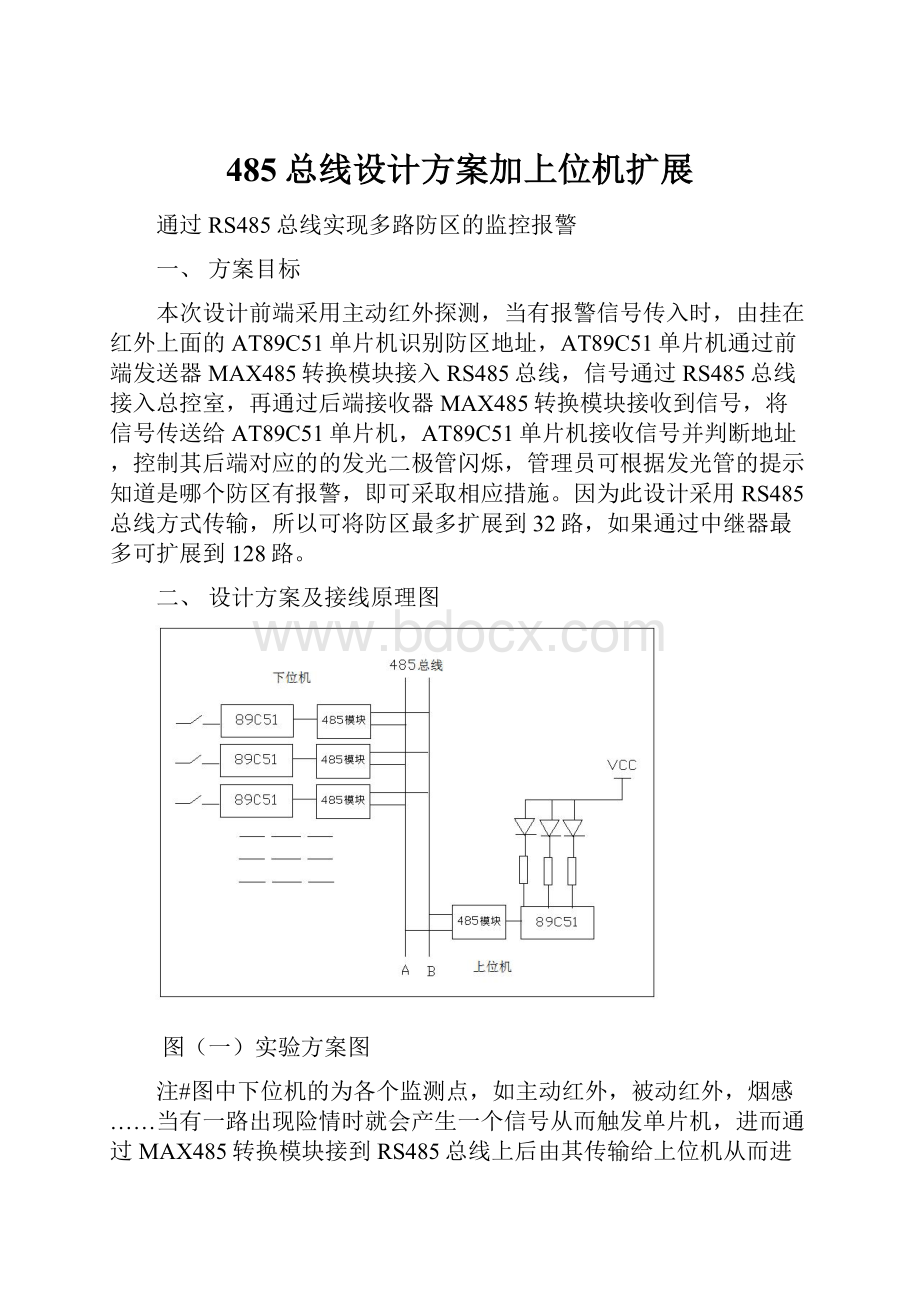

按理C51的有四个接口动可以驱动,当防区多的话必然不够,因此需要扩展,我们采用的是利用单片机与74HC164等若干芯片实现对其扩展,类似于中继器,从而进行扩展……

图

(二)接线图(上位机未扩展)

注#图中的接线图仅画了一路来表示,实际中有N路,先用一路与上位机尝试实现通信……

三、实现报警的信号能被单片机识别的思路

图中AT89C51单片机P1口接主动/被动红外探测,单片机识别的语言是高级语言,即二进制。

因此直接根据红外是否被出发作为二进制的开关量对前端的防区进行定义。

当单片机AT89C51接收到红外传来的信号时,单片机用TXD、RXD端口将信号通过MAX485芯片的RO、DI接入到RS485的A、B总线上面,后端同样通过MAX485芯片A、B接收信号通过RO、DI接入到AT89C51单片机的TXD、RXD进行通信,实现对前端地址的识别。

后端接收到前端防区来的触发信号时,控制后端相应地址的发光二极管发光。

如果要扩展多路后端接收单片机可通过P0口接到74LS373芯片进行扩展。

其中应注意的是所有AT89C51单片机的XTAL1/XTAL2端口应接11.0592MHZ的晶振,满足前后端波特率误差的要求。

后端接收的单片机RET端口接复位电路,当检查报警完毕之后管理员可按下复位按钮复位,重新进行下一轮的监控。

四、MAX485芯片资料

图(三)MAX485引脚和结构图

RO:

接收器输出端。

若A比B大200mv,RO为高;

若A比B小200mv,RO为低。

/RE:

接收器输出使能端。

RE为低时,RO有效,RE为高时,RO为高阻态。

DE:

驱动器输出使能端。

若DE为高,驱动输出A和B有效;

若DE为低,它们成高阻状态,若驱动器输出有效,器件作为线驱动使用,RE为低,器件作线接收使用。

DI:

驱动器输入。

DI为低,将迫使输出为低;

若DI为高,将迫使输出为高。

GND:

接地。

B:

反相接收器输入和反相驱动器输出。

A:

同相接收器输入和同相驱动器输出。

MAX485芯片是RS485通信的低功率收发器。

MAX的驱动器变化率没有限制,最大传输速率可达2.5Mbit/s,传输距离为1.2km。

MAX485芯片采用单+5V电源供电,额定电流为300μA,总线上可挂接32个收发器。

MAX485有8个引脚,当驱动器使能端DE和接收器使能端/RE禁止时,驱动器和接收器输出为高阻态。

RO和DI分别为接收器输出端和驱动器输入端,只要A、B端通过电阻对应连接,即可实现信息传输。

MAX485采用双线半双工方式,串行通信的波特率为9.6kbit/s,AT89C51单片机的晶振相应的选为11.0592MHZ,即可满足系统对波特率误差的要求。

它完成将TTL电平转换为RS-485电平的功能。

从图中可以看出,MAX485芯片的结构和引脚都非常简单,内部含有一个驱动器和接收器。

RO和DI端分别为接收器的输出和驱动器的输入端,与单片机连接时只需分别与单片机的RXD和TXD相连即可;

/RE和DE端分别为接收和发送的使能端,当/RE为逻辑0时,器件处于接收状态;

当DE为逻辑1时,器件处于发送状态,因为MAX485工作在半双工状态,所以只需用单片机的一个管脚控制这两个引脚即可;

A端和B端分别为接收和发送的差分信号端,当A引脚的电平高于B时,代表发送的数据为1;

当A的电平低于B端时,代表发送的数据为0。

在与单片机连接时接线非常简单。

只需要一个信号控制MAX485的接收和发送即可。

RO:

接收器输出端,连接单片机串口的RXD。

接收器的输入端,连接单片机串口的TXD。

A、B:

MAX485芯片传输之间的接口,需要连接两个120Ω的电阻,削弱甚至消除信号的反射。

五、RS485总线特点

图(四)RS485总线差分电路平衡电路

RS485总线方式采用差分平衡电路(如上图),其中一根导线上的电压是另一根导线上的电压取反。

接收器的输入电压为这两根导线电压的差值(VA-VB)。

差分电路的最大优点是抑制噪声,由于在它的两根信号线上传递着信号相同、方向相反的电流,而噪声电压往往在两根导线上同时出现,一根导线上的噪声电压会被另一根导线上的噪声电压抵消,因而可以极大的削弱噪声对信号的影响。

差分电路不受节点间接地电平差异的影响。

在非差分电路中,多个信号共用一根接地线,长距离传输时,不同节点接地线的电平差异可能相差好几伏,甚至会引起信号的误读。

差分电路则完全不会受到接地电平差异的影响。

但应该指出的是,RS485标准没有规定连接器、信号功能和引脚分配。

要保持两根信号线相邻,两根差动导线应该位于同一根双绞线内。

引脚A和B不要调换。

RS485在点对点的网络中,使用总线型。

它的端口都采用半双工通信方式。

有多个驱动器和多个接收器共享一条信号通道。

理想情况下它需要2个终端电阻,一般用2个120Ω电阻是作为总线的终端电阻,其阻值等于传输电缆的特性阻抗,可以削弱甚至消除信号的反射。

六、AT89C51单片机部分引脚资料

P0口:

P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:

P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

P3.0RXD(串行输入口)。

P3.1TXD(串行输出口)。

RST:

复位输入。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

XTAL1:

反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2:

来自反向振荡器的输出。

振荡器特性:

XTAL1和XTAL2分别为反向放大器的输入和输出。

该反向放大器可以配置为片内振荡器。

石晶振荡和陶瓷振荡均可采用。

如采用外部时钟源驱动器件,XTAL2应不接。

有余输入至内部时钟信号要通过一个二分频触发器,因此对外部时钟信号的脉宽无任何要求,但必须保证脉冲的高低电平要求的宽度。

图(五)AT89C51引脚图

七、上位机控制的扩展

单片机扩展图如下:

图(六)单片机扩展图

工作原理:

74LS373的输出端Q0~Q7可直接与总线相连。

当三态允许控制端/E为低电平时,Q0~Q7

为正常逻辑状态,可用来驱动负载或总线。

当/E为高电平时,Q0~Q7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端G为高电平时,O随数据D而变。

当G为低电平时,O被锁存在已建立的数据电平。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 485 总线 设计方案 加上 扩展

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《JAVA编程基础》课程标准软件16级.docx

《JAVA编程基础》课程标准软件16级.docx