EDA技术实验教案Word文件下载.docx

EDA技术实验教案Word文件下载.docx

- 文档编号:22228680

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:36

- 大小:94.10KB

EDA技术实验教案Word文件下载.docx

《EDA技术实验教案Word文件下载.docx》由会员分享,可在线阅读,更多相关《EDA技术实验教案Word文件下载.docx(36页珍藏版)》请在冰豆网上搜索。

9

so

二极管D1

PIO8

20

co

二极管D2

PIO9

21

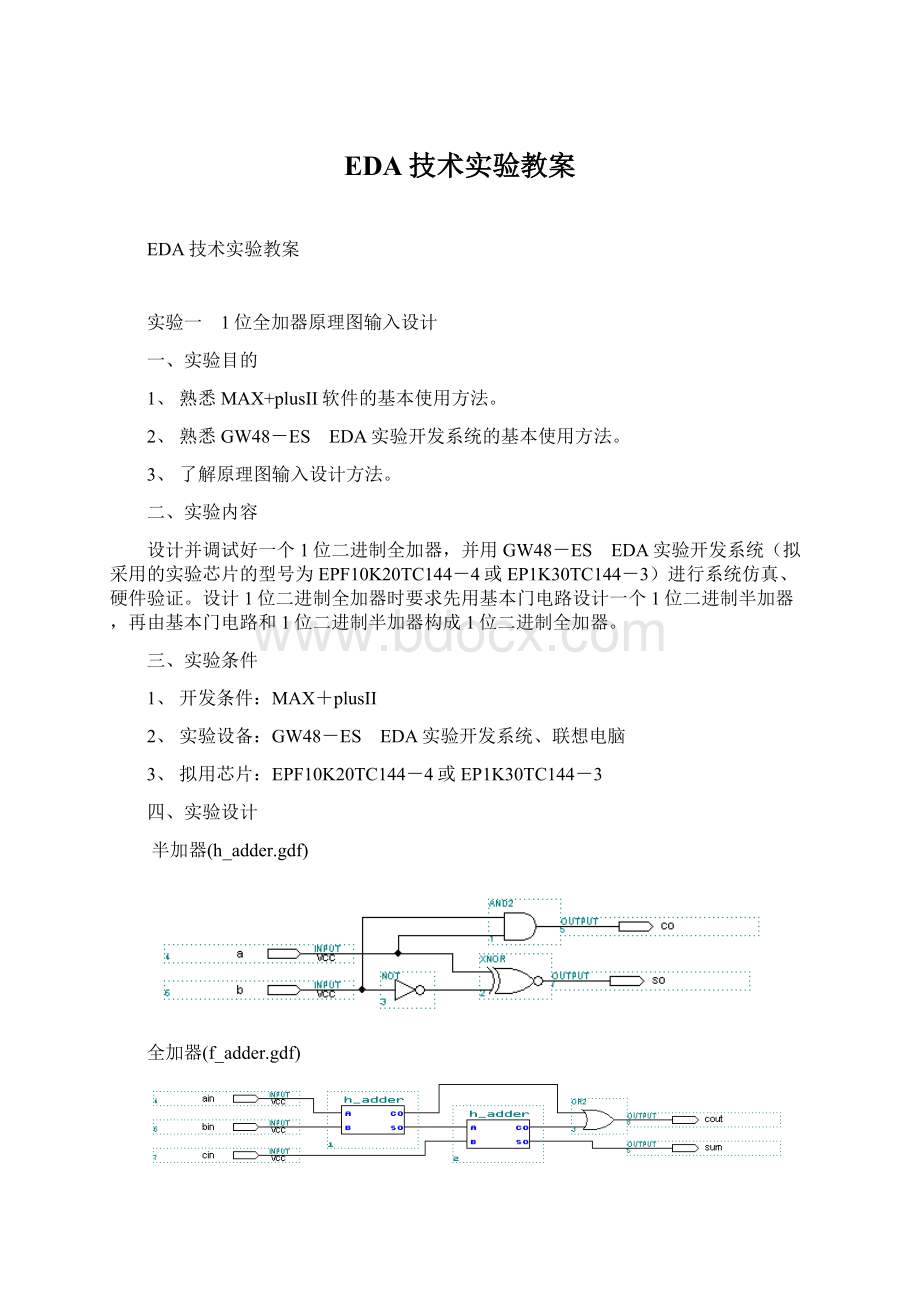

全加器仿真波形

全加器引脚锁定

ain

bin

cin

键3

PIO2

10

sum

cout

全加器真值表

1

实验二 1位全加器VHDL文本输入设计

1、熟悉MAX+plusII软件的基本使用方法。

2、熟悉GW48-ES EDA实验开发系统的基本使用方法。

3、了解VHDL文本输入设计方法。

设计1位二进制全加器时要求先设计一个或门和一个1位二进制半加器,再由或门和1位二进制半加器构成1位二进制全加器。

1、开发条件:

2、实验设备:

3、拟用芯片:

--或门逻辑描述(or2a.vhd)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYor2aIS

PORT(a,b:

INSTD_LOGIC;

c:

OUTSTD_LOGIC);

ENDENTITYor2a;

ARCHITECTUREoneOFor2aIS

BEGIN

c<

=aORb;

ENDARCHITECTUREone;

--半加器描述(h_adder.vhd)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYh_adderIS

INSTD_LOGIC;

co,so:

OUTSTD_LOGIC);

ENDENTITYh_adder;

ARCHITECTUREfh1OFh_adderis

BEGIN

so<

=NOT(aXOR(NOTb));

co<

=aANDb;

ENDARCHITECTUREfh1;

--1位二进制全加器顶层设计描述(f_adder.vhd)

LIBRARYIEEE;

ENTITYf_adderIS

PORT(ain,bin,cin:

Cout,sum:

ENDENTITYf_adder;

ARCHITECTUREfd1OFf_adderIS

COMPONENTh_adder

PORT(a,b:

Co,so:

ENDCOMPONENT;

COMPONENTor2a

ENDCOMPONENT;

SIGNALd,e,f:

STD_LOGIC;

u1:

h_adderPORTMAP(a=>

ain,b=>

bin,

co=>

d,so=>

e);

u2:

e,b=>

cin,

f,so=>

sum);

u3:

or2aPORTMAP(a=>

d,b=>

f,c=>

cout);

ENDARCHITECTUREfd1;

或门仿真波形

半加器仿真波形

全加器仿真波形

实验三 有时钟使能的两位十进制计数器VHDL文本输入设计

3、学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

设计并调试好一个有时钟使能的两位十进制计数器,并用GW48-ES EDA实验开发系统(拟采用的实验芯片的型号为EPF10K20TC144-4或EP1K30TC144-3)进行系统仿真、硬件验证。

设计有时钟使能的两位十进制计数器时要求先设计一个或门和一个十进制计数器,再由十进制计数器构成两位十进制计数器。

--十进制计数器(cnt10.vhd)

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcnt10IS

PORT(clk:

clr:

enb:

outy:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

cout:

ENDcnt10;

ARCHITECTUREbehavOFcnt10IS

BEGIN

PROCESS(clk,clr,enb)

VARIABLEcqi:

STD_LOGIC_VECTOR(3DOWNTO0);

IFclr='

1'

THENcqi:

="

0000"

;

ELSIFCLK'

EVENTANDCLK='

THEN

IFenb='

THEN

IFcqi<

"

1001"

=cqi+1;

ELSEcqi:

ENDIF;

ENDIF;

ENDIF;

outy<

=cqi;

cout<

=cqi(0)AND(NOTcqi

(1))AND(NOTcqi

(2))ANDcqi(3);

ENDPROCESS;

ENDbehav;

--两位十进制计数器(cnt100.vhd)

ENTITYcnt100IS

PORT(clkin:

clrin:

enbin:

outlow:

outhigh:

coutout:

ENDENTITYcnt100;

ARCHITECTUREoneOFcnt100IS

COMPONENTcnt10

PORT(clk:

clr:

enb:

outy:

cout:

SIGNALa:

cnt10PORTMAP(clk=>

clkin,clr=>

clrin,enb=>

enbin,outy=>

outlow,cout=>

a);

a,clr=>

outhigh,cout=>

coutout);

ENDARCHITECTUREone;

十进制计数器仿真波形

两位十进制计数器仿真波形

两位十进制计数器管脚锁定

实验模式:

NO:

5

信号名

芯片管脚序号

enbin

clrin

clkin

CLOCK0

54

coutout

outlow[3..0]

数码管1

PIO16~PIO19

30~33

outhigh[3..0]

数码管2

PIO20~PIO23

36~39

实验五 4位十进制频率计VHDL文本输入设计

--测频控制器(testctl.vhd)

ENTITYTESTCTLIS

PORT(CLKK:

--1Hz

CNT_EN,RST_CNT,LOAD:

ENDTESTCTL;

ARCHITECTUREbehavOFTESTCTLIS

SIGNALDIV2CLK:

PROCESS(CLKK)

IFCLKK'

EVENTANDCLKK='

THENDIV2CLK<

=NOTDIV2CLK;

ENDIF;

PROCESS(CLKK,DIV2CLK)

IFCLKK='

0'

ANDDiv2CLK='

THENRST_CNT<

='

ELSERST_CNT<

LOAD<

=NOTDIV2CLK;

CNT_EN<

=DIV2CLK;

--4位锁存器(reg4b.vhd)

ENTITYREG4BIS

PORT(LOAD:

DIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDREG4B;

ARCHITECTUREbehavOFREG4BIS

PROCESS(LOAD,DIN)

IFLOAD'

EVENTANDLOAD='

THENDOUT<

=DIN;

--时钟到来,锁存数据

--4位十进制频率计(quen4b)

ENTITYquen4bIS

fin:

out1:

out2:

out3:

out4:

coutt:

ENDENTITYquen4b;

ARCHITECTUREoneOFquen4bIS

COMPONENTTESTCTL

COMPONENTREG4B

DIN:

DOUT:

SIGNALa_ena,b_rst,c_load,cout1,cout2,cout3:

SIGNALouty1,outy2,outy3,outy4:

TESTCTLPORTMAP(clkk=>

clkin,CNT_EN=>

a_ena,RST_CNT=>

b_rst,LOAD=>

c_load);

fin,clr=>

b_rst,enb=>

a_ena,outy=>

outy1,cout=>

cout1);

cout1,clr=>

outy2,cout=>

cout2);

u4:

cout2,clr=>

outy3,cout=>

cout3);

u5:

cout3,clr=>

outy4,cout=>

coutt);

u6:

REG4BPORTMAP(LOAD=>

c_load,DIN=>

outy1,DOUT=>

out1);

u7:

outy2,DOUT=>

out2);

u8:

outy3,DOUT=>

out3);

u9:

outy4,DOUT=>

out4);

四位十进制频率计仿真波形(clkin:

1s,fin:

300us)

四位十进制频率管脚锁定

Clock1

55

fin

Clock0

out1

out2

out3

数码管3

PIO24~PIO27

41、42、65、67

out4

数码管4

PIO28~PIO31

68、69、70、72

coutt

实验七 数字秒表VHDL文本输入设计。

实验目的

1、熟悉MAX+plusII的使用。

2、学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

3、熟悉GW48EDA实验开发系统使用。

实验仪器

联想电脑,GW48EDA实验开发系统

设计任务

1、设计一个计时范围为0.01秒~1小时的数字秒表,应具有停表、恢复、清零功能。

实验要求

1、画出系统的原理框图,说明系统中各主要组成部分的功能。

2、编写各个VHDL源程序。

3、根据选用的软件编好用于系统仿真的测试文件。

4、根据选用的软件及EDA实验开发装置编好用于硬件验证的管脚锁定文件。

5、记录系统仿真、硬件验证结果。

6、记录实验过程中出现的问题及解决办法。

实验内容

--3MHz→100Hz分频器(CLKGEN.VHD)

ENTITYCLKGENIS

PORT(CLK:

NEWCLK:

ENDENTITYCLKGEN;

ARCHITECTUREARTOFCLKGENIS

SIGNALCNTER:

INTEGERRANGE0TO10#29999#;

PROCESS(CLK)IS

IFCLK'

EVENTANDCLK='

THEN

IFCNTER=10#29999#THENCNTER<

=0;

ELSECNTER<

=CNTER+1;

PROCESS(CNTER)IS

IFCNTER=10#29999#THENNEWCLK<

='

ELSENEWCLK<

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 技术 实验 教案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx