8位串行进位加法器Word文件下载.docx

8位串行进位加法器Word文件下载.docx

- 文档编号:22222588

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:10

- 大小:1.82MB

8位串行进位加法器Word文件下载.docx

《8位串行进位加法器Word文件下载.docx》由会员分享,可在线阅读,更多相关《8位串行进位加法器Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

用半加器设计一个全加器元件,然后根据图4-38,在顶层设计中用8个1位全加器构成8位串行进位加法器。

给出时序仿真波形并说明之、引脚锁定编译、编程下载于FPGA中进展硬件测试。

完成实践报告。

三、实验步骤与各步结果

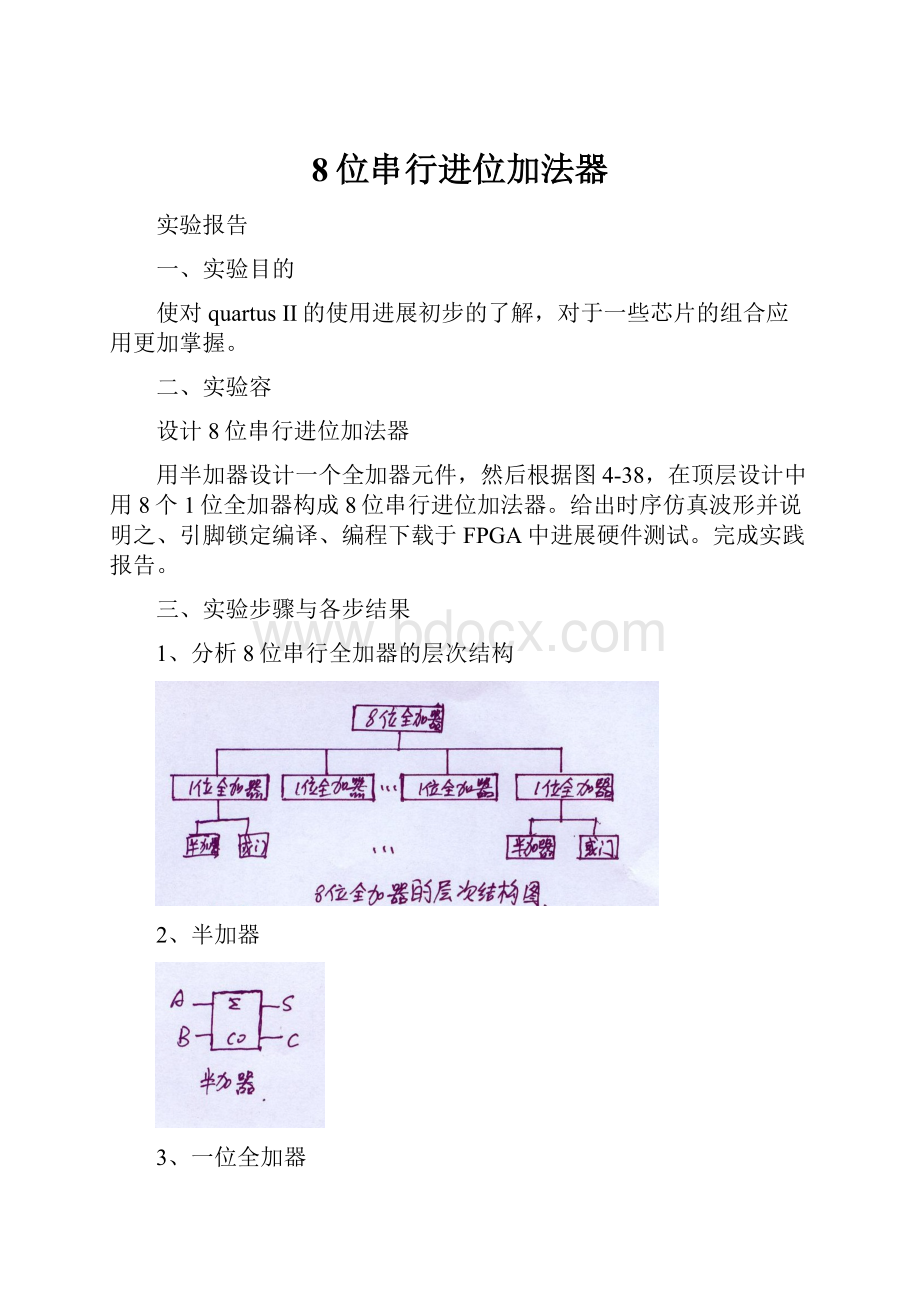

1、分析8位串行全加器的层次结构

2、半加器

3、一位全加器

4、8位全加器

//8-bitadder

//halfadder

modulehalfadder(S,C,A,B);

inputA,B;

outputS,C;

xor(S,A,B);

and(C,A,B);

endmodule

//1-bitfulladder

modulefulladder(S,CO,A,B,CI);

inputA,B,CI;

outputS,CO;

wireS1,D1,D2;

halfadderHA1(S1,D1,A,B);

halfadderHA2(S,D2,S1,CI);

org1(CO,D2,D1);

//8-bitfulladder

module_8bit_adder(S,C7,A,B,C_1);

input[7:

0]A,B;

inputC_1;

output[7:

0]S;

outputC7;

wireC0,C1,C2,C3,C4,C5,C6,C7;

fulladderFA0(S[0],C0,A[0],B[0],C_1),

FA1(S[1],C1,A[1],B[1],C0),

FA2(S[2],C2,A[2],B[2],C1),

FA3(S[3],C3,A[3],B[3],C2),

FA4(S[4],C4,A[4],B[4],C3),

FA5(S[5],C5,A[5],B[5],C4),

FA6(S[6],C6,A[6],B[6],C5),

FA7(S[7],C7,A[7],B[7],C6);

5、软件使用

〔1〕、新建一个工程,工程名为_8bit_adder

(2)、新建一个VerilogHDLFile文件并写入程序代码

〔3〕、对写完的代码进展编译,发现没有错误

〔4〕、新建一个波形文件

〔5〕、新建

〔6〕、插入程序后双击输入数值进展数据的输入

〔7〕、输入相应的值

〔8〕、仿真出来的结果

〔9〕、按时序给输入端输入不同的数据

〔10〕、继续仿真,波形如图

〔11〕、时序仿真

〔12〕、放大后

这里出现了冒险竞争。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 串行 进位 加法器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx