ANST微控制器振荡器电路设计指南文档格式.docx

ANST微控制器振荡器电路设计指南文档格式.docx

- 文档编号:22220920

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:15

- 大小:203.21KB

ANST微控制器振荡器电路设计指南文档格式.docx

《ANST微控制器振荡器电路设计指南文档格式.docx》由会员分享,可在线阅读,更多相关《ANST微控制器振荡器电路设计指南文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

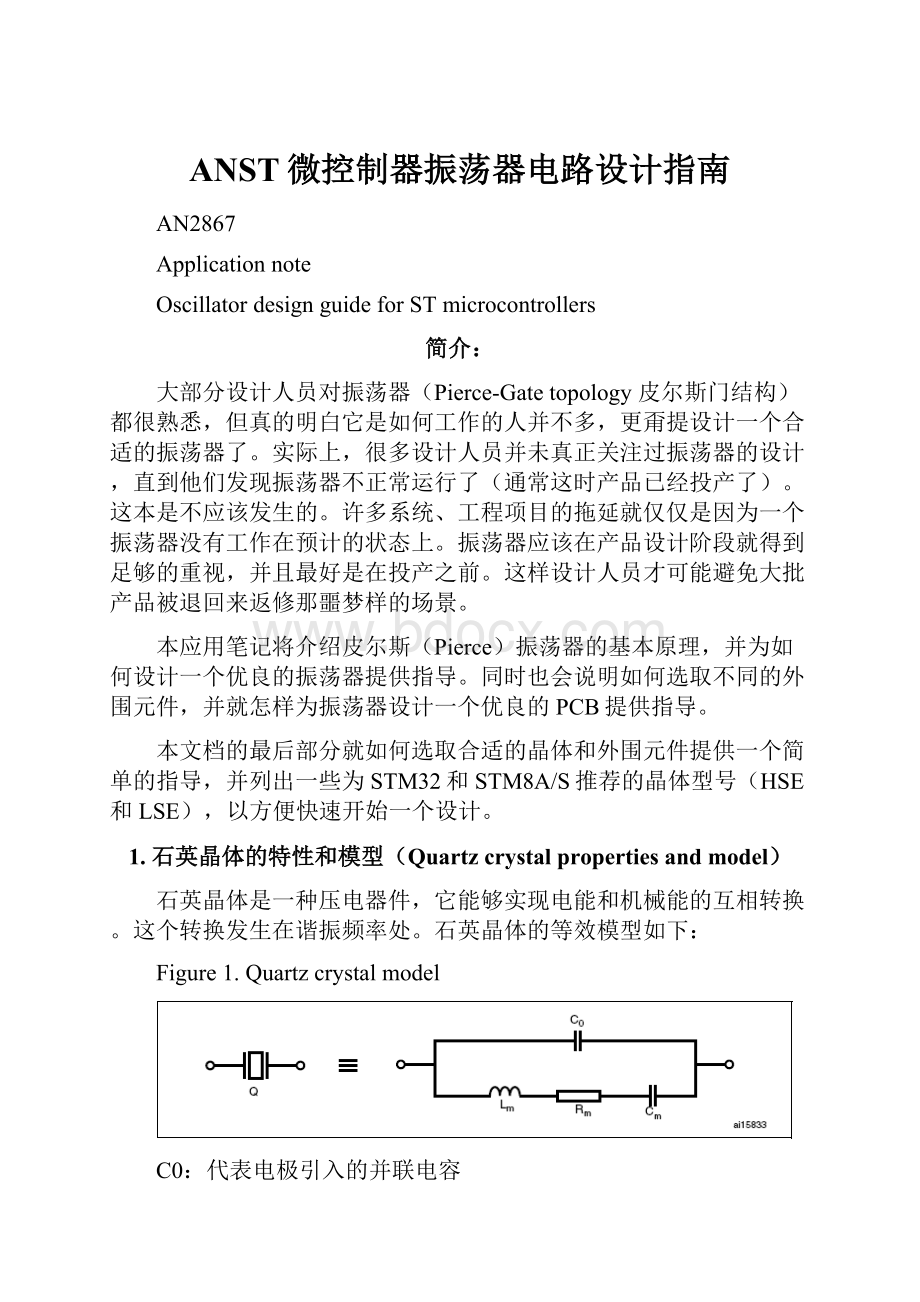

(假设Rm是可以忽略的)

图2是晶体在频域内的阻抗曲线。

Figure2.Impedancerepresentationinthefrequencydomain

Fs是晶体在Z=0时的串联谐振频率。

它的表达式可以从等式

(1)中推导出来:

Fa是反谐振频率,此时的Z趋于无穷大。

从等式

(1)中可以推导出它的表达式为:

由Fs和Fa界定的区域被称作为并联谐振区域(图2中的阴影部分)。

在这段区域内,晶体工作在并联谐振状态下,其表现像一个电感,会在环路中增加180度的相移。

它的频率Fp(或FL:

负载频率)的表达式如下:

从等式4中可以看出,晶体的振荡频率能够通过使用不同的负载电容CL进行调校。

这也就是为什么晶体制造商会在他们的晶体数据手册内指明晶体振荡在标定的频率上时所需要的精确的负载电容CL值。

表1给出了一个标定为8MHz的晶体,其等效电路元件值的例子。

表1等效电路的参数的例子

通过等式

(2)、(3)、(4)我们可以算出这个晶体的Fs,Fa,Fp:

Fs=7988768Hz,Fa=8008102Hz

如果该晶体电极上的负载电容CL等于10pF,则该晶体将振荡在如下的频率上:

Fp=7995695Hz

如果要精确的得到8MHz的振荡频率,则CL应等于4.02pF。

2.振荡器理论

一个振荡器包含一个放大器和一个提供选频的反馈网络。

图3是这个基本原理的框图:

图3振荡器原理

●A(f)是放大器的复转移函数(complextransferfunction),为保持振荡器的振荡提供能量。

●B(f)是反馈的复转移函数(complextransferfunction),用来设置振荡器的频率。

为了能够振荡,必须要满足以下Barkhausen条件:

闭环增益大于1;

总相移为360度。

即:

启动振荡器需要有一个初始的电能量。

上电的瞬间以及噪声都可以提供这种能量。

但是,这个能量必须足够大到可以触发振荡器振荡在设计的频率上。

数学表达式为:

这个表达式意味着开环增益必须远大于1。

振荡器达到稳定所需要的时间就取决于这个开环增益。

满足了振荡条件并不足以解释晶体振荡器为什么可以起振。

实际上,之所以能够起振,是因为在满足了振荡条件后,那个放大器是非常不稳定的,从正反馈网络中引入的任何一点干扰都会导致放大器的失稳并导致起振。

这个干扰可以归因于一个上电,一个使能电平的跳变,或者是晶体的热噪声,等等。

另外值得注意的是,只有落在串-并频率范围内的噪声能够被放大(译注:

“串-并频率范围”是指图2中Fa到Fs之间的频率)。

这表示能够触发振荡的频率范围是很小的,这也就解释了为什么晶体振荡器需要如此长的时间才能启动。

3.皮尔斯振荡器(Pierceoscillator)

皮尔斯振荡器(Pierceoscillator)在各种应用中使用的非常普遍,因为它功耗低,成本低,并且稳定性好。

图4皮尔斯振荡器(Pierceoscillator)电路

Inv:

内部的反向器,作为放大器来工作。

Q:

石英晶体或者陶瓷谐振器。

RF:

内部反馈电阻。

RExt:

外部电阻,用于限制反向器的输出电流。

CL1和CL2:

两个外部负载电容。

Cs:

MCU引脚(OSC_IN和OSC_OUT)间和PCB线路上的杂散电容,它是一个并联电容。

4.皮尔斯振荡器的设计(Pierceoscillatordesign)

本章讲解各种限定因素,以及如何为它们取值,进一步熟悉皮尔斯振荡器(Pierceoscillator)的设计。

4.1反馈电阻RF(FeedbackresistorRF)

在大多数的ST微控制器中,RF是嵌入在振荡器电路内部的,它的作用是使反向器作为放大器工作。

该反馈电阻被并接在Vin和Vout上,这样就使放大器的Vout=Vin,从而强制它运行在线性区内(图5中的阴影区域)。

放大器会把处于串-并频率范围(Fa,Fs)(译注:

原文为(Fa,Fa),应是有误)内的噪声放大(例如,晶体的热噪声)。

这个噪声会引发振荡器起振。

在某些情况下,当振荡器的振荡稳定后将RF移走,振荡器仍可以继续正常的运行。

图5反向器的转移函数

表2是RF的典型值。

表2在给定的频率下的典型RF值

4.2负载电容CL(LoadcapacitorCL)

负载电容是指与晶体振荡器相连的电路中的所有电容。

它的值取决于外接电容CL1、CL2,以及PCB和连接点上的杂散电容(Cs)。

负载电容CL由晶体制造商指定。

值得注意的是,若要得到精确的频率,振荡器电路的负载电容必须与所需要的值相等;

若要频率保持稳定,则负载电容必须稳定。

外接电容CL1和CL2就是为了把负载电容调校为制造商所指定的CL值。

下面的等式给出了负载电容CL的表达式:

下面举一个例子说明外接电容CL1、CL2的值的计算:

假设某晶体的负载电容CL值为15pF,且Cs=5pF,则:

4.3振荡器的增益裕量(Gainmarginoftheoscillator)

增益裕量是一个关键参数,它决定着振荡器是否能够起振。

它的表达式是:

其中,

●gm是反向器的跨导(在高频模块中的单位是mA/V,在32KHz低频模块中的单位是μA/V)

●gmcrit(gm的临界值),取决于晶体的参数。

假设CL1=CL2,并且晶体上的负载电容与制造商的给定值完全一样,则gmcrit可用下式来表示:

,式中ESR的意思是等效串联电阻(equivalentseriesresistor)

根据EricVittoz理论:

晶体动态的等效RLC电路的阻抗由放大器和两个外接电容的阻抗作补偿。

由此理论,反向器的跨导(gm)的值必须满足gm>

gmcrit,这是振荡器能够正常运行的必要条件。

通常认为,增益裕量值为5是保证振荡器有效起振的最小值。

举个例子,为某微控制器中gm值为25mA/V的振荡器做设计时,我们选择了具有以下特性的石英晶体:

frequency=8MHz,C0=7pF,CL=10pF,ESR=80,问此晶体是否可以用于此微控制器?

我们首先计算一下gmcrit,

然后计算gainmargin,

可见,gainmargin值远大于5,满足起振条件,能够起动振荡器。

晶体能够正常振荡。

如果计算后发现gainmargin值不合适(增益裕量gainmargin值小于5),则达不到振荡条件,晶体将不能振荡。

这时你只能再选择一个有更低ESR和/或有更低CL值的晶体了。

4.4驱动功率和外接电阻的计算(DrivelevelDLandexternalresistorRExtcalculation)

驱动功率与外接电阻紧密相关,因此在本章中将两者一并讨论。

4.4.1计算驱动功率(CalculatingdrivelevelDL)

驱动功率就是指晶体内消耗的功率。

它必须被限制在一定范围内,否则晶体会因过度的机械振动而损坏。

最大驱动功率由晶体制造商指定,单位通常用mW。

超过指定的驱动功率,可能会导致晶体损坏。

驱动功率可以用这个表达式来表示:

●ESR是等效串联电阻(由制造商指定)。

●IQ是流过晶体的电流的有效值(均方根)。

流过晶体的电流可以通过示波器观测到,它是一个正弦曲线。

电流值可以通过测量峰-峰值(IPP)读出。

如果使用电流探针(如图6所示),示波器上电压网格的尺度就可以转换为1mA/1mV。

图6使用电流探针测量驱动电流

由前面所述的可知,在用电位计调节流过晶体的电流时,电流值不可以超过IQmax的有效值(均方根)(假设流过晶体的电流是完全正弦的)。

由此,可以反推出IQmax:

(译注:

IQmaxPP为正弦波的峰-峰值,为求有效值IQmax,需先将峰-峰值除以2,再除以

。

交流电有效值的推导过程:

原理是总功耗相等,即

,假设电阻R=1Ω,单位正弦电压峰值为1V,对正弦电压求平方,再求其周期

内的积分得

,得到

。

)

流过晶体的电流值(从示波器上读到的峰-峰值)不可以超过最大峰-峰值电流IQmaxPP,由上式可以得到其最大值为:

因此,当实际电流IQ超过了IQmaxPP时,需要加上一个外接电阻RExt(参考4.4.3节)。

这时该电阻是电路中不可缺少的一部分,相应地,在计算IQmax的表达式中会增大那个ESR的值。

4.4.2另一种测量驱动功率的方法(Anotherdrivelevelmeasurementmethod)

驱动功率可以按下式计算:

其中,IQRMS是交流电流的有效值(均方根)。

电流值可以通过使用一个低电容值(不大于1pF)的示波器探针测量放大器输入端的电压波形计算得出。

因为相对于CL1而言,流入放大器的电流稍不足道,所以我们可以假设流过晶体的电流等于流过CL1的电流。

因此,这一点上的电压有效值(均方根)与电流有效值(均方根)的关系为:

电容阻抗z=1/(2*pi*F*C);

所以电流I=V/z可推出上式。

)

●F为晶振的频率

●

其中,Vpp是CL1上的电压峰峰值

●Ctot=CL1+(Cs/2)+Cprobe,其中:

–CL1是放大器输入端的外接负载电容

–Cs是杂散电容

–Cprobe是探针电容

因此可以按下式计算驱动功率DL:

该DL值必须小于晶体制造商指定的驱动功率值。

4.4.3计算外接电阻RExt(CalculatingexternalresistorRExt)

这个电阻的作用是限制晶体的驱动功率。

它和CL2一起构成了一个低通滤波器,强制振荡器工作在基波频率上,而不是其他高次谐波(防止振荡器振荡在3,5,7倍的基波频率上)。

如果晶体上的功率耗散大于制造商的指定值,则外接电阻RExt是必须的,以避免晶体被过驱动;

如果晶体上的功率耗散小于制造商的指定值,则不建议加入外接电阻RExt,或者它的值为0Ω。

可以通过计算由RExt/CL2构成的分压来估算外接电阻RExt的初始值。

即令RExt等于CL2的容抗。

如下:

例如,假设:

●振荡频率F=8MHz

●CL2=15pF

则可以算出RExt的值为1326Ω。

推荐使用下面的方法优化外接电阻RExt:

先以之前介绍的方法选择CL1和CL2,然后在RExt的位置初始放置一个值等于CL2的容抗的分压电阻。

然后不断微调这个分压电阻的值,直到得到符合要求的输出和驱动功率。

注意:

在计算完RExt的值以后,建议重新计算增益裕量(参考4.3节,振荡器的增益裕量)以确保增加的电阻不会影响振荡器的起振条件。

也就是说,gmcrit表达式中的ESR还要加上RExt,并且依然要满足gm>

>

gmcrit的条件:

注:

如果RExt太低,晶振上就没有功率耗散;

如果如果RExt太高,就不会产生振荡,因为不满足起振条件。

(原文:

IfRExtistoolow,thereisnopowerdissipationinthecrystal.IfRExtistoohigh,thereisnooscillation:

theoscillationconditionisnotreached.

译注:

这句话想表达的意思没弄明白。

貌似是原文档写错/反了吧。

推测它想表达的实际意思应该是Rext阻值越大越好,可有效防止晶振被过驱动,但太大会导致Gmargin过小,不能起振。

4.5启动时间(Startuptime)

这是振荡器从开始起振到振荡稳定的时间。

石英谐振器的启动时间要比陶瓷谐振器的长。

启动时间取决于:

外接电容CL1和CL2;

晶体的振荡频率,频率越高启动时间越短;

所选用的晶体类型,相比较而言,石英谐振器的启动时间远长于陶瓷谐振器。

启动问题通常可归因于增益裕量(如前面所述的那样),与之相关的是CL1和CL2过小或过大,或者是ESR太大了。

一个MHz级的晶体,启动时间一般是ms级。

32kHz晶体的启动时间一般在1-5s范围内。

4.6晶体牵引度(pullability)

晶体牵引度(Pullability)是指在通常的并联谐振应用中晶体频率的改变。

它也是对晶体在负载电容按指定规律变化时所对应的频率变化的一个测量。

负载电容减小会导致频率增大;

相反的,负载电容增大会导致频率减小。

晶体牵引度(Pullability)可用下式表示:

5.轻松选择合适晶体和外围器件的指导(Easyguidelinefortheselectionofsuitablecrystalandexternalcomponents)

本章给出了选择合适晶体和外围器件的推荐流程。

整个流程可分解为三个步骤:

步骤一:

计算增益裕量。

(请参考4.3节:

振荡器的增益裕量)

●选择一个晶体,然后找到控制器的参考手册(选择晶体+微控制器数据手册)

●计算微控制器中振荡器的增益裕量,查看它是否比5大:

如果增益裕量小于5,该晶体不合适,再选择其他具有较低ESR或/和有较低CL的晶体,然后重复步骤一。

如果增益裕量大于5,进入步骤二。

步骤二:

计算外接负载电容。

(请参考4.2节:

负载电容CL)

计算CL1和CL2,查看是否能够在市场上买到它们:

●如果你能买到与你的计算值完全一样的电容,振荡器就会工作在预期的频率上,你可以进入步骤三了。

●如果你没有买到那个值的电容,并且:

–频率精度对你而言非常关键,你可以使用一个可调电容以获得精确的值。

然后你可以进入步骤三了。

–你对频率精度的要求并不严格,就选择一个在市场上能买到的值最接近的电容,然后进入步骤三。

步骤三:

计算驱动功率和外接电阻。

(请参考4.4节:

驱动功率和外接电阻的计算)

●计算DL,然后比较它与DLcrystal谁大谁小:

–如果DL<

DLcrystal,不需要增加外接电阻。

恭喜你选到了一个合适的晶体!

–如果DL>

DLcrystal,你应该再计算RExt以满足DL<

DLcrystal。

然后你还需要把RExt代到增益裕量的计算公式中重新计算增益裕量。

如果增益裕量>

5,恭喜你,你找到了一个合适的晶体!

如果增益裕量太小,这个晶体将不能正常工作,你只能再重新选择一个晶体了。

回到步骤一,选择一个新的晶体吧。

6.推荐一些适合STM32MCU用的晶体

(略)

7.推荐一些适合STM8MCU用的晶体

8.一些PCB的提示(SomePCBhints)

1.必须避免引入过多的杂散电容和电感,因为它们可能会使振荡器进入到非预期的状态,并产生启动问题。

高频信号尽量不要靠近振荡器电路。

2.尽可能地缩短布线长度。

3.使用地平面隔离信号,减少噪声。

例如在最靠近晶振保护环路(译注:

指器件或走线外围成一圈用于屏蔽干扰的导线环,一般要求理论上没有电流从该导线环上经过)的另一个板层上铺设一层本地地平面,可有效防止晶振与其他PCB板层产生不希望的耦合(串扰)。

应当注意的是,这个本地地平面只是在晶振附近铺设,而不是在整个板子都铺设。

见图7。

4.VSS路径也可以像图7那样布置。

在这种方法中,VSS路径将振荡器的输入与输出隔离开,同时也把振荡器与邻近的其他电路隔离开。

VSS路径中间不能被打断,两端分别终止于CL2、CL2下面,并不连接到晶振下面的那块地保护上。

图7中所有VSS的过孔/焊盘都和在另一层上的本地地平面相连(即图7中除了晶振的焊盘)。

5.在每个VDD和离它最近的VSS上使用去耦电容,以减小噪声干扰。

图7推荐的振荡电路PCB布线

警告:

强烈建议在图7中所示的PCB区域使用保护涂料,尤其是在LSE晶体,CL1,CL2,和OSC_IN、OSC_OUT线路上,以防止水雾,灰尘,湿气和极端温度导致启动问题。

RExt只有当晶体的功率耗散比制造商规定的驱动功率大的时候才是必须的,否则其值应当为0(详细内容参考4.4驱动功率和外接电阻的计算)

9.结论(Conclusion)

最重要的参数是振荡器的增益裕量,它决定了振荡器是否能够起振。

这个参数必须在晶体的选型阶段被计算。

第二个重要的参数是外接负载电容,它的选择必须与晶体所规定的CL相一致(该CL值由晶体制造商提供)。

外接负载电容决定着晶体的频率精度。

第三个重要的参数是用于限制驱动功率的外接电阻的值。

但是,在32kHz振荡器模块中,不推荐使用外接电阻。

因为有太多的变量被涉及,所以在实验阶段所使用的元件应该与将来在产品上所使用的元件有完全相同的特性。

例如,你应当在相同的环境条件下使用同样的振荡器布线来工作,以避免无法预料的情况,并因此节省时间。

10.版本历史(Revisionhistory)

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ANST 控制器 振荡器 电路设计 指南

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

素描基础课ppt课件PPT课件下载推荐.ppt

素描基础课ppt课件PPT课件下载推荐.ppt

培训体系搭建工作完成时间计划表表格推荐下载.xlsx

培训体系搭建工作完成时间计划表表格推荐下载.xlsx