CMOS全加器课程设计Word格式文档下载.docx

CMOS全加器课程设计Word格式文档下载.docx

- 文档编号:22198105

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:14

- 大小:180.25KB

CMOS全加器课程设计Word格式文档下载.docx

《CMOS全加器课程设计Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《CMOS全加器课程设计Word格式文档下载.docx(14页珍藏版)》请在冰豆网上搜索。

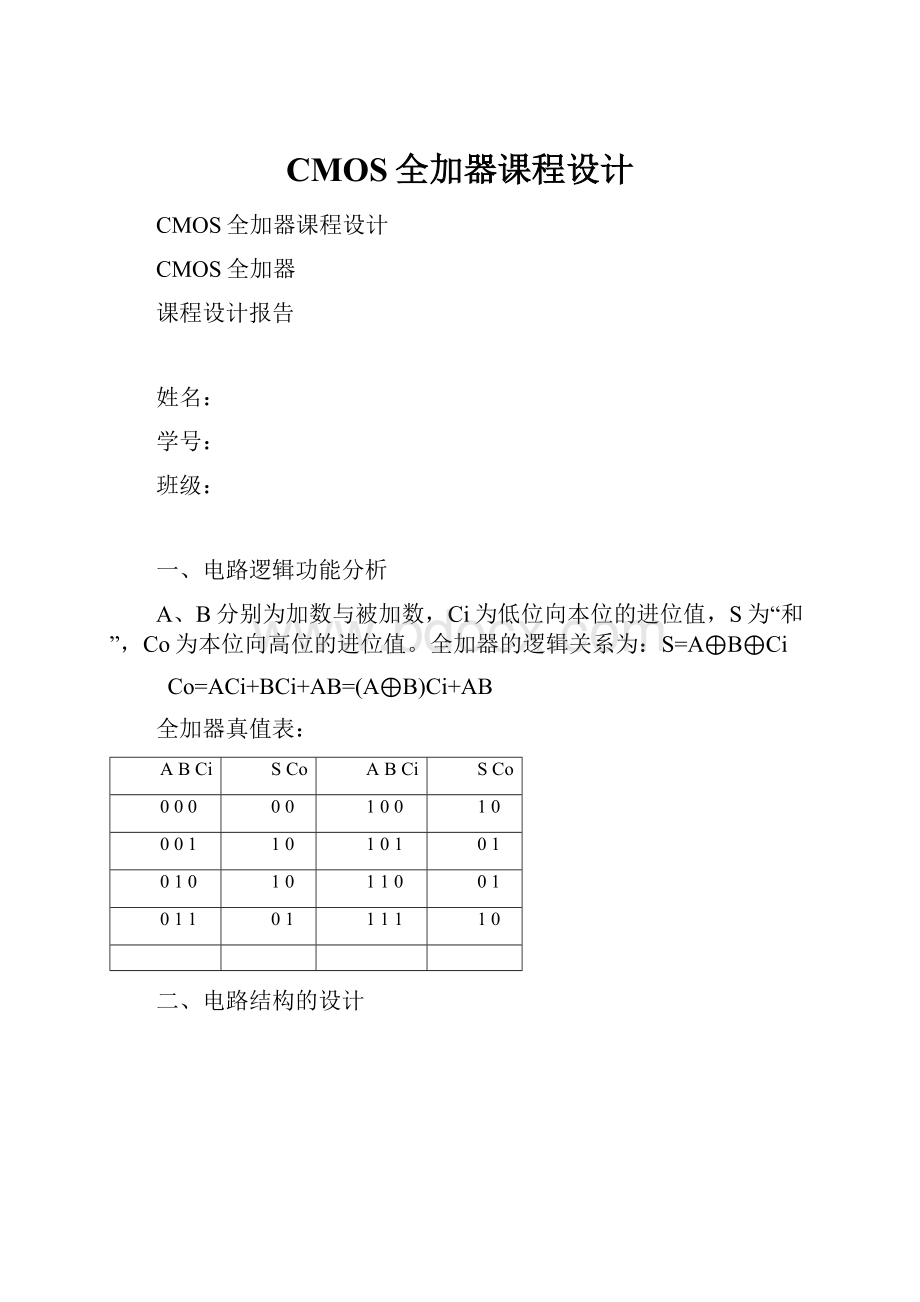

010

110

011

111

二、电路结构的设计

该电路传输门1与反相器构成异或门,传输门2与反相器构成同或门,其输出分别为A⊕B、

。

同或门与异或门的关系为:

只要将异或门的输出端反相,如A变成

,那么异或门就变成了同或门,反之亦然。

该电路实现全加器的原理为:

因为

S=A⊕B⊕Ci=(A⊕B)

+(

)Ci

当

=0,A⊕B=1时,S=

=1,A⊕B=0时,S=Ci

因此,求和只需用一个2选1数据选择器,用A⊕B和

作为控制信号,用Ci与

作为输入信号即可。

图中传输门3和4组成2选1数据选择器。

进位信号:

Co=(A⊕B)Ci+AB

当A⊕B=0,则A=B=1Co=1=A=B,A=B=0Co=0=A=B,即Co选择A或B。

当A⊕B=1,则A

B,Co=Ci,即Co选择Ci。

因此,同样用一个2选1电路,用A⊕B和

作为控制信号,Co在A和Ci选择。

图中传输门5和6构成2选1电路,完成进位信号输出功能。

输出端反相器一方面可以增加驱动能力,另一方面可以完成反相还原极性,因为数据选择器输入信号是

和

三、全加器线路图:

四、全加器网表:

fulladder.sp文件:

*SPICEnetlistwrittenbyS-EditWin322.06

*WrittenonJun12,2011at23:

16:

01

*Waveformprobingcommands

.probe

.optionsprobefilename="

Module0.dat"

+probesdbfile="

H:

\fulladder\fulladder.sdb"

+probetopmodule="

Module0"

.include"

\fulladder\ml2_125.md"

VPowerVddGnd5

vaAGndPULSE(0550n5n5n50n100n)

vbBGndBIT({0011}lt=50nht=50non=5off=0rt=5nft=5n)

vciCiGndPWL(0ns0V200ns0V205ns5V400ns5V)

.tran1n400n

.printtranv(A)v(B)v(Ci)v(S)v(Co)

*Maincircuit:

Module0

M1N13AGndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M2N14N12GndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M3N10N13BGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M4N12ABGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M5N6CiGndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M6N2N1GndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M7CoN5GndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M8N12BAGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M9N10BN13GndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M10N6N10N1GndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M11CiN12N1GndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M12N13N12N5GndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M13N6N10N5GndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M14SN2GndGndNMOSL=2uW=5uAD=66pPD=24uAS=66pPS=24u

M15N13AVddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M16N14N12VddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M17N10ABVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M18N12N13BVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M19N6CiVddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M20N2N1VddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M21CoN5VddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M22N12BN13VddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M23N10BAVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M24N6N14N1VddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M25CiN10N1VddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M26N13N12N5VddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M27N6N12N5VddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

M28SN2VddVddPMOSL=2uW=9uAD=66pPD=24uAS=66pPS=24u

*Endofmaincircuit:

fulladder.spc文件:

*CircuitExtractedbyTannerResearch'

sL-EditV7.12/ExtractV4.00;

*TDBFile:

H:

\fulladder\fulladder,Cell:

Cell0

*ExtractDefinitionFile:

C:

\ProgramFiles\TannerEDA\L-Edit\spr\morbn20.ext

*ExtractDateandTime:

06/12/2011-22:

58

VPowerVDDGND5

vaAGNDPULSE(0550n5n5n50n100n)

vbBGNDBIT({0011}lt=50nht=50non=5off=0rt=5nft=5n)

vciCiGNDPWL(0ns0V200ns0V205ns5V400ns5V)

*WARNING:

LayerswithUnassignedAREACapacitance.

*<

PolyResistor>

Poly2Resistor>

NDiffResistor>

PDiffResistor>

NWellResistor>

PBaseResistor>

LayerswithUnassignedFRINGECapacitance.

PadComment>

Poly1-Poly2Capacitor>

LayerswithZeroResistance.

NMOSCapacitor>

PMOSCapacitor>

*NODENAMEALIASES

*1=VDD(33,36)

*2=VDD(186,-80)

*5=Co(186,-4.5)

*6=S(163,3.5)

*8=VDD(29,-80.5)

*9=VDD(107.5,-27)

*10=VDD(80,-77.5)

*11=Ci(52.5,5.5)

*12=B(100.5,-63.5)

*15=A(30.5,6.5)

*18=GND(27,-22)

M1Co3VDDVDDPMOSL=2uW=9uAD=49.5pPD=29uAS=247.5pPS=145u

*M1DRAINGATESOURCEBULK(1831818527)

M2S4VDDVDDPMOSL=2uW=9uAD=49.5pPD=29uAS=247.5pPS=145u

*M2DRAINGATESOURCEBULK(1601816227)

M3416VDDVDDPMOSL=2uW=9uAD=49.5pPD=29uAS=247.5pPS=145u

*M3DRAINGATESOURCEBULK(1371813927)

M413AVDDVDDPMOSL=2uW=9uAD=148.5pPD=87uAS=247.5pPS=145u

*M4DRAINGATESOURCEBULK(40184227)

M51619CiVDDPMOSL=2uW=9uAD=99pPD=58uAS=49.5pPS=29u

*M5DRAINGATESOURCEBULK(1141811627)

M614CiVDDVDDPMOSL=2uW=9uAD=148.5pPD=87uAS=247.5pPS=145u

*M6DRAINGATESOURCEBULK(62.51864.527)

M7161714VDDPMOSL=2uW=9uAD=99pPD=58uAS=148.5pPS=87u

*M7DRAINGATESOURCEBULK(91.51893.527)

M832013VDDPMOSL=2uW=9uAD=99pPD=58uAS=148.5pPS=87u

*M8DRAINGATESOURCEBULK(143.5-45145.5-36)

M932014VDDPMOSL=2uW=9uAD=99pPD=58uAS=148.5pPS=87u

*M9DRAINGATESOURCEBULK(166-45168-36)

M101720VDDVDDPMOSL=2uW=9uAD=49.5pPD=29uAS=49.5pPS=29u

*M10DRAINGATESOURCEBULK(189.5-75191.5-66)

M1132013GNDNMOSL=2uW=5uAD=55pPD=42uAS=82.5pPS=63u

*M11DRAINGATESOURCEBULK(143.5-83.5145.5-78.5)

M121720GNDGNDNMOSL=2uW=5uAD=27.5pPD=21uAS=165pPS=126u

*M12DRAINGATESOURCEBULK(189.5-36191.5-31)

M1331914GNDNMOSL=2uW=5uAD=55pPD=42uAS=82.5pPS=63u

*M13DRAINGATESOURCEBULK(166-83.5168-78.5)

M14Co3GNDGNDNMOSL=2uW=5uAD=27.5pPD=21uAS=165pPS=126u

*M14DRAINGATESOURCEBULK(183-18185-13)

M15S4GNDGNDNMOSL=2uW=5uAD=27.5pPD=21uAS=165pPS=126u

*M15DRAINGATESOURCEBULK(160-18162-13)

M16416GNDGNDNMOSL=2uW=5uAD=27.5pPD=21uAS=165pPS=126u

*M16DRAINGATESOURCEBULK(137-18139-13)

M17B1320VDDPMOSL=2uW=9uAD=99pPD=58uAS=99pPS=58u

*M17DRAINGATESOURCEBULK(114.5-45116.5-36)

M18BA19VDDPMOSL=2uW=9uAD=99pPD=58uAS=99pPS=58u

*M18DRAINGATESOURCEBULK(88.5-73.590.5-64.5)

M1920B13VDDPMOSL=2uW=9uAD=99pPD=58uAS=148.5pPS=87u

*M19DRAINGATESOURCEBULK(63.5-4065.5-31)

M2019BAVDDPMOSL=2uW=9uAD=99pPD=58uAS=49.5pPS=29u

*M20DRAINGATESOURCEBULK(40-76.542-67.5)

M21B1319GNDNMOSL=2uW=5uAD=55pPD=42uAS=55pPS=42u

*M21DRAINGATESOURCEBULK(88.5-3090.5-25)

M22BA20GNDNMOSL=2uW=5uAD=55pPD=42uAS=55pPS=42u

*M22DRAINGATESOURCEBULK(114.5-83.5116.5-78.5)

M2313AGNDGNDNMOSL=2uW=5uAD=82.5pPD=63uAS=165pPS=126u

*M23DRAINGATESOURCEBULK(40-1842-13)

M241620CiGNDNMOSL=2uW=5uAD=55pPD=42uAS=27.5pPS=21u

*M24DRAINGATESOURCEBULK(114-18116-13)

M2514CiGNDGNDNMOSL=2uW=5uAD=82.5pPD=63uAS=165pPS=126u

*M25DRAINGATESOURCEBULK(62.5-1464.5-9)

M2620BAGNDNMOSL=2uW=5uAD=55pPD=42uAS=27.5pPS=21u

*M26DRAINGATESOURCEBULK(63.5-7965.5-74)

M2719B13GNDNMOSL=2uW=5uAD=55pPD=42uAS=82.5pPS=63u

*M27DRAINGATESOURCEBULK(40-3642-31)

M28161914GNDNMOSL=2uW=5uAD=55pPD=42uAS=82.5pPS=63u

*M28DRAINGATESOURCEBULK(91.5-1893.5-13)

*TotalNodes:

20

*TotalElements:

28

*ExtractElapsedTime:

0seconds

.END

五、全加器波形图:

六、全加器版图:

七、全加器LVS对比结果:

八、课程设计体会

通过此次课程设计,使我更加扎实的掌握了有关全加器线路方面的知识,也更了解异或门、同或门和数据选择器方面和版图设计方面的知识,在设计过程中查到的资料虽然有点小错误,还遇到了其他一些问题,例如仿真、版图,但经过大家一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。

实践出真知,通过亲自动手制作,使我掌握的知识不再是纸上谈兵。

过而能改,善莫大焉。

在课程设计过程中,我不断发现错误,不断改正,不断领悟,不断获取。

在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜

悦,也永远不可能得到社会及他人对你的认可!

通过课程设计给了我很多专业知识以及专业技能上的提升,给了我很多思。

同时,设计让我感触很深。

使我对抽象的理论有了具体的认识。

看到成果,那种喜悦无法形容,收获颇丰。

九、参考文献

1.《专用集成电路设计基础》孙肖子等编著,西安电子科技大学出版社,2003

2.《TannerPro集成电路设计与布局实践指导》廖裕评陆瑞强编著,科学出版社,2007

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CMOS 全加器 课程设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx