FPGA教学实验板说明书.docx

FPGA教学实验板说明书.docx

- 文档编号:2207661

- 上传时间:2022-10-27

- 格式:DOCX

- 页数:18

- 大小:220.56KB

FPGA教学实验板说明书.docx

《FPGA教学实验板说明书.docx》由会员分享,可在线阅读,更多相关《FPGA教学实验板说明书.docx(18页珍藏版)》请在冰豆网上搜索。

FPGA教学实验板说明书

FPGA教学实验板说明书

西安邮电学院计算机系

电子科学信息与技术实验室

2009-10-29

FPGA教学实验板说明书

Altera公司FLEX10K系列FPGA芯片,具有高密度,低成本,低功耗的特点,属于查找表型逻辑单元结构,其不仅具有实现普通逻辑功能的逻辑阵列,而且具有实现“宏函数”的嵌入式阵列,因而可以实现高效存储器和特殊的逻辑功能.

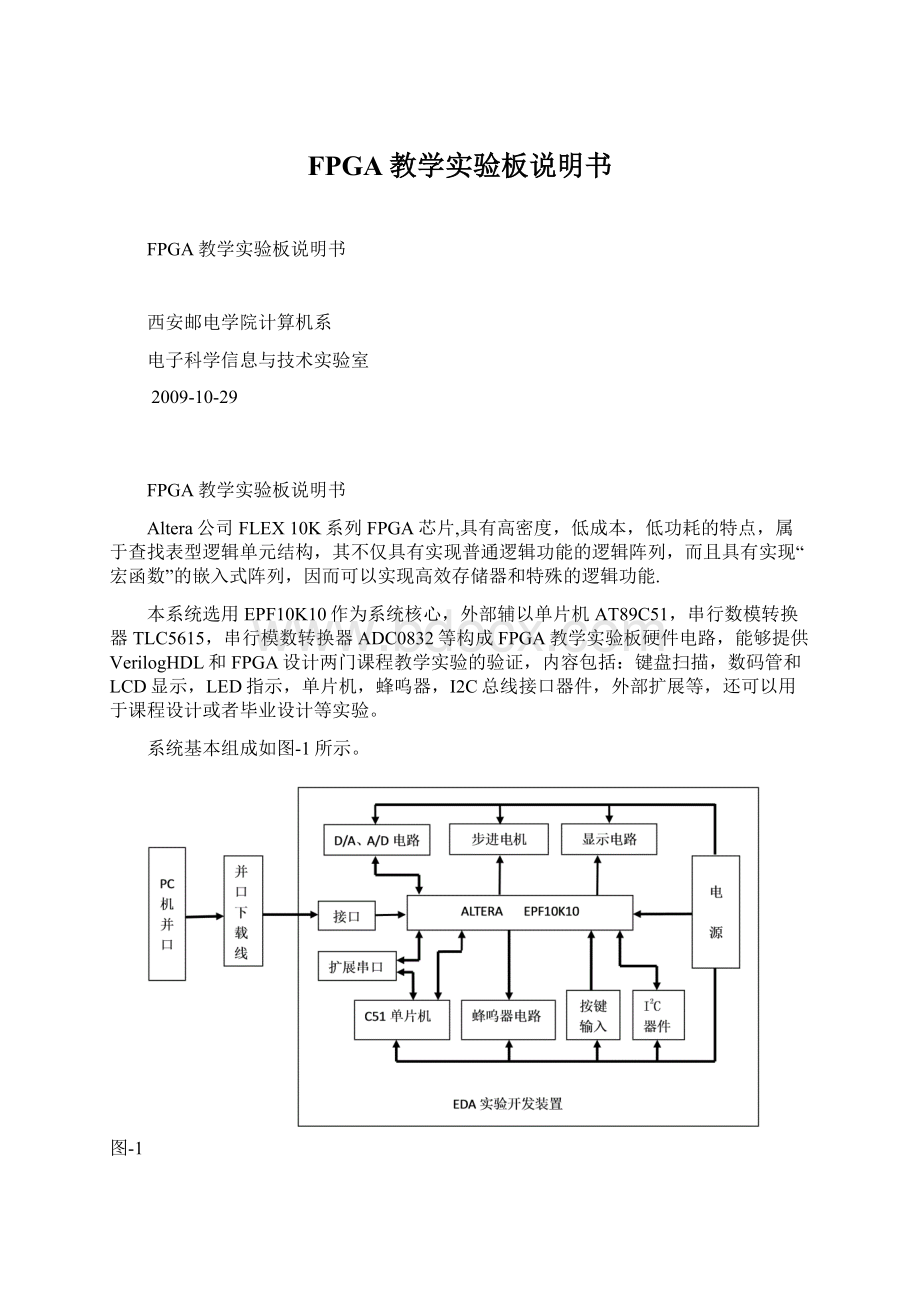

本系统选用EPF10K10作为系统核心,外部辅以单片机AT89C51,串行数模转换器TLC5615,串行模数转换器ADC0832等构成FPGA教学实验板硬件电路,能够提供VerilogHDL和FPGA设计两门课程教学实验的验证,内容包括:

键盘扫描,数码管和LCD显示,LED指示,单片机,蜂呜器,I2C总线接口器件,外部扩展等,还可以用于课程设计或者毕业设计等实验。

系统基本组成如图-1所示。

图-1

现将各部分分述如下:

1.EPF10K10芯片简介及扩展端口说明

(1)FLEX10K系列芯片简介

EPF10K10属于Altera公司FLEX10K系列FPGA芯片,内部结构灵活,内嵌存储块,属于查找表型逻辑单元结构,FLEX10K是工业界第一个嵌入式的PLDs,具有高密度,低成本,低功耗的特点。

FLEX10K把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时又兼收并储了众多可编程逻辑器件的优点来完成普通门阵列的宏功能。

FLEX10K器件的嵌入式阵列和逻辑阵列能够让设计人员轻松地开发出集存储器、数字信号处理器及特殊逻辑等强大功能于一体的芯片。

AlteraFLEX10K系列主流器件如表—1所示。

FPGAFLEX10K系列主流器件

器件

管脚/封装选择

I/O脚

电压供应

速度等级

逻辑单元

门数

RAMBITS

EPF10K10

84PLCC,144TQFP,208PQFP

59,102,134

5.0V

-3,-4

576

10000

6144

EPF10K10A

100TQFP,144TQFP,208PQFP,256BGA

66,102,134,150

3.3V

-1,-2,-3

576

10000

6144

EPF10K20

144TQFP,208PQFP,240PQFP

102,147,189

5.0V

-3,-4

1152

20000

12288

EPF10K30/E

144TQFP,208PQFP,256BGA,484BGA

102,147,176,220

2.5V,5.0V

-1,-2,-3

1728

30000

24576

EPF10K50(V)

144TQFP,208PQFP,240OQFP,256BGA,356BGA,484BGA

102,147,189,191,256,254

3.3V,5.0V

-1,-2,-3

2880

50000

40960

EPF10K70

240PQFP

189

5.0V

-3,-4

3744

70000

18432

EPF10K100A/E

208PQFP,240PQFP,256BGA,356BGA,484BGA

147,189,191,274,338

2.5V,3.3V

-1,-2,-3

4992

100000

49152

EPF10K130E

240PQFP,356BGA,484BGA,600BGA,672BGA

186,274,369,426,413

2.5V

-1,-2,-3

6656

130000

65536

EPF10K200E

240PQFP,356BGA,484BGA,600BGA,672BGA

182,274,470,470,470

2.5V

-1,-2,-3

9984

200000

98304

表—1

FLEX10K系列器件具有以下特性:

高密度阵列嵌入式编程逻辑器件系列;0.5μmCMOSSRAM工艺制造;在电路可配置;所有I/O端口有输入/输出寄存器;快速有效地实现特大规模电路,包括存储器、DSP、专用算术逻辑、微处理器和微控制器等;专用进位链路,可实现快速加法器和计数器功能;专用级联链路,有效地实现高速多输入功能;内部三态总线,支持系统集成;支持多时钟系统的低时滞要求;具有JTAG边界扫描测试内建电路;3.3V或5.0V工作模式;由Altera公司的MAX+PLUSⅡ开发系统提供软件支持;具有84到562引脚的多种封装选择。

FLEX10K系列器件根据规模的大小可分为EPF10K10、EPF10K20、EPF10K30、EPF10K40、EPF10K50、EPF10K70、EPF10K100等系列,其中EPF10K10系列具有10000个典型门、7000-31000个可用门,576个逻辑门,720个触发器,最大用户I/O为150,同时内嵌了可在不降低逻辑功能的情况下应用的40960bit的RAM(每个EBA有2048位)。

并且支持多电压接口,同时内置JTAG边界扫描测试电路。

(2)EPF10K10芯片扩展端口说明

EPF10K10的20和21号I\O口分别接在MAX232的10号和9号管脚上用来完成串口通信的功能。

38、39、41~44和46及47号I\O口与8段拨码开关相连用来构成EPF10K10的一组手动输入。

EPF10K10的12插外接扩展的管脚对应如表—2,EPF10K10的14外接扩展的管脚对应如表—3所示。

12插外接扩展端口说明

EPF10K10管脚

管脚说明

扩展端口编号

EPF10K10管脚

管脚说明

扩展端口编号

14

INT-DONE

1

14

GND

7

11

RDY-nBSY

2

7

CLKUSR

8

141

nRS

3

128

DEV-OE

9

142

nWS

4

55

GCLK1

10

55

CS

5

122

DEV-nCLR

11

3

nCS

6

GND

12

表—2

EPF10K10管脚

管脚说明

扩展端口编号

EPF10K10管脚

管脚说明

扩展端口编号

109

D1

1

GND

8

110

D2

2

54

IN0

9

111

D3

3

124

IN1

10

112

D4

4

56

IN2

11

113

D5

5

126

IN3

12

114

D6

6

19

I\O1

13

116

D7

7

GND

14

14插外接扩展端口说明

表—3

2.EPF10K10芯片配置

器件工作期间,FLEX10K器件将配置数据保存在SRAM中。

因为SRAM数据是易丢失的,SRAM单元必须在器件加电后装入配置数据。

当FLEX10K器件完成配置后,它的存储器和I/O引脚必须被初始化,初始化后,器件进入用户模式,开始系统运行。

对于FLEX10K系列器件,Altera公司提供了四种配置方案:

EPC1配置法、被动串行法、被动并行同步法、被动并行异步法。

这四种配置方案可通过将FLEX10K器件的引脚MSEL1和MSEL0设置为不同的高电平和低电平进行选取,见表—4。

FLEX10K系列器件的四种配置方案

MSEL1

MSEL0

配置方案

GND

GND

EPC1配置或被动串行配置

VCC

GND

被动并行同步配置

VCC

VCC

被动并行异步配置

表—4

EPF1OK10配置文件大小:

器件

配置数据大小(Bits)

配置文件大小(Kbytes)

EPF1OK10

118,000

15

表—5

注:

配置文件大小由.rbf文件决定。

(1)本实验板可以采用Altera公司专用配置芯片EPC1进行配置,由于其采用不可檫除型EEPROM故在实验中我们一般不使用,现给出EPC1接口说明如表—6所示。

EPC1接口说明

EPC1管脚号

管脚说明

EPF10K10管脚

1

DATA

I/O(108)

2

DCLK

DCLK(107)

3

OE

(35)

4

nCS

CONF_DONE

(2)

表—6

(2)同时由于EPF10K10具有JTAG(JointTextActionGroup:

联合测试行动小组)接口,我们也可以使用该接口对EPF10K10进行在线配置,本实验板我们主要采用该接口对EPF10K10进行在线配置。

使用EPF10K10芯片一个特别突出的优点就是:

该芯片可以通过在线配置的方式来调整电路结构、延时信息等,这给电路设计人员调试电路带来极大的方便。

而并口下载电缆ByteBlaster正是将PC机中的配置信息传送到PCB板EPF10K10芯片中必不可少的器件。

ByteBlaster下载电缆组成部分有:

与PC机并口相连的25针插座头、与PCB板插座相连的10针插头和25针到10针的变换电路。

在不同的配置模式下,25针插头和10针插头都对应有相应的名称,该装置采用JTAG模式配置,10针对应针的名称如表—7所示,25针连接线对应名称如表—8所示。

并口下载电缆ByteBlasterMV原理图见图—2。

JTAG模式下ByteBlaster10针接口信号名称

接口引脚号

1

2

3

4

5

6

7

8

9

10

名称

TCK

GND

TDO

VCC

TMS

空

空

空

TDI

GND

EPF10K10引脚号

1

4

34

105

表—7

JTAG模式下ByteBlaster的25针连接线名称

引脚号

2

3

8

11

15

18~25

名称

TCK

TMS

TDI

TDO

VCC

GND

表—8

ByteBlasterMV原理图:

图—2

3.单片机部分

在本实验板中我们选用美国ATMEL公司生产的低电压,高性能CMOS8位单片机AT89C51单片机,片内含4Kbytes的可反复擦写的Flash只读程序存储器和128bytes的随机数据存储器(RAM),器件采用ATMEL公司的高密度,非易失性存储技术生产,兼容标准MCS-51指令系统,元件如图-3所示。

单片机的P1.0~P1.5接在条形拨码开关SWDIP-5上用于配置P1口,P1.5~P1.7接在三态D型锁存器的Q0、D1和Q2管脚上后与DB25接口相联。

P2.0和P2.1接在36和37号I/O口上。

ALE/管脚接在EPF10K10的管脚号为8的I/O口上,外部访问允许端口/VPP接在3口插接件上。

P3.0/RXD,P3.1/TXD分别接在MAX232的12号和11号管脚上,通过MAX232的电平转换作用完成与计算机的通信。

P3.2/,P3.3/分别与EPF10K10的12,13号I/O口相连。

P3.4/T0和P3.5/T1管脚接在17、18号I/O口上,P3.6/和P3.7/接在9、10号I/O口上。

P0口(P0.0~P0.7)是一个8位漏极开路双向输入输出端口,P0.0~P0.7接在EPF10K10的26~33号管脚上。

综上,AT89C51管脚连接可归为表—9,AT89C51的20插扩展如表—10所示,10插扩展如表—11所示。

AT89C51管脚连接

管脚编号

管脚说明

所连芯片端口编号

连接芯片

P2.0

准双向并行I/O口

36

EPF10K10

P2.1

准双向并行I/O口

3

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 教学 实验 说明书

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls