EDA实验 译码器与编码器的设计与仿真Word格式.docx

EDA实验 译码器与编码器的设计与仿真Word格式.docx

- 文档编号:21834518

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:9

- 大小:335.16KB

EDA实验 译码器与编码器的设计与仿真Word格式.docx

《EDA实验 译码器与编码器的设计与仿真Word格式.docx》由会员分享,可在线阅读,更多相关《EDA实验 译码器与编码器的设计与仿真Word格式.docx(9页珍藏版)》请在冰豆网上搜索。

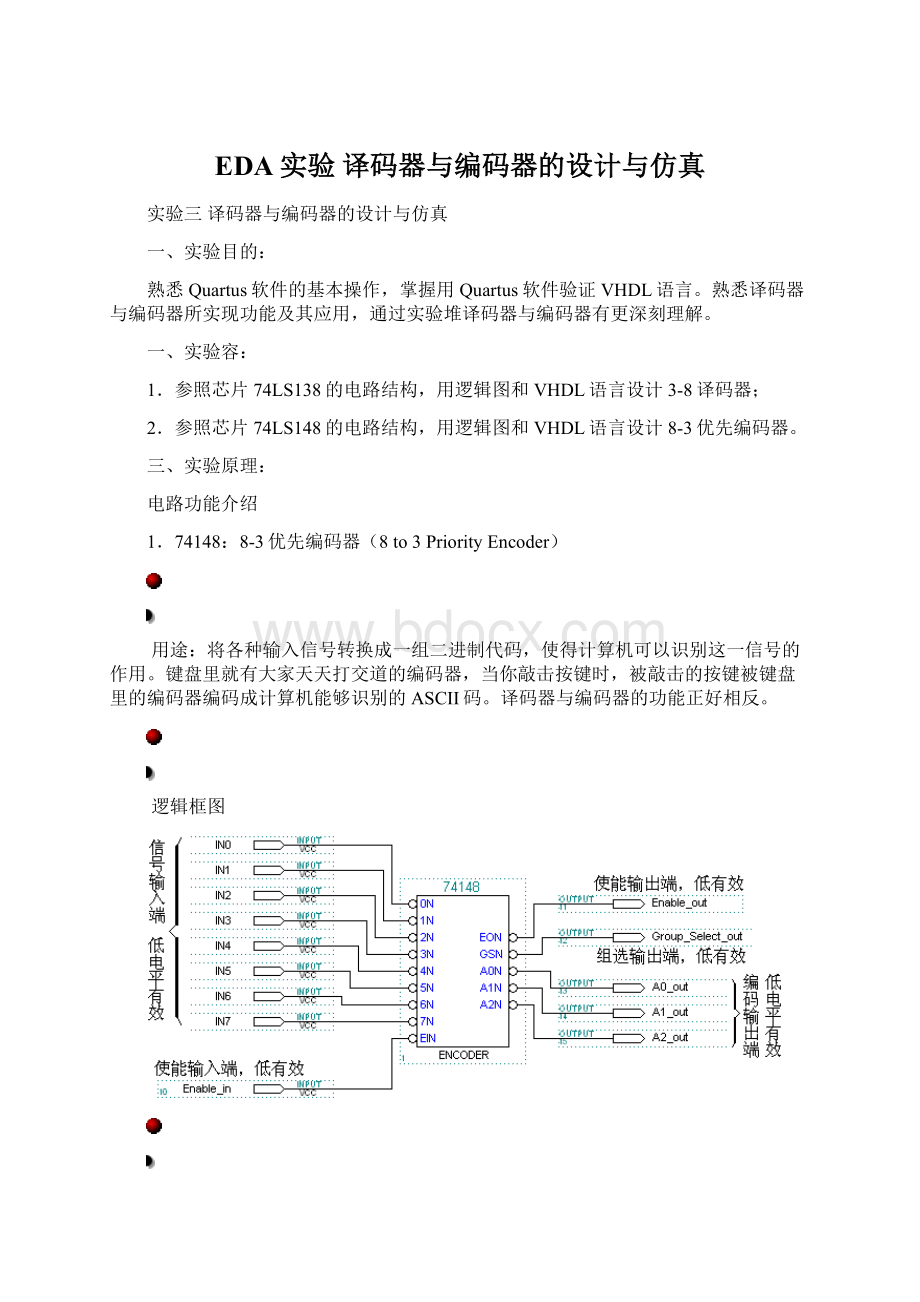

逻辑框图

逻辑功能表

INPUTS

OUTPUTS

EN

0N

1N

2N

3N

4N

5N

6N

7N

A2

A1

A0

EOGS

1

×

×

1

1

1

11

0

0

0

01

1

10

逻辑表达式和逻辑图:

由你来完成。

2.74138:

3-8译码器(3to8Demultiplexer),也叫3-8解码器

用一组二进制代码来产生各种独立的输出信号,这种输出信号可以用来执行不同的工作。

显示器中的像素点受到译码器的输出控制。

逻辑框图:

用逻辑符号(Symbol)来解释该电路输入与输出信号之间的逻辑关系,既省事又直观。

如下图所示。

逻辑功能表:

用真值表来定量描述该电路的逻辑功能。

这个表是设计3-8译码器的关键;

74138的逻辑功能表如下:

INPUT

OUTPUT

Select

Enable

CBA

G1 ̄GHA ̄G2B

̄Y ̄7 ̄Y ̄6 ̄ ̄Y ̄5 ̄ ̄Y ̄4 ̄Y ̄3 ̄Y ̄2 ̄Y ̄1 ̄Y ̄0

100

001

010

011

100

101

110

111

11

0×

11111111

11111110

11111101

11111011

11110111

11101111

11011111

10111111

01111111

注:

使能端G1是高电平有效;

使能端G2是低电平有效,G2=G2AANDG2B。

四、实验步骤:

1、译码器:

(1)在Quartus软件中输入以下程序:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitylbz3is

port(A:

instd_logic_vector(2downto0);

Y:

outstd_logic_vector(7downto0));

endlbz3;

architectureartoflbz3is

begin

Y<

="

10000000"

when(A="

111"

)else

"

01000000"

110"

00100000"

101"

00010000"

100"

00001000"

011"

00000100"

010"

00000010"

001"

00000001"

;

endart;

在Quartus中对程序进行编译如下所示:

从编译界面可以看到程序运行无错误;

通过“RTLviewer”按钮生成综合电路图如下:

(2)根据综合电路图生成如下功能仿真波形:

如仿真图可以看出当A=“001”时Y=“00000010”,同理当A取其他值时Y也输出相应的值,满足译码器逻辑功能表。

(3)对应时序波形如下所示:

2、编码器:

entitylbz31is

instd_logic_vector(0to7);

outstd_logic_vector(0to2));

endlbz31;

architectureartoflbz31is

process(A)

if(A(7)='

0'

)thenY<

elsif(A(7)='

elsif(A(6)='

elsif(A(5)='

elsif(A(4)='

elsif(A(3)='

elsif(A

(2)='

elsif(A

(1)='

elsif(A(0)='

000"

endif;

endprocess;

end;

(2)在Quartus中对程序进行编译如下所示:

(3)根据综合电路图生成如下功能仿真波形:

如仿真图可以看出当A=“10000000”时Y=“110”,同理当A取其他值时Y也输出相应的值,满足译码器逻辑功能表。

(4)对应时序波形如下所示:

五、实验总结:

(1)通过实验掌握了译码器与编码器的原理与运行程序;

(2)加深了对译码器与编码器的使用;

(3)对Quartus软件有更深刻的理解。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA实验 译码器与编码器的设计与仿真 EDA 实验 译码器 编码器 设计 仿真

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx