EDA实验综合设计报告Word文档格式.docx

EDA实验综合设计报告Word文档格式.docx

- 文档编号:21828128

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:17

- 大小:484.20KB

EDA实验综合设计报告Word文档格式.docx

《EDA实验综合设计报告Word文档格式.docx》由会员分享,可在线阅读,更多相关《EDA实验综合设计报告Word文档格式.docx(17页珍藏版)》请在冰豆网上搜索。

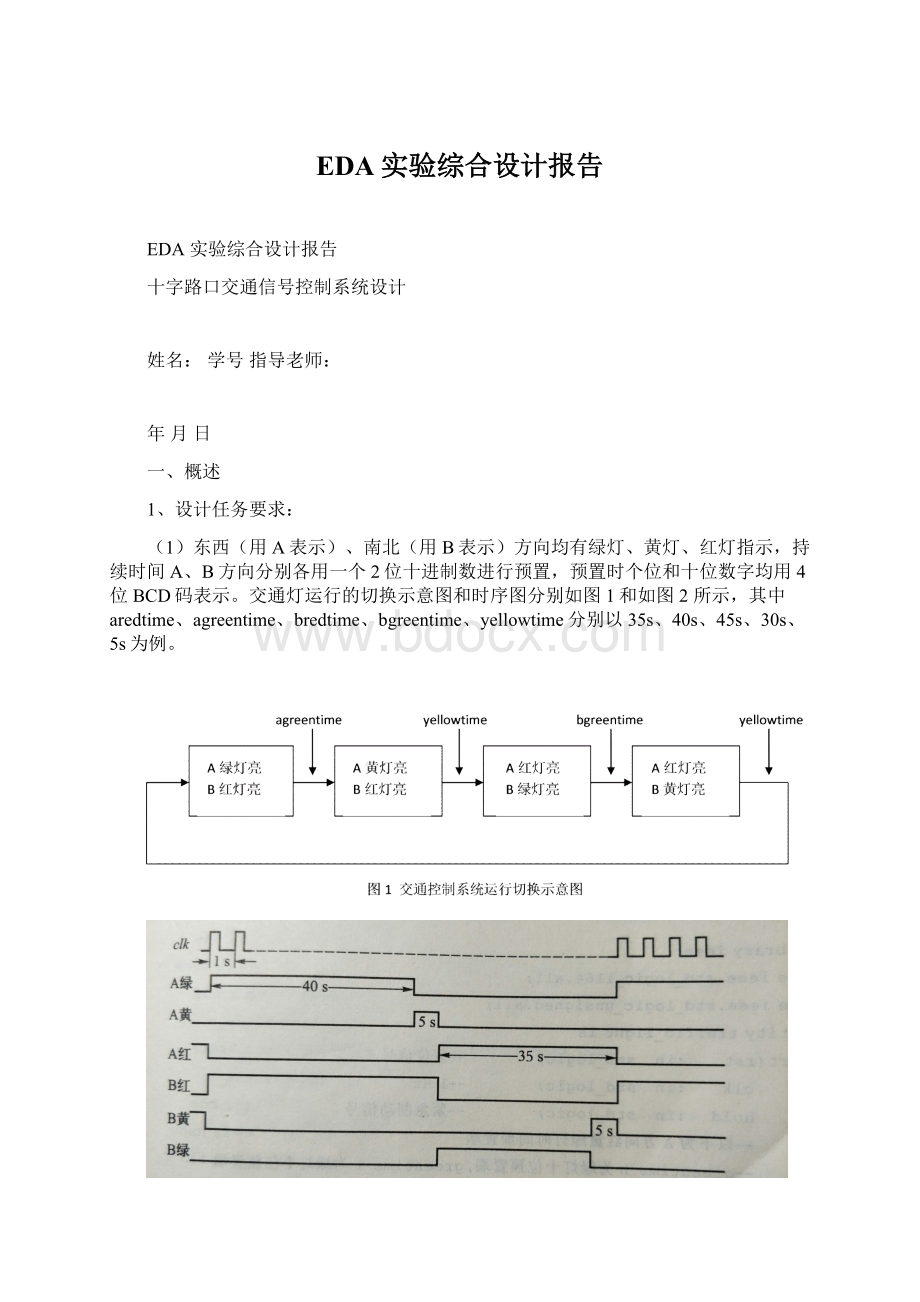

倒计时显示电路实现A路40、5、35秒以及B路45、30、5秒倒计时和显示功能。

整个系统的工作时序受控制器控制,它是系统的核心。

三、实现方法

1、本设计实现方案分析

整个系统的工作过程用状态机进行描述,其状态转移如图3所示,5种状态描述如下:

s0=A方向绿灯亮,B方向红灯亮,此状态持续为agreentime(40s);

s1=A方向黄灯亮,B方向红灯亮,此状态持续yellowtime(5s);

s2=A方向红灯亮,B方向绿灯亮,此状态持续bgreentime(30s);

s3:

A方向红灯亮,B方向黄灯亮,此状态持续yellowtime(5s);

s4:

紧急制动状态,A方向红灯亮,B方向红灯亮,当紧急制动信号有效时(hold=1)进入这种状态。

当紧急制动信号无效(hold=0)时,状态机按照s0—s1—s2—s3—s0循环;

当紧急制动信号有效(hold=1)时,状态机立即转入s4两个方向红灯全亮;

当紧急制动信号再次恢复无效(hold=0)时,状态机会回到初始状态s0继续执行。

状态机进入不同的状态,计数器从不同的初始值开始减法计数,当减到0时,切换到下一个状态。

计数器的计数值通过七段译码器模块译码后显示。

2、本设计实现转移图

图3交通控制系统状态转移图

四、实现过程

1、各模块具体实现

(1)分频器devide.vhd文件

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitydevideis

generic(

sys_clk_fre_value:

integer:

=50000000;

div_clk_fre_value:

=1

);

port(

i_sys_clk:

instd_logic;

clk:

outstd_logic

endentitydevide;

architecturearcdivofdevideis

signalr_div_count:

std_logic_vector(31downto0);

signalr_div_clk:

std_logic;

begin

process(i_sys_clk,r_div_count)

begin

if(i_sys_clk'

eventandi_sys_clk='

1'

)then

if(r_div_count=sys_clk_fre_value/div_clk_fre_value/2-1)then

r_div_count<

=x"

00000000"

;

r_div_clk<

=notr_div_clk;

else

=r_div_count+1;

endif;

endif;

endprocess;

clk<

=r_div_clk;

endarchitecturearcdiv;

(2)主要部分traffic_light.vhd文件

entitytraffic_lightis

port(

rst:

clk:

hold:

ared,agreen,ayellow,bred,bgreen,byellow:

outstd_logic;

aseg7_h,aseg7_l:

outstd_logic_vector(6downto0);

bseg7_h,bseg7_l:

outstd_logic_vector(6downto0)

endtraffic_light;

architecturearcoftraffic_lightis

constantaredtime_h:

std_logic_vector(3downto0):

="

0011"

constantaredtime_l:

0101"

--aredtime35s

constantagreentime_h:

0100"

constantagreentime_l:

0000"

--agreentime40s

constantbredtime_h:

constantbredtime_l:

--bredtime45s

constantbgreentime_h:

constantbgreentime_l:

--bgreentime30s

constantyellowtime_h:

constantyellowtime_l:

--yellowtime5s

signalacount_h,acount_l,bcount_h,bcount_l:

std_logic_vector(3downto0);

typestate_typeis(s0,s1,s2,s3,s4);

signalc_state,n_state:

state_type;

begin

process

waituntilclk'

eventandclk='

ifrst='

then

c_state<

=s0;

else

=n_state;

--statechange状态机的状态转移关系描述

process(hold,c_state,acount_h,acount_l,bcount_h,bcount_l)

n_state<

=c_state;

casec_stateis

whens0=>

ifhold='

=s4;

elsifacount_h="

andacount_l="

=s1;

whens1=>

=s2;

whens2=>

elsifbcount_h="

andbcount_l="

=s3;

whens3=>

=s0;

whens4=>

0'

endcase;

--count十进制倒计时计数器的描述

ifc_state/=n_stateorrst='

ifn_state=s0then

acount_h<

=agreentime_h;

acount_l<

=agreentime_l;

bcount_h<

=bredtime_h;

bcount_l<

=bredtime_l;

elsifn_state=s1then

=yellowtime_h;

=yellowtime_l;

elsifn_state=s2then

=aredtime_h;

=aredtime_l;

=bgreentime_h;

=bgreentime_l;

elsifn_state=s3then

ifacount_l="

1001"

=acount_h-1;

acount_l<

=acount_l-1;

ifbcount_l="

=bcount_h-1;

bcount_l<

=bcount_l-1;

--LEDtrafficlight每个状态下两个路口红绿灯的状态描述

process(c_state)

whens0=>

ared<

='

agreen<

ayellow<

bred<

bgreen<

byellow<

whens1=>

whens2=>

whens3=>

whens4=>

--decodedisplaying倒计时计数器的显示译码

process(acount_h)

caseacount_his

when"

=>

aseg7_h<

0000001"

0001"

1001111"

0010"

0010010"

0000110"

1001100"

0100100"

0110"

0100000"

0111"

0001111"

1000"

0000000"

0000100"

1010"

0001000"

1011"

1100000"

1100"

0110001"

1101"

1000010"

1110"

0110000"

1111"

0111000"

whenothers=>

null;

process(acount_l)

caseacount_lis

aseg7_l<

process(bcount_h)

casebcount_his

bseg7_h<

process(bcount_l)

casebcount_lis

bseg7_l<

endarc;

2、仿真波形

(1)紧急制动

hold=1时,紧急制动,ared=bred=1。

(2)重置

rst=1时,重置,从s0开始运行。

(3)分频器

验证分频器功能,改为二分频。

波形为:

、

(4)整体运行波形

五、实现结果

达到预期效果,LED灯,倒计时计数器,rst、hold键工作正常。

六、结论

存在问题:

倒计时计数的波形不正常;

解决方法:

发现计数器环节有小的编写错误,将“acount_h<

=acount_h+1;

”

“acount_h<

”两条语句中的“+”改成“-”,即“acount_h<

”“acount_h<

”。

收获:

第一次系统进行了数字系统设计,对QuartusII的使用有了自己的理解。

虽然已有知识还是很有限,但因为有了一次完整的设计体验,我相信这对以后的帮助是无穷的。

七、参考文献

【1】孙万蓉、任爱锋等,《数字电路与系统设计》,高等教育出版社,2015年4月

【2】任爱锋、袁晓光,《数字电路与EDA实验》,西安电子科技大学出版社,2017年3月

达到部分预期效果,有些功能未实现。

附录

devide.vhd文件和traffic_light.vhd文件已在正文中给出,下面给出顶层文件、原理图和管脚锁定。

1、顶层文件project_traffic_light.vhd:

entityproject_traffic_lightis

i_sys_clk:

outst

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 实验 综合 设计 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx