《计算机体系结构》课程实验教学大纲ⅡWord格式文档下载.docx

《计算机体系结构》课程实验教学大纲ⅡWord格式文档下载.docx

- 文档编号:21707946

- 上传时间:2023-01-31

- 格式:DOCX

- 页数:13

- 大小:21.32KB

《计算机体系结构》课程实验教学大纲ⅡWord格式文档下载.docx

《《计算机体系结构》课程实验教学大纲ⅡWord格式文档下载.docx》由会员分享,可在线阅读,更多相关《《计算机体系结构》课程实验教学大纲ⅡWord格式文档下载.docx(13页珍藏版)》请在冰豆网上搜索。

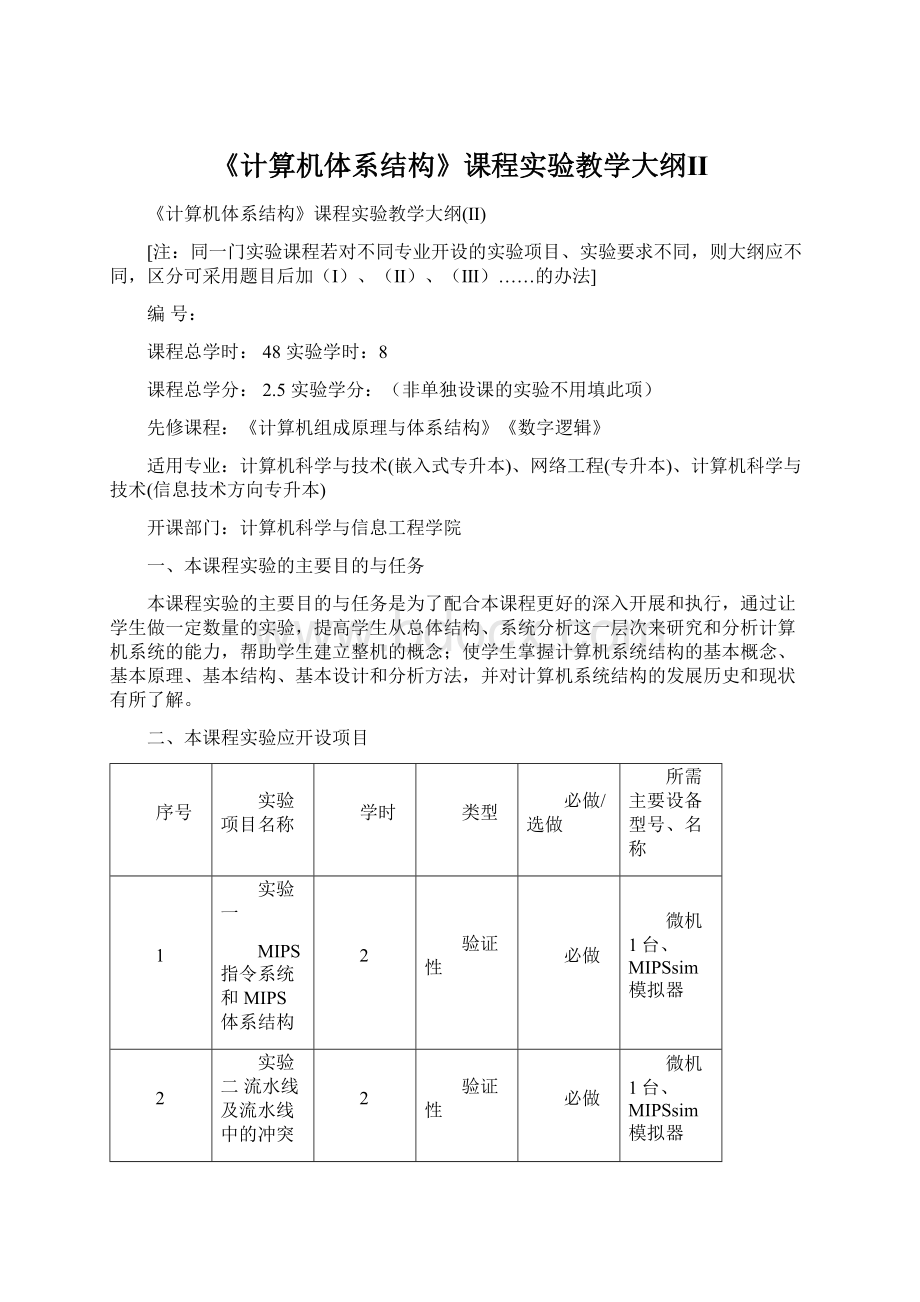

验证性

必做

微机1台、MIPSsim模拟器

实验二流水线及流水线中的冲突

3

实验三指令调度和延迟分支

4

实验四Cache性能分析

微机1台、MyCache模拟器

注:

1、类型---指验证性、综合性、设计性;

2、该表格不够可拓展。

三、各实验项目主要实验内容和基本要求

实验1MIPS指令系统和MIPS体系结构

1.实验目的

(1)了解和熟悉指令级模拟器;

(2)熟练掌握MIPSsim模拟器的操作和使用方法;

(3)熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解;

(4)熟悉MIPS体系结构。

2.实验内容

首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言。

(1)启动MIPSsim(用鼠标双击MIPSsim.exe)。

(2)选择“配置”->

“流水方式”选项,使模拟器工作在非流水方式。

(3)参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中),然后分别以

单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化。

(4)选择“文件”->

“载入程序”选项,加载样例程序alltest.asm,然后查看“代码”窗口,查看程序所在的位置(起始地址为0x00000100)。

(5)查看“寄存器”窗口PC寄存器的值:

[PC]=0X。

(6)执行load和store指令,步骤如下:

1)单步执行一条指令(F7)。

2)下一条指令地址为=0X,是一条(有,无)符号载入(字节,半字,字)指令。

3)单步执行一条指令(F5)。

4)查看R1的值,[R1]=0X。

5)下一条指令地址为0X,是一条(有,无)符号载入(字节,半字,字)指令。

6)单步执行1条指令。

7)查看R1的值,[R1]=0X。

8)下一条指令地址为,是一条(有,无)符号载入(字节,半字,字)指令。

9)单步执行1条指令。

10)查看R1的值,[R1]=0X。

11)单步执行1条指令。

12)下一条指令地址为0X,是一条保存(字节,半字,字)指令。

13)单步执行一条指令(F5)。

14)查看内存BUFFER处字的值,值为0X。

(7)执行算术运算类指令。

步骤如下:

1)双击“寄存器”窗口中的R1,将其值修改为2。

2)双击“寄存器”窗口中的R2,将其值修改为3。

3)单步执行一条指令。

4)下一条指令地址为0x____,是一条加法指令。

5)单步执行一条指令。

6)查看R3的值,[R3]=0x____。

7)下一条指令地址为0x____,是一条乘法指令。

8)单步执行一条指令。

9)查看LO、HI的值,[LO]=0x____,[HI]=0x____。

(8)执行逻辑运算类指令。

1)双击“寄存器”窗口中的R1,将其值修改为0XFFFF0000。

2)双击“寄存器”窗口中的R1,将其值修改为0XFFFF0000。

3)单步执行一条指令。

4)下一条指令地址为0x____,是一条逻辑与运算指令,第二个操作数寻址方式是_____(寄存器直接寻址,立即数寻址)。

5)单步执行一条指令。

6)查看R3的值,[R3]=0x____。

7)下一条指令地址为0x____,是一条逻辑或指令,第二个操作数寻址方式是_____(寄存器直接寻址,立即数寻址)。

8)单步执行一条指令。

9)查看R3的值,[R3]=0x____。

(9)执行控制转移类指令。

1)双击“寄存器”窗口中R1,将其值修改为2。

2)双击“寄存器”窗口中R2,将其值修改为2。

4)下一条指令地址为0x__________,是一条BEQ指令,其测试条件是__________,目标地址为0x__________。

5)单步执行1条指令。

6)查看PC的值,[PC]=0x__________,表明分支__________(成功,失败)。

7)一条指令是一条BGEZ指令,其测试条件是__________,目标地址为0x__________。

8)单步执行1条指令。

9)查看PC的值,[PC]=0x__________,表明分支__________(成功,失败)。

10)下一条指令是一条BGEZAL指令,其测试条件是__________,目标地址为0x__________。

11)单步执行1条指令。

12)查看PC的值,[PC]=0x__________,表明分支__________(成功,失败);

查看R31的值,[R31]=0x_______________。

13)单步执行1条指令。

14)查看R1的值,[R1]=0x_______________。

15)下一条指令地址为0x__________,是一条JALR指令,保存目标地址的寄存器为R______,保存返回地址的目标寄存器为R______。

16)单步执行1条指令。

17)查看PC和R3的值,[PC]=0x_______,[R3]=0x____________。

3.实验要求

通过本实验应达到如下要求:

(1)对指令级模拟器有一定了解;

(2)能够熟练使用MIPSsim模拟器;

(3)理解MIPS指令系统及其特点,加深对MIPS指令操作语义的理解。

4.实验器材

(1)实验平台采用指令级和流水线操作级模拟器MIPSsim;

(2)计算机一台。

实验2流水线及流水线中的冲突

(1)加深对计算机流水线基本概念的理解。

(2)理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作。

(3)加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU性能的影响。

(4)进一步理解解决数据冲突的方法,掌握如何应用定向技术来减少数据冲突引起的停顿。

首先要掌握MIPSsim模拟器的使用方法。

(1)启动MIPSsim。

(2)根据预备知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义。

(用鼠标双击各段,就可以看到各流水寄存器的内容)

(3)参照MIPSsim模拟器使用说明,熟悉MIPSsim模拟器的操作和使用方法。

可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中)。

然后分别以单步执行一条周期、执行多个周期、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化,特别是流水寄存器内容的变化。

(4)选择配置菜单中的“流水方式”选项,使模拟器工作于流水方式下。

(5)观察程序在流水线中的执行情况,步骤如下:

1)选择MIPSsim的“文件”—>

“载入程序”选项来加载pipeline.s(在模拟器所在文件夹下的“样例程序”文件夹中)。

2)关闭定向功能。

这是通过“配置”—>

“定向”(使该项前面没有√号)来实现的。

3)用单步执行一个周期的方式(在“执行”菜单中)或按F7键执行该程序,观察每一个周期中,各段流水寄存器内容的变化、指令的执行情况(“代码”窗口)以及时钟周期图。

4)当执行到第13个时钟周期时,各段分别正在处理的指令是:

IF:

________________________________

ID:

EX:

MEM:

______________________________

WB:

画出这时的时钟周期图。

(6)这时各流水寄存器中的内容为:

IF/ID.IR:

IF/ID.NPC:

ID/EX.A:

ID/EX.B:

ID/EX.Imm:

ID/EX.IR:

EX/MEM.ALUo:

___________________________

EX/MEM.IR:

MEM/WB.LMD:

MEM/WB.ALUo:

MEM/WB.IR:

(7)观察和分析结构冲突对CPU性能的影响,步骤如下:

1)加载structure_hz.s(在模拟器所在文件夹下的“样例程序”文件夹中)。

2)执行该程序,找出存在结构冲突的指令对以及导致结构冲突的部件。

3)记录由结构冲突引起的停顿时钟周期数,计算停顿时钟周期数占总执行周期数的百分比。

4)把浮点加法器的个数改为4个。

5)再次重复步骤①~③的工作。

6)分析结构冲突对CPU性能的影响,讨论解决结构冲突的方法。

(8)观察数据冲突并用定向技术来减少停顿,步骤如下:

1)全部复位。

2)加载data_hz.s(在模拟器所在的文件夹下的“样例程序”文件夹中)。

3)关闭定向功能。

这是通过“配置”->

“定向”(是该项前面没有√号)来实现的。

4)用单步执行一个周期的方式(F7)执行该程序,同时查看时钟周期图,列出在什么时刻发生了RAW(先写后读)冲突。

5)记录数据冲突引起的停顿时钟周期数以及程序执行的总时钟周期数,计算停顿时钟周期数占总执行周期数的百分比。

6)复位CPU。

7)打开定向功能。

“定向”(是该项前面有√号)来实现的。

8)用单步执行一个周期的方式(F7)执行该程序,同时查看时钟周期图,列出在什么时刻发生了RAW(先写后读)冲突,并与步骤3的结果进行比较。

9)记录数据冲突引起的停顿时钟周期数以及程序执行的总时钟周期数。

计算采用定向技术后的性能是原来的几倍。

(1)能够加深对计算机流水线基本概念的理解。

(2)能够理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作。

(3)进一步加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU性能的影响。

(4)进一步理解解决数据冲突的方法和如何应用定向技术来减少数据冲突引起的停顿。

(1)实验平台采用指令级和流水线操作级模拟器MIPSsim;

实验3指令调度和延迟分支

(1)加深对指令调度技术的理解。

(2)加深对延迟分支技术的理解。

(3)熟练掌握用指令调度技术解决流水线中的数据冲突的方法。

(4)进一步理解指令调度技术对CPU性能的改进。

(5)进一步理解延迟分支技术对CPU性能的改进。

首先要掌握MIPSsim模拟器的使用方法。

(2)根据前面的相关知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义(双击各段,就可以看到各流水寄存器中的内容)。

(3)选择“配置”->

“流水方式”选项,使模拟器工作于流水方式下。

(4)用指令调度技术解决流水线中的数据冲突。

1)启动MIPSsim。

2)用MIPSsim的“文件”->

“载入程序”选项来加载schedule.s(在模拟器所在的文件夹下的“样例程序”文件夹中)。

4)执行所载入的程序。

通过查看统计数据和时钟周期图,找出并记录程序执行过程中各种冲突发生的次数、发生冲突的指令组合以及程序执行的总时钟周期数。

5)采用指令调度技术对程序进行指令调度,消除冲突。

将调度后的程序存到after-schedule.s中。

6)载入after-schedule.s。

7)执行该程序。

观察程序在流水线中的执行情况,记录程序执行的总时钟周期数。

8)根据记录结果,比较调度前和调度后的性能。

论述指令调度对于提高CPU性能的作用。

(5)用延迟分支减少分支指令对性能的影响。

2)载入branch.s。

3)关闭延迟分支功能。

“延迟槽”选项来实现的。

4)执行该程序。

观察并记录发生分支延迟的时刻。

5)记录执行该程序所用的总时钟周期数。

6)假设延迟槽有1个,对branch.s进行指令调度,然后保存到“delayed-branch.s”中。

7)载入delayed-branch.s。

8)打开延迟分支功能。

9)执行该程序。

观察其时钟周期图。

10)记录执行该程序所用的总时钟周期数。

11)对比上述两种情况下的时钟周期图。

12)根据记录结果,比较没采用延迟分支和采用了延迟分支的性能之间的不同。

论述延迟分支对于提高CPU性能的作用。

(1)进一步加深对指令调度技术和延迟分支技术的理解,及它们对CPU性能的影响。

(2)能够熟练掌握用指令调度技术解决流水线中的数据冲突的方法。

实验4Cache性能分析

(1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。

(2)掌握Cache容量、相联度、块大小对Cache性能的影响。

(3)掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

(4)理解LRU与随机法的基本思想以及它们对Cache性能的影响。

首先掌握MyCache模拟器的使用方法。

(1)Cache容量对不命中率的影响。

1)启动MyCache。

2)用鼠标单击“复位”按钮,把各参数设置为默认值。

3)选择一个地址流文件。

方法:

选择“访问地址”—>

“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在文件夹下的“地址流”文件夹中选取。

4)选择不同的Cache容量,包括2KB、4KB、8KB、16KB、32KB、64KB、128KB和256KB。

分别执行模拟器(单击“执行到底”按钮即可执行),然后在表7.1中记录各种情况下的不命中率。

表7.1不容量下Cache的不命中率

Cache容量(KB)

16

32

64

128

256

不命中率

地址流文件名:

___________________。

5)以容量为横坐标,画出不命中率随Cache容量变化而变化的曲线,并指明地址流文件名。

6)根据该模拟结果,你能得出什么结论?

(2)相联度对不命中率的影响

1)用鼠标单击“复位”按钮,把各参数设置为默认值。

此时的Cache容量为64KB。

2)选择一个地址流文件。

3)选择不同的Cache相联度,包括2路、4路、8路、16路和32路。

分别执行模拟器(单击“执行到底”按钮即可执行),然后在表7.2中记录各种情况下的不命中率。

表7.2当容量为64KB时,不同相联度下Cache的不命中率

相联度

4)把Cache的容量设置为256KB,重复3)的工作,并填写表7.3.

表7.3当容量为256KB时,不同相联度下Cache的不命中率

5)以相联度为横坐标,画出在64KB和256KB的情况下不命中率随Cache相联度变化而变化的曲线,并指明地址流文件名。

(3)Cache块大小对不命中率的影响

1)用鼠标单击“复位”按钮,把各参数设置为默认值。

2)选择一个地址流文件。

3)选择不同的Cache块大小,包括16B、32B、64B、128B和256B。

对于Cache的各种容量,包括2KB、8KB、32KB、64KB、128KB和512KB。

分别执行模拟器(单击“执行到底”按钮即可执行),然后在表7.4中记录各种情况下的不命中率。

表7.4各种块大小情况下Cache的不命中率

块大小

(B)

512

4)分析Cache块大小对不命中率的影响。

(4)替换算法对不命中率的影响

2)选择地址流文件all.din。

3)对于不同的替换算法、Cache容量和相联度,分别执行模拟器(单击“执行到底”按钮即可执行),然后在表7.5中记录各种情况下的不命中率。

表7.5LRU和随机替换法的不命中率的比较

Cache容量

2路

4路

8路

LRU

随机算法

16KB

64KB

256KB

1MB

4)分析不同的替换算法对Cache不命中率的影响。

通过本实验应达到如下要求:

(1)进一步加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。

(2)进一步理解Cache容量、相联度、块大小对Cache性能的影响。

(3)能够理解降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

(1)实验平台采用Cache模拟器MyCache;

四、实验成绩考核与评定办法

根据出勤情况、实际操作情况和实验报告进行实验评分,成绩评定为优秀(A)、良好(B)、中(C)、及格(D)和不及格(E)五个档次。

实验成绩占期末总成绩的10%。

五、大纲说明

本实验大纲和《计算机体系结构》课程相对应,可以参见《计算机体系结构》课程教学大纲(Ⅰ)。

本课程要求教师以启发式教学为主,充分调动学生的思维,鼓励学生大胆创新,以最优化的方法完成实验。

六、主要参考书目

教材:

《计算机系统结构实践教程》,张晨曦,清华大学出版社,2010年5月

参考书:

《计算机系统结构》,李学干,西安电子科技大学出版社,2009年2月

撰写人:

刘家磊审定人:

批准人:

执行时间:

2011年5月

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机体系结构 课程 实验教学 大纲

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx