CMOS管Word文档格式.docx

CMOS管Word文档格式.docx

- 文档编号:21237765

- 上传时间:2023-01-28

- 格式:DOCX

- 页数:15

- 大小:426.17KB

CMOS管Word文档格式.docx

《CMOS管Word文档格式.docx》由会员分享,可在线阅读,更多相关《CMOS管Word文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

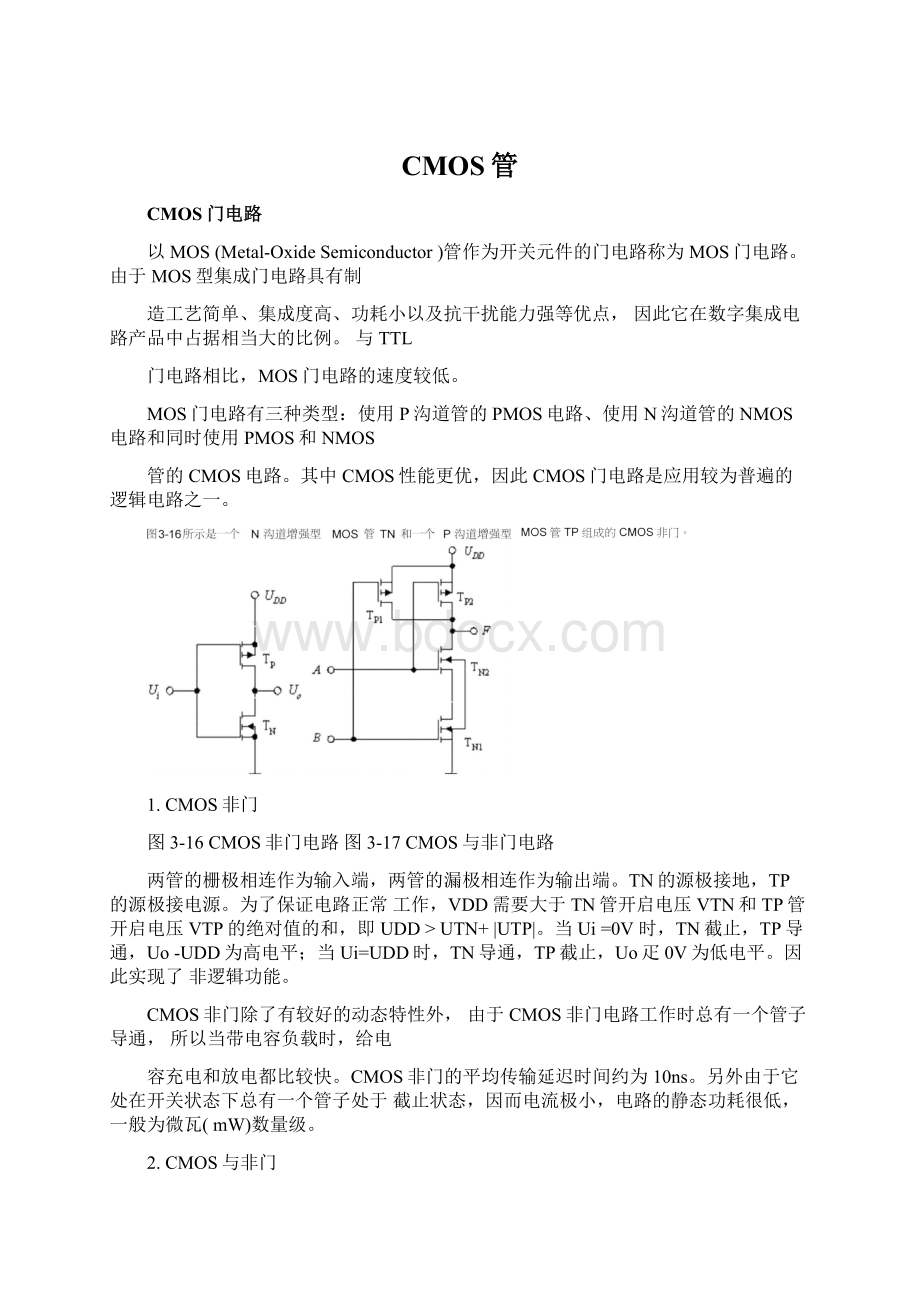

入端连到一个PMOS管和一个NMOS管的栅极。

当输入A、B均为高电平时,TN1和TN2导通,TP1和TP2截止,输出端为低电平;

当输入A、B中至少有一个为低

电平时,对应的TN1和TN2中至少有一个截止,TP1和TP2中至少由一个导通,输出F为高电平。

因此,该电路实现了与非逻辑功能。

3.CMOS或非门

图3-18所示是一个两个输入端的CMOS或非门电路,它由两个并联的NMOS管和两个串联的PMOS管构成。

每个

输入端连接到一个NMOS管和一个PMOS管的栅极。

或非门的逻辑符号如图3-19所示。

当输入A、B均为低电平时,TN1和TN2截止,TP1和TP2导通,输出L为高电平;

只要输入端A、B中有一个为高电平,则对应的TN1和TN2中至少有一个导通,TP1和TP2中便至少有一个截止,使输出F为低电平。

因此,该电路实现了或非逻辑功能。

CMOS非门的基础上增加了NMOS

输出F呈高阻状态;

当使能控制端jJi'

图3-18CMOS或非门电路图3-19或非门逻辑符号4.CMOS三态门图3-20所示是一个低电平使能控制的三态非门,从电路结构上看,该电路是在管TN2和PMOS管TP2构成的。

当使能控制端汕=1时,TN2和TP2同时截止,

=0时,TN2和TP2同时导通,非门正常工作,实现F*的功能。

与TTL三态门一样,CMOS三态门也可用于总线传输。

9tZnn

图3-20CMOS三态门

5.CMOS传输门

图3-21(a)所示是一个CMOS传输门的电路图,它由一个NMOS管TN和一个PMOS管TP并联构成,其逻辑符号如图3-21(b)所示。

图中,TN和TP的结构和参数对称,两管的源极连在一起作为传输门的输入端,漏极连在一起作为

当控制端C=1(VDD),C=0(0V)时,若输出电压Ui在0V〜UDD范围内变化,则两管中至少有一个通导,输入

和输出之间呈低阻状态,相当于开关接通,即输入信号Ui在0V〜UDD范围内都能通过传输门。

当控制端C=0(0V),C=1(UDD)时,输入信号Ui在0V〜UDD范围内变化,两管总是处于截止状态,输入和输出之间呈高阻状态(107W),信号Ui不能通过,相当于开关断开。

由此可见,变换两个控制端的互补信号,可以使传输门接通或断开,从而决定输出端的模拟信号(0V〜UDD之间

的任意电平)是否能传送到输出端。

所以,传输门实质上是一种传输模拟信号的压控开关。

由于MOS管的结构是对称的,即源极和漏极可以互换使用,因此,传输门的输入端和输出端可以互换使用,即

CMOS传输门具有双向性,故又称为可控双向开关。

⑻(b)

图3-21CMOS传输门及其逻辑符号

6.CMOS逻辑门电路的系列及主要参数

(1)CMOS逻辑门电路的系列

•基本的CMOS—4000系列。

•高速的CMOS—HC系列。

•与TTL兼容的高速CMOS—HCT系列。

(2)CMOS逻辑门电路主要参数的特点

•输出高电平UOH(min)=0.9UDD;

输出低电平UOL(max)=0.01UDD。

所以CMOS门电路的逻辑摆幅(即高低电平之差)较大。

•阈值电压Uth约为UDD/2。

•CMOS非门的关门电平UOFF为0.45UDD,开门电平UON为0.55UDD。

因此,其高、低电平噪声容限均达

0.45UDD。

•CMOS电路的功耗很小,一般小于1mW/门;

•因为CMOS电路有极高的输入阻抗,故其扇出系数NO很大,可达到50。

CMOS逻辑门电路

CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器

件。

CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎

所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

MOS管结构图

MOS管主要参数:

1.开启电压Vt

开启电压(又称阈值电压):

使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;

标准的N沟道MOS管,Vt约为3〜6V;

通过工艺上的改进,可以使MOS管的Vt值降到2〜3V。

2.直流输入电阻Rgs

即在栅源极之间加的电压与栅极电流之比

这一特性有时以流过栅极的栅流表示

MOS管的Rgs可以很容易地超过1010Q。

3.漏源击穿电压BVds

在Vgs=0(增强型)的条件下,在增加漏源电压过程中使Id开始剧增时的Vds称为漏源击穿电压

BVds

Id剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

有些MOS管中,其沟道长度较短,不断增加Vds会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后

,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的Id

4.栅源击穿电压BVgs

在增加栅源电压过程中,使栅极电流Ig由零开始剧增时的Vgs,称为栅源击穿电压BVgs。

5.低频跨导gm

在VDS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

gm反映了栅源电压对漏极电流的控制能力

是表征MOS管放大能力的一个重要参数

一般在十分之几至几mAN的范围内

6.导通电阻Ron

导通电阻Ron说明了Vds对Id的影响,是漏极特性某一点切线的斜率的倒数

在饱和区,Id几乎不随Vds改变,Ron的数值很大,一般在几十千欧到几百千欧之间

由于在数字电路中,MOS管导通时经常工作在Vds=0的状态下,所以这时的导通电阻Ron可用原点的Ron来近似

对一般的MOS管而言,Ron的数值在几百欧以内

7.极间电容

三个电极之间都存在着极间电容:

栅源电容Cgs、栅漏电容Cgd和漏源电容CDS

Cgs和Cgd约为1〜3pF

Cds约在0.1〜1pF之间

8.低频噪声系数NF

噪声是由管子内部载流子运动的不规则性所引起的

由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电

流变化

噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

这个数值越小,代表管子所产生的噪声越小

低频噪声系数是在低频范围内测出的噪声系数

场效应管的噪声系数约为几个分贝,它比双极性三极管的要小

一、CMOS反相器

由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

由

N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。

下图表示CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。

为了电路能正常工作,要求电源电压Vdd大于两个管子的开启电压的绝对值之和,即

Vdd>

(Vtn+|Vtp|)。

DP

1.工作原理

Vi处于逻辑0时,相应的电压近似为0V;

而当vi处于逻辑1时,相应

首先考虑两种极限情况:

当

的电压近似为Vdd。

假设在两种情况下N沟道管Tn为工作管P沟道管Tp为负载管。

但是,由于电路是互补对称的,这种假设可以是任意的,相反的情况亦将导致相同的结果。

下图分析了当V|=Vdd时的工作情况。

在TN的输出特性iD—vds(Vgsn—Vdd)(注意Vdsn=vo)上,叠加一条负载线,它是负载管Tp在vsgp=0V时的输出特性iD—vsd。

由于vsgp<

Vt(Vtn=|Vtp|=Vt),负载曲线几乎是一条与横轴重合的水平线。

两条曲线的交点即工作点。

显然,这时的输出电压VOL-0V

(典型值<

10mV,而通过两管的电流接近于零。

这就是说,电路的功耗很小(微瓦量级)

下图分析了另一种极限情况,此时对应于v尸0Vo此时工作管Tn在Vgsn二0的情况下运用,其输出特性iD—VDS几乎与横轴重合,负载曲线是负载管TP在VsGP=VdD时的输出特性iD—VDS。

由图可知,工作点决定了Vo=VohP/dd;

通过两器件的电流接近零值。

可见上述两种极限情况下的功耗都很低。

由此可知,基本CMOS反相器近似于一理想的逻辑单元,其输出电压接近于零或+Vdd,而功耗

几乎为零

2.传输特性

下图为CMOS反相器的传输特性图。

图中Vdd=10V,Vtn=|Vtp|=Vt=

2V。

由于Vdd>

(Vtn+|Vtp|),因此,当Vdd-|Vtp|>

vI>

Vtn时,Tn和Tp两管同时导通。

考虑到电路是互补对称的,一器件可将另一器件视为它的漏极负载。

还应注意到,器件在放大区(饱和区)呈现恒流特性,两器件之一可当作高阻值的负载。

因此,在过渡区域,传输特性变化比较急剧。

两管在Vi=Vdd/2处转换状态。

3.工作速度

CMOS反相器在电容负载情况下,它的开通时间与关闭时间是相等的,这是因为电路具有互补对称的性质。

下图表示当vi=0V时,Tn截止,Tp导通,由Vdd通过Tp向负载电容Cl充电的情况。

由于CMOS反相器中,两管的gm值均设计得较大,其导通电阻较小,充电回路的时间常数较小。

类似

、CMOS门电路

1.与非门电路

下图是2输入端CMOS与非门电路,其中包括两个串联的N沟道增强型MOS管和两个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;

仅当A、B全为高电平时,才会使两个串联的NMOS管都导通,使两个并联的PMOS管都截止,输出为低电平。

HH二T

因此,这种电路具有与非的逻辑功能,即!

■i

n个输入端的与非门必须有n个NMOS管串联和n个PMOS管并联

2•或非门电路

下图是2输入端CMOS或非门电路。

其中包括两个并联的N沟道增强型MOS管和两个串联的P

沟道增强型MOS管

当输入端A、B中只要有一个为高电平时,就会使与它相连的NMOS管导通,与它相连的PMOS管截止,输出为低电平;

仅当A、B全为低电平时,两个并联NMOS管都截止,两个串联的PMOS管都导通,输出为高电平。

因此,这种电路具有或非的逻辑功能,其逻辑表达式为丄-.:

■J

显然,n个输入端的或非门必须有n个NMOS管并联和n个PMOS管并联。

比较CMOS与非门和或非门可知,与非门的工作管是彼此串联的,其输出电压随管子个数的增加而增加;

或非门则相反,工作管彼此并联,对输出电压不致有明显的影响。

因而或非门用得较多。

3.异或门电路

上图为CMOS异或门电路。

它由一级或非门和一级与或非门组成。

或非门的输出工---S。

而

与或非门的输出L即为输入A、B的异或

L=A^B+X

如在异或门的后面增加一级反相器就构成异或非门,由于具有」i1-的功能,因而称为同或门。

异成门和同或门的逻辑符号如下图所示

三、BiCMOS门电路

面的优势,因而这种逻辑门电路受到用户的重视

I.BiCMOS反相器

上图表示基本的BiCMOS反相器电路,为了清楚起见,MOSFET用符号M表示BJT用T表示。

Ti和T2构成推拉式输出级。

而Mp、Mn、Mi、M2所组成的输入级与基本的CMOS反相器很相似。

输入信号vi同时作用于Mp和Mn的栅极。

当vi为高电压时Mn导通而Mp截止;

而当vi为低电压时,情况则相反,Mp导通,Mn截止。

当输出端接有同类BiCMOS门电路时,输出级能提供足够大的电流为电容性负载充电。

同理,已充电的电容负载也能迅速地通过T2放电。

上述电路中Ti和T2的基区存储电荷亦可通过Mi和M2释放,以加快

电路的开关速度。

当vi为高电压时Mi导通,Ti基区的存储电荷迅速消散。

这种作用与TTL门电路的输入级中Ti类似。

同理,当vi为低电压时,电源电压Vdd通过Mp以激励M2使M2导通,显然T2基区的存储电荷通过M2而消散。

可见,门电路的开关速度可得到改善。

2.BiCMOS门电路

根据前述的CMOS门电路的结构和工作原理,同样可以用BiCMOS技术实现或非门和与非门。

如果要实现或非逻辑关系,输入信号用来驱动并联的N沟道MOSFET,而P沟道MOSFET则彼此

串联。

正如下图所示的

2输入端或非门。

JJ1kTt

当A和B均为低电平时,则两个MOSFETMpa和Mpb均导通,Ti导通而Mna和Mnb均截止,输出L为高电平。

与此同时,Mi通过Mpa和MpB被Vdd所激励,从而为T2的基区存储电荷提供一条释放通路。

另一方面,当两输入端A和B中之一为高电平时,则Mpa和Mpb的通路被断开,并且Mna或Mnb导通,将使输出端为低电平。

同时,Mia或Mib为Ti的基极存储电荷提供一条释放道路。

因此,只要有一个输入端接高电平,输出即为低电平。

四、CMOS传输门

MOSFET的输出特性在原点附近呈线性对称关系,因而它们常用作模拟开关。

模拟开关广泛地用于取样一一保持电路、斩波电路、模数和数模转换电路等。

下面着重介绍CMOS传输门。

nE

F5V

-5V

1117

cl

戲路

所谓传输门(TG)就是一种传输模拟信号的模拟开关。

CMOS传输门由一个P沟道和一个N沟

道增强型MOSFET并联而成,如上图所示。

Tp和Tn是结构对称的器件,它们的漏极和源极是可互换的。

设它们的开启电压|Vt|=2V且输入模拟信号的变化范围为-5V到+5V。

为使衬底与漏源极之间的PN结任何时刻都不致正偏,故Tp的衬底接+5V电压,而Tn的衬底接-5V电压。

两管的栅极由互补的信号电压(+5V和-5V)来控制,分别用C和〕表示。

传输门的工作情况如下:

当C端接低电压-5V时Tn的栅压即为-5V,vi取-5V到+5V范围内的任意值时,Tn均不导通。

同时,Tp的栅压为+5V

,Tp亦不导通。

可见,当C端接低电压时,开关是断开的。

为使开关接通,可将C端接高电压+5V。

此时TN的栅压为+5V,vi在-5V到+3V的范围内,Tn导通。

同时Tp的棚压为-5V,vi在-3V到+5V的范围内Tp将导通。

由上分析可知,当viV-3V时,仅有Tn导通,而当vi>

+3V时,仅有Tp导通当vi在-3V到+3V的范围内,Tn和Tp两管均导通。

进一步分析

还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。

换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。

由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。

这是CMOS传输出门的优点。

在正常工作时,模拟开关的导通电阻值约为数百欧,当它与输入阻抗为兆欧级的运放串接时,可以忽略不计。

CMOS传输门除了作为传输模拟信号的开关之外,也可作为各种逻辑电路的基本单元电路。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CMOS

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx