通过Verilog实现交通灯设计实验报告文档格式.docx

通过Verilog实现交通灯设计实验报告文档格式.docx

- 文档编号:20847763

- 上传时间:2023-01-26

- 格式:DOCX

- 页数:10

- 大小:223.62KB

通过Verilog实现交通灯设计实验报告文档格式.docx

《通过Verilog实现交通灯设计实验报告文档格式.docx》由会员分享,可在线阅读,更多相关《通过Verilog实现交通灯设计实验报告文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

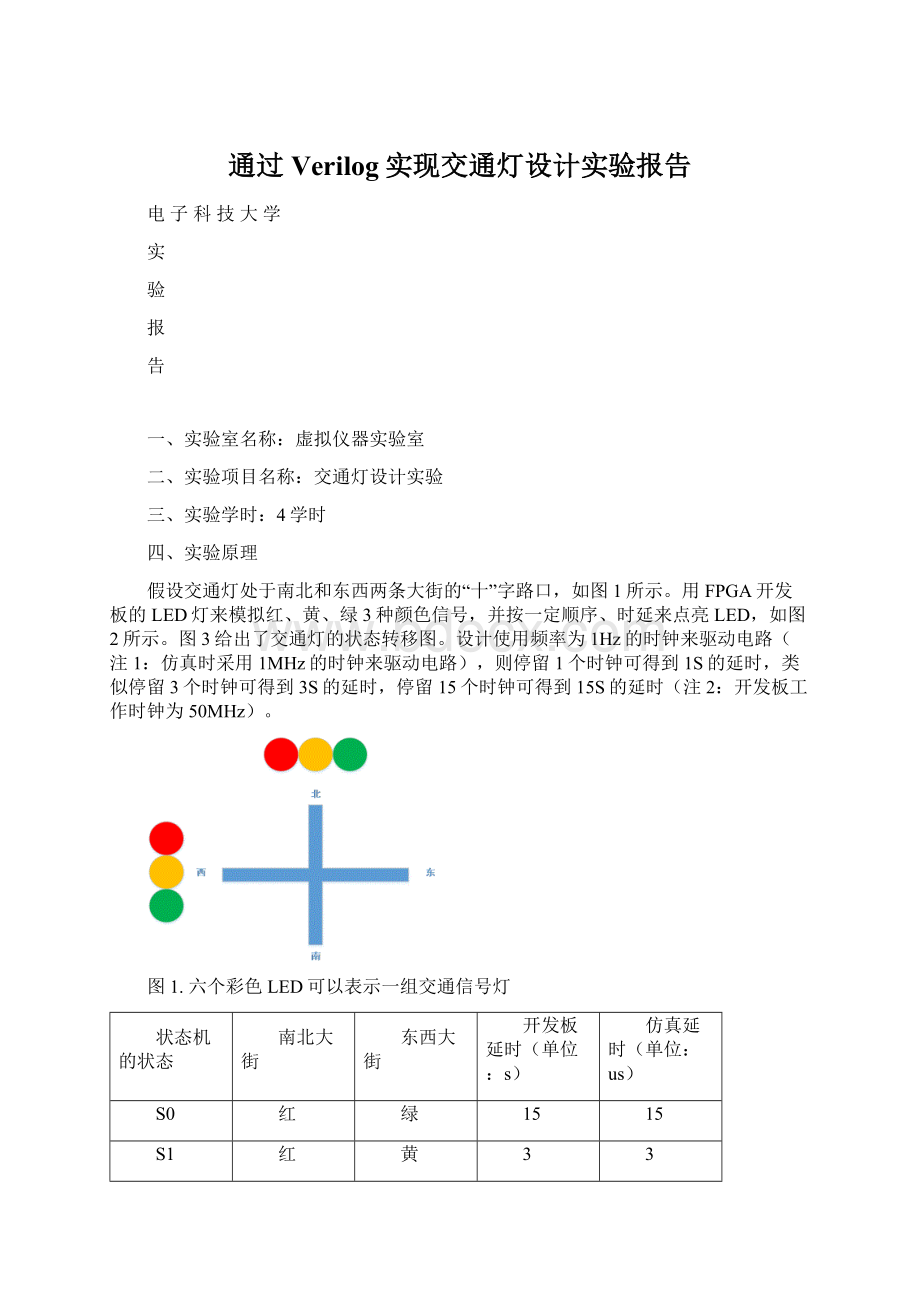

南北大街

东西大街

开发板延时(单位:

s)

仿真延时(单位:

us)

S0

红

绿

15

S1

黄

3

S2

S3

S4

S5

图2.交通灯状态

南北东西

红黄绿红黄绿

S0100001

S1100010

S2100100

S3001100

S4010100

S5100100

图3.交通灯的状态转移图

图4.交通灯的原理框图

五、实验目的

本实验是有限状态机的典型综合实验,掌握如何使用状态转移图来定义Mealy状态机和Moore状态机,熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。

并通过一个交通灯的设计掌握利用EDA软件(XilinxISE13.2)进行HDL代码输入方式的电子线路设计与仿真的详细流程。

。

六、实验内容

在XilinxISE13.2上完成交通灯设计,输入设计文件,生成二进制码流文件下载到FPGA开发板上进行验证。

七、实验器材(设备、元器件)

1、计算机(安装XilinxISE13.2软件平台);

2、BASYS2FPGA开发板一套(带USB-MIniUSB下载线)

八、实验步骤

(1)新建工程,设置器件属性:

在XilinxISE13.2平台中,新建一个工程(注意命名规范),输入工程名称以及工程所在的目录,设置芯片的具体型号(Spartan3EXC3S100E)、封装类型(CP132)以及编码使用的语言(Verilog)。

(详见实验指导书)

(2)Verilog源码文件创建与编辑:

选中器件名字,点击鼠标右键,选中NewSource…,选择VerilogModule以及输入文件名称(详见实验指导书)

(3)语法检查,对设计文件进行综合:

代码编写完成后,在ISE的主界面的处理子窗口的synthesis的工具检查代码语法(CheckSyntax),同时在此窗口可以查看RTL原理图(ViewRTLschematic)、查看技术原理图(ViewTechnologySchematic)以及产生综合后仿真模型(GeneratePost-SynthesisSimulationModel)。

(4)对设计进行行为仿真:

1)产生测试文件模板;

2)完成测试脚本创建与编辑;

3)调出仿真窗口对设计进行仿真;

4)通过波形查看仿真结果。

(5)添加实现约束文件。

(6)UCF文件导入。

(7)FPGA在线下载配置:

1)连接开发板并给开发板供电;

2)边界扫描,初始化链;

3)下载比特流文件;

4)对FPGA进行编程;

5)生成PROM文件;

6)将生成的PROM文件烧到PROM芯片中。

(8)关闭配置界面,不保存任何信息。

(一定不要保存任何信息)

(9)关闭电源重新上电,程序从PROM自动引导到FPGA芯片中。

(10)给开发板断电,清理器件,实验结束。

九、实验数据及结果分析

9.1状态机转移代码

moduletraffic(inputclk,

inputrst,

outputreg[5:

0]lights

);

reg[2:

0]state;

reg[3:

0]count;

parameterS0=3'

b000,S1=3'

b001,S2=3'

b010,

S3=3'

b011,S4=3'

b100,S5=3'

b101;

always@(posedgeclkorposedgerst)begin

if(rst)begin

state<

=S0;

count<

=0;

end

elsebegin

case(state)

S0:

if(count<

15)begin

state<

count<

=count+1;

end

elsebegin

=S1;

S1:

3)begin

=S2;

S2:

=S3;

S3:

=S4;

S4:

=S5;

S5:

defaultstate<

endcase

end

always@(*)begin

case(state)

S0:

lights=6'

b100_001;

S1:

b100_010;

S2:

b100_100;

S3:

b001_100;

S4:

b010_100;

S5:

defaultlights=6'

Endmodule

9.2时钟分频代码

moduleclk_div(inputclk,

outputregclk_1hz

parameterCNT_WIDTH=5;

reg[CNT_WIDTH-1:

0]cnt;

always@(posedgeclkorposedgerst)

begin

if(rst)begin

cnt<

end

elsebegin

=cnt+1;

end

if(rst)

clk_1hz<

elseif(cnt==25)begin

=~clk_1hz;

9.3顶层代码

moduletop(inputmclk,

inputwire[3:

3]btn,

outputwire[7:

2]Led

wireclk_1hz;

wirerst;

assignrst=btn[3];

clk_divclk_div_inst(

.clk(mclk),

.rst(rst),

.clk_1hz(clk_1hz)

);

traffictraffic_inst(

.clk(clk_1hz),

.lights(Led)

endmodule

9.4测试代码

moduletext;

//Inputs

regmclk;

reg[3:

3]btn;

//Outputs

wire[7:

2]Led;

//InstantiatetheUnitUnderTest(UUT)

topuut(

.mclk(mclk),

.btn(btn),

.Led(Led)

initialbegin

//InitializeInputs

mclk=0;

btn=1;

//Wait100nsforglobalresettofinish

#100;

btn=0;

//Addstimulushere

parameterPERIOD=20;

alwaysbegin

#(PERIOD/2)mclk=0;

#(PERIOD/2)mclk=1;

9.5仿真波形代码(对波形进行相关的文字说明,所截取的波形要覆盖所有状态转移)

由图中可以看出,lights显示100001(S0),经过15us后变为100010(S1),接着3us变为100100(S2),再3us变为001100(S3),然后15us变为010100(S4),之后3us变为100100(S5),状态正确。

由图可以看出,clk_1hz周期为1000ns,满足1Mhz的要求

10、实验结论

通过实验,实现了用XilinxISE13.2实现了一个交通灯的电子线路设计与仿真,更加熟练掌握Verilog语言的基本语法。

十一、实验中遇到的问题及相应的解决办法

(1)lights状态不发生变化

答:

在test文件中,令btn初值为1

报告评分:

指导教师签字:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 通过 Verilog 实现 交通灯 设计 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx