通信原理实验指导文档格式.docx

通信原理实验指导文档格式.docx

- 文档编号:20829845

- 上传时间:2023-01-25

- 格式:DOCX

- 页数:27

- 大小:312.99KB

通信原理实验指导文档格式.docx

《通信原理实验指导文档格式.docx》由会员分享,可在线阅读,更多相关《通信原理实验指导文档格式.docx(27页珍藏版)》请在冰豆网上搜索。

1

VPO+

接收功率放大器非倒相输出

2

GNDA

模拟地

3

VPO-

接收功率放大器倒相输出

4

VPI

接收功率放大器倒相输入

5

VFRO

接收滤波器的模拟输出

6

VCC

正电源引脚,Vcc=+5V±

5℅

7

FSR

接收的帧同步脉冲,它启动BCLKR,于是PCM数据移入Dr,FSR为8KHz脉冲序列。

8

Dr

接收帧数据输入,PCM数据随着FSR前沿移入Dr。

9

BCLKR\

CLKSEL

在FSR的前沿后把数据移入Dr的位时钟,其频率可从64KHz到2.048MHz。

另一方面它也可能是一个逻辑输入,以此为在同步模式中的主时钟选择频率1.536MHz/1.544MHz或2.048MHz。

BCLKR用在发送和接收两个方向。

10

MCLKR/

PDN

接收主时钟。

其频率可以为1.536MHz、1.544MHz或2.048MHz。

它允许与MCLKx异步,但为了获得最佳性能应当与MCLKx同步,当MCLKR连续联在低电位时,MCLKx被选用为所有内部定时,当MCLKR连续工作在高电位时,器件就处于掉电模式。

11

MCLKx

发送主时钟,其频率可以是1.536MHz,1.544MHz或2.048MHz,它允许与MCLKR异步,同步工作能实现最佳性能。

12

BCLKx

把PCM数据从Dx上移出的位时钟,其频率可从64KHz变至2.048MHz,但必须与MCLKx同步。

13

Dx

由FSx启动的三态PCM数据输出

14

FSx

发送帧同步脉冲输入,它启动BCLKx,并使Dx上PCM数据移出。

15

TSx

开漏输出,在编码器时隙内为低电平脉冲。

16

ANLB

模拟环回路控制输入,在正常工作时必须置为逻辑“0”,当拉到逻辑“1”时,发送滤波器和发送前置放大器输出的连接线被断开,而改为和接收功率放大器的VPO+输出连接。

17

GSx

发送输入放大器的模拟输出。

用来在外部调节增益。

18

VFxI-

发送输入放大器的倒相输入。

19

VFxI+

发送输入放大器的非倒相输入。

20

VBB

负电源引脚,VBB=-5V±

3.实验系统工作原理

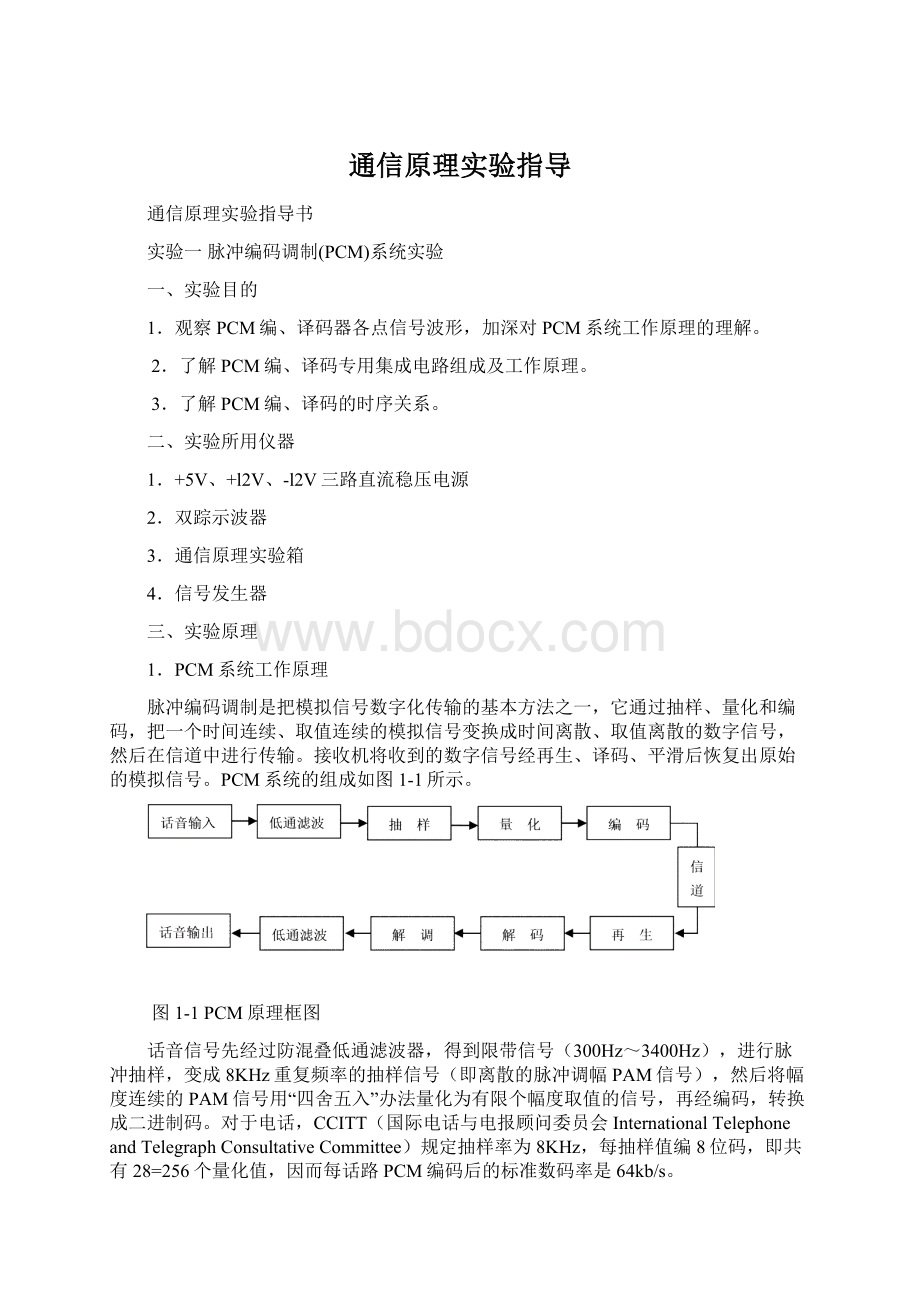

实验PCM系统的完整电路如图1-6所示。

图中发送通道和接收通道的电路见图1-4和图1-5。

图1-5接收通道

图1-4发送通道

图1-7PCM系统总电路图

编译码器的工作是由时序电路控制的。

在编码电路中,进行取样、量化、编码,译码电路经过译码低通、放大后输出模拟信号,把这两部分集成在一个芯片上就是一个单路编译码器,它只能为一个用户服务,即在同一时刻只能为一个用户进行A/D及D/A变换。

如果同时有多路信号时分复用,则需要多个单路编译码器协同工作。

单路编译码器变换后的8位PCM码字是在一个时隙中被发送出去,这个时序号是由A/D控制电路来决定的,而在其它时隙时编码器是没有输出的。

同样在一个PCM帧里,它的译码电路也只能在一个由它自己的时序里,从外部接收8位PCM码。

单路编译码器的发送时序和接收时序可由外部电路来控制。

只要向A/D控制电路或D/A控制电路发某种命令即可控制单路编译码器的发送时序和接收时序号,从而也可以达到总线交换的目的。

不同的单路编译码器对其发送时序和接收时序的控制方式都有所不同,有些编译码器有二种方式,一种是编程法,即给它内部的控制电路输进一个控制字,分配其时隙;

另一种是直接控制,这时它有两个控制端,我们定义为FSx和FSR,它们是周期性的,并且它的周期和多路PCM的帧周期相同,为125μs,这样,每来一个FSx,编译码器就输出一个PCM码字,每来一个FSR,编译码器就从外部输入一个PCM码字。

编译码器的功能比较强,它既可以进行A律变换,也可以进行μ律变换,它的数据既可以固定速率传送,也可以可变速率传送,它既可以传输信令帧也可以选择它传送无信令帧,并且还可以控制它处于低功耗备用状态等,到底使用它的什么功能可由用户通过一些控制来选择。

在本实验中我们选择它进行A律变换,以2.048Mbit/s来传送信息,信息帧为无信令帧,它的发送时序与接收时序直接受FSx和FSR控制。

还有一点,编译码器一般都有一个PDN降功耗控制端,PDN=l时,编译码能正常工作,PDN=0时,编译码器处于低功耗状态,这时编译码器其它功能都不起作用,我们在设计时,可以实现对编译码器的降功耗控制。

四、实验步骤与内容

1.对照说明书确认实验板上的元件和测试点的位置(元件位置见图1-7)。

检查确认板上无错误接线及杂物。

2.正确设置开关位置:

K1011-2、K5011—2。

3.打开电源开关,检查电源电压。

按下按键开关:

K2、K3、K100、K500。

按下“复位”、“开始”与“PCM”功能键,显示代码“2”。

控制系统为PCM实验系统提供三组信号,即:

a.2048KHz主时钟信号;

b.8KHz收发分帧同步信号;

c.使能信号,低电平有效。

4.在不加信号的情况下,参照图1-6实验电路,用双踪示波器观察TP501—TP508各点波形(包括脉冲形状、幅值、重复频率、相位关系)。

5.从信号发生单元TP106引入单音频信号至S501中,再测量TP501—TP508各点波形并记录下来,测量中注意下列测试点波形要用示波器双通道同时观测,并分析两信号之间幅度、频率和相位关系。

①TP504与TP505②TP501与TP508

五、实验报告要求

1.画出实验电路的实验方框图,并叙述其工作过程。

2.画出实验过程中各测量点的波形图,注意相位关系,注明信号频率、峰-峰值。

图1-7脉冲编码调制(PCM)系统元器件位置结构图

六、注意事项

编译码器芯片是本实验中最易受损器件,稍有不慎就有烧坏的可能,所以在实验中要求特别细致,做到以下几点:

(1)在使用中要注意编译码器芯片说明中的要求。

(2)在实验中要细心,接线正确,避免因接线错误或探头抖动等导致测点短路;

(3)在关电源之前应该首先将所有外来的输入信号(如时钟,同步脉冲等)去除,即先关掉其他几部分的电源,最后关编译码器的电源,以免在关电后仍有信号输入。

并将示波器去掉,以免关电后因示波器引起的静电对芯片产生影响。

实验二增量调制系统实验

l.加深理解增量调制的基本原理。

2.加深理解连续可变斜率增量调制系统的电路组成与基本工作原理。

3.了解不同速率的编码时的输出波形。

4.了解系统的过载持性、动态范围以及最大量化信噪比等三大指标的测试方法。

1.+5V、+l2V、-l2V三路直流稳压电源

2.双踪示波器

1.增量调制的基本原理

增量调制是由PCM发展而来的模拟信号数字化的另一种编码方式,增量调制编码基本原理是只用一位编码,这一位码不是表示信号抽样值的大小,而是表示抽样幅度的增量特性,即采用一位二进制数码“1”或“0”来表示信号在抽样时刻的值相对于前一个抽样时刻的值是增大还是减小,增大则输出“1”码,减小则输出“0”码。

输出的“1”、“0”只是表示信号相对于前一个时刻的增减,不表示信号的绝对值。

增量调制又可以分为基本增量调制、连续可变斜率增量调制、总和增量调制。

其原理见下图2-1:

图2-1增量调制系统框图

2.芯片MC34115简介

MC34115是单片增量调制解调器大规模集成电路芯片。

其内部组成框图分别如图2-2、图2-3所示,引脚排列图见2-4所示,引脚功能如表2-1所示。

由图2-2可知,MC34115集成电路内部电路由下列八个部分组成:

模拟输入运算放大器、数字输入运算放大器、V—I电压/电流转换运算放大器、积分运算放大器、斜率过载检测电路、斜率极性控制电路、工作状态选择开关电路、Vcc/2稳压电源。

图2-3增量调制系统编码器电路原理方框图

图2-4增量调制系统译码器电路原理方框图

图2-2MC34115引脚排列图

表2-1:

引脚功能说明

ANI(Analoginput)

模拟信号输入端。

输入音频模拟信号经过直流分量转换为内部参考电压值,则应在该端与第10脚(Vcc/2端)间接入偏置电阻。

ANF(AnalogFeedback)

模拟反馈输入端。

该端为集成电路内模拟比较器的同相输入端。

当该集成电路工作于编码方式时,其本地解码信号从该端输入至内部的模拟比较器;

当该集成电路工作于译码方式时,该端不用,可接到第10脚(Vcc/2端),也可以接地或悬空。

SYL(SyllabicFilter)

量阶控制信号输入端。

当从第11引脚COIN(一致脉冲输入端)端输出的负极性一致脉冲经过音节平滑滤波器,得到量阶控制电压输入到该第3引脚至内部V—I变换运算放大器内,控制积分器量阶的大小。

在进行音频信号编码时的典型时间常数为6~50ms。

GC(GainControlInput)

增量控制输入。

该芯片内部的V—I变换运算放大器使该端电压跟随量阶控制电压变化,变换速率为0.5V/μs。

因此输入该端的电流大小由外接调整电阻Rx决定,为保证电路稳定工作,Rx值一般不超过l0KΩ。

VREF(RefInput)

参考电压输入端。

该端为积分运算放大器的同相输入端,用于调节模拟信号的直流分量。

在进行编码时,为保证输入输出模拟信号有相同的直流分量,该端应通过偏置电阻与Vcc/2端相连。

在实验电路中视实际情况,可接入偏置电阻R(10K)。

FIL(FilterInput)

外接积分器输入端。

该端为积分运算放大器的反相输入端,用于外接元件组成积分滤波器。

在编码时,如果第一引脚即音频模拟信号输入端的输入信号幅度大于第二引脚,即大于模拟反馈输入端的反馈输入信号幅度,则积分电流输入到该引脚。

反之,积分电流输出该引脚。

在解码时第13引脚即接收数据输入端,若输入数据为“1”码,则积分电流输入该端,反之则积分电流输出该端。

ANO(AnalogOutput)

模拟信号输出端。

该端为积分运算放大器输出端。

它根据第13引脚即DDI(接收数据输入端)端输入数据恢复的音频模拟信号从该端输出到积分网络中。

V-

负电源端。

当该集成电路单电源供电时该端接地。

若正、负电源供电时该端接至负电源。

在实验电路中,采用单电源+12V供电,故该引脚接地。

DOT(DataOutput)

发送编码数据输出端。

该集成电路将输入音频信号编成信码后从该端输出,其输出电平与TTL或CMOS兼容。

Vcc/2(Vcc/2Output)

参考电压输出端。

该端在单电源供电时,输出的参考电压值为电源电压的一半,可用来建立各运算放大器的直流工作点,输出电流至少为10mA。

使用时一般接旁路电容到地。

COIN(CoincidenceOutput)

一致脉冲输入端。

当该集成电路内的移位寄存器的各输出为全“1”码或全“0”码时,该端输出负极性一致脉冲,该脉冲经外接音节平滑滤波器后得到量阶控制电压。

DTN(DigitalThreshold)

接口电平控制端。

该端用于控制数字输入端接口电平。

当该集成电路需要与CMOS电路接口时,该端应与Vcc/2端(即第10引脚)相连;

当该集成电路需要与TTL电路接口时,则该端应该比V-高两个二极管电压降的电位。

DDI(DigitalDataInput)

接收数据输入端。

当该集成电路用于译码时,其接收端的信码从该端输入至该芯片内的数字运算放大器进行比较。

在时钟下降沿前后,该端的输入数据应保持有效0.5μs,该芯片如果用作编码,则该因引脚可不用。

CP(ClockInput)

编译码时钟输入端。

该端输入时钟信号的频率决定于该集成电路的工作速率。

该输入时钟信号最小正脉冲宽度为300ns,最小负脉冲宽度为600ns,在本实验电路中,该端的时钟信号输入可通过K201进行选择不同的时钟速率,其时钟速率有:

64KHz、32KHz、16KHz、8KHz,四种方式可选择。

E/D(Encode/Decode)

编码/译码方式控制输入端。

当该端用于选择编码工作方式时,应接高电平,使该芯片内的模拟运算放大器与移位寄存器连接;

在本实验电路中,该端由中央集中控制器U1(89C51)进行控制,由软件运行输出高电平送至该端;

当该端用于选择译码工作方式时,该端应接低电平,使该芯片内的数字运算放大器与移位寄存器相连接,即做增量调制译码实验时,该端由中央集中控制器U1(89C51)进行管理与控制,由软件运行,输出低电平送至该端。

Vcc

正电源输入端。

该端与GND端电压差为4.75~16.5V之内,在本实验电路中,该Vcc端为+l2V电源。

3.实验电路工作原理

图2-5是增量调制编码器电原理图,图2-6是增量调制译码器电原理图。

(1)编码电路工作过程

由图2-5可知,音频模拟输入信号由输入插座S201进入,经过发送通道电路输出到电解电容E201,经过耦合至MC34115的模拟信号输入端,第1引脚。

因为是编码工作方式,所以中央集中控制器输出高电平送至本级U201(MC34115)的第15引脚。

此时芯片内的模拟输入运算放大器与移位寄存器接通,从第1引脚(ANI)输入的音频模拟信号与2脚(ANF)输入的本地解码信号相减并放大得到误差信号,然后根据该信号极性编成数据信码从第9引脚(DOT)输出。

该信码在片内经过3级或4级移位寄存器及检测逻辑电路。

检测过去的3位或4位信码中是否为连续“1”或连续“0”的出现。

一旦当移位寄存器各级输出为全“1”码或全“0”码时,表明积分运算放大器增益过小,检测逻辑电路从第11引脚(COIN端)输出负极性一致脉冲,经过外接音节平滑滤波器后得到量阶控制电压输入到第3引脚(SYL端),由内部电路决定,GC端电压与SYL端相同,这相当于量阶控制电压加到GC端。

该端外接调节电位器W202,调节W202为一固定电位,改变此电位器即可改变GC端的输入电流,以此控制积分量阶的大小,从而改变环路增益,展宽动态范围。

第4引脚(GC)输入电流经过V—I变换运算放大器,再经量阶极性控制开关送到积分运算放大器,极性开关则由信码控制。

外接积分网络(由R207、C201组成)与芯片内部积分运算放大器相连,在二次积分网络上得到本地解码信号送回ANF端与输入信号再进行比较,以完成整个编码过程。

该芯片的外围辅助电路由三大部分组成:

音节平滑滤波器电路、二次积分网络电路,其中R207、R212、C202组成一次积分电路,R206、C201组成二次积分电路。

在没有音频模拟信号输入时,话路是空闲状态,则编码器应能输出稳定的“1”、“0”交替码,这需要一最小积分电流来实现,该电流可通过增大调节电位器来获得。

由于极性开关的失配,积分运算放大器与模拟输入运算放大器的电压失调,此电流不能太小,否则无法得到稳定的“l”、“0”交替码。

该芯片总环路失调电压约为1.5mv,所以量阶可选择为3mv。

当本地积分时间常数1mS时,则最小积分电流取1OμA,就可得到稳定的“l”、“0”交替码。

如果输出不要求有稳定的“l”、“0”交替码,量阶可减小到0.lmV,而环路仍可正常工作。

(2)译码电路工作过程

由发端送来的编码数据信号加至信号转接开关K802的引脚,通过该开关的作用,把信号送到U80l(MC34115)芯片的第13引脚,即接收数据输入端。

对译码电路,CPU中央控制单元送出低电平至U801(MC34115)的15引脚,使模拟输入运算放大器与移位寄存器断开,而数字输入运算放大器与移位寄存器接通,这样,接收数据信码经过数字输入运算放大器接形后送到移位寄存器,后面的工作过程与编码时相同,只是解调信号不再送回第2引脚,而是直接送入后面的积分网络中,再通过接收通道低通滤波电路滤去高频量化噪声,然后送出话音信号。

虽然增量调制系统的话音质量不如脉冲编码调制PCM数字系统的音质,但是增量调制电路比较简单,能从较低的数码率进行编码,通常为16~32kbit/s,而且在用于单路数字电话通信时,不需要收发端同步,故增量调制系统仍然广泛应用于数字话音通信系统中,如应用在传输数码率的军事,野外及保密数字电话等方面。

图2-5增量调制编码器电路原理图

图2-6增量调制译码器电路原理图

四、实验内容与步骤

1.对照说明书确认实验板上的元件和测试点的位置(元件位置见图2-7和图2-8)。

图2-7增量调制编码电路元器件位置结构图

图2-8增量调制译码电路元器件位置结构图

2.设置跳线开关位置:

K1011-2、K2011-2、K8011-2、K8021-2。

3.打开电源开关,检查电源电压。

K2、K3、K100、K200、K800。

按一下“复位”、“开始”与“Δ译码”功能键,显示代码“7”。

4.在不加信号的情况下,用二踪示波器测TP20l—207、TP80l—804各测量点的波形(包括脉冲形状、幅值、重复频率、相位关系)。

5.从信号发生单元TP106引入单音频信号至S201中,再测量TP20l—207、TP80l—804各点波形并记录下来。

6.输入信号幅度、频率保持不变,改变输入时钟的速率,如64KHz、32KHz、16KHz,分别逐点测TP20l—207、TP80l—804各点波形,并分析测试结果。

编译码时钟速率由K201、K801跳线开关决定。

K2011-2=64KHz;

K2012-3=32KHz;

K2014-5=16KHz;

K2015-6=8KHz

K8011-2=64KHz;

K8012-3=32KHz;

K8014-5=16KHz;

K8015-6=8KHz

1.画出实验电路的方框图,并叙述其工作过程。

2.画出实验过程中各测量点的波形图,注意相位关系,注明信号频率、峰-峰值。

1.实验前认真阅读本实验指导书。

2.在实验中要细心,接线正确,避免因接线错误或探头抖动等导致测点短路;

3.在关电源之前应该首先将所有外来的输入信号(如时钟,同步脉冲等)去除,即先关掉其他几部分的电源,最后关编译码器的电源,以免在关电后仍有信号输入。

实验三FSK调制解调系统实验

l.加深理解FSK调制工作原理及电路组成。

2.加深理解利用锁相环解调FSK的原理和实现方法。

1.+5V、+l2V、-l2V三路直流稳压电源

2.双踪示波器

3.通信原理实验箱

4.万用表

(一)FSK调制电路工作原理

图3-1FSK调制电原理框图

数字调频又可称作移频键控(FSK),它是利用载频频率变化来传递数字信息。

这种调制解调方式容易实现,抗噪声和抗衰减性能较强,因此在中低速数据传输系统中得到了较为广泛的应用。

本实验电路中,载频频率经过本实验电路分频而得到的两个不同频率的载频信号,则为相位连续的数字调频信号。

图3-1为FSK调制器原理框图。

图3-2为FSK调制器电路图。

图3-2FSK调制电路电原理图

由图3-2可知,输入的基带信号由转换开关K904转接后分成两路,一路控制32KHz的载频,另一路经倒相去控制16KHz的载频。

当基带信号为“1”时,模拟开关1打开,模拟开关2关闭,此时输出f1=32KHz,当基带信号为"

0"

时,模拟开关1关闭,模拟开关2开通。

此时输出f2=16KHz,于是可在输出端得到已调的FSK信号。

电路中的两路载频(f1,f2)由内时钟信号发生器产生,经过开关K9Ol,K902送入。

两路载频分别经射随、选频滤波、射随、再送至模拟开关U9Ol:

A与U90l:

B(4066)。

(二)FSK解调电路工作原理

FSK集成电路模拟锁相环解调器由于性能优越,价格低廉,体积小,所以得到了越来越广泛的应用。

FSK集成电路模拟锁相环解调器的工作原理是十分简单的,只要在设计锁相环时,使它锁定在FSK的一个载频f1上,对应输出高电平,而对另一载频f2失锁,对应输出低电平,那么在锁相环路滤波器输出端就可以得到解调的基带信号序列。

FSK锁相环解调器中的集成锁相环选用了MCl4046。

MCl4046集成电路内有两个数字式鉴相器(PDI、PDII)、一个压控振荡器(VCO),还有输入放大电路等,环路低通滤波器接在集成电路的外部,引脚排列图见3-3所示,引脚功能说明见表3-1所示。

图3-3MC14046引脚排列图

表3-1:

PDO3

相位比较器2输出的相位差信号,为上升沿控制逻辑。

PDO1

相位比较器1输出的相位差信号,它采用异或门结构,即鉴相特性为PDO1=PDI1⊕PDI2。

PDI2

相位比较器输入信号,通常PD为来自VCO的参考信号。

VCOO

压控振荡器的输出信号。

INH

控制信号输入,若IN

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 通信 原理 实验 指导

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx