3篇7章习题解答文档格式.docx

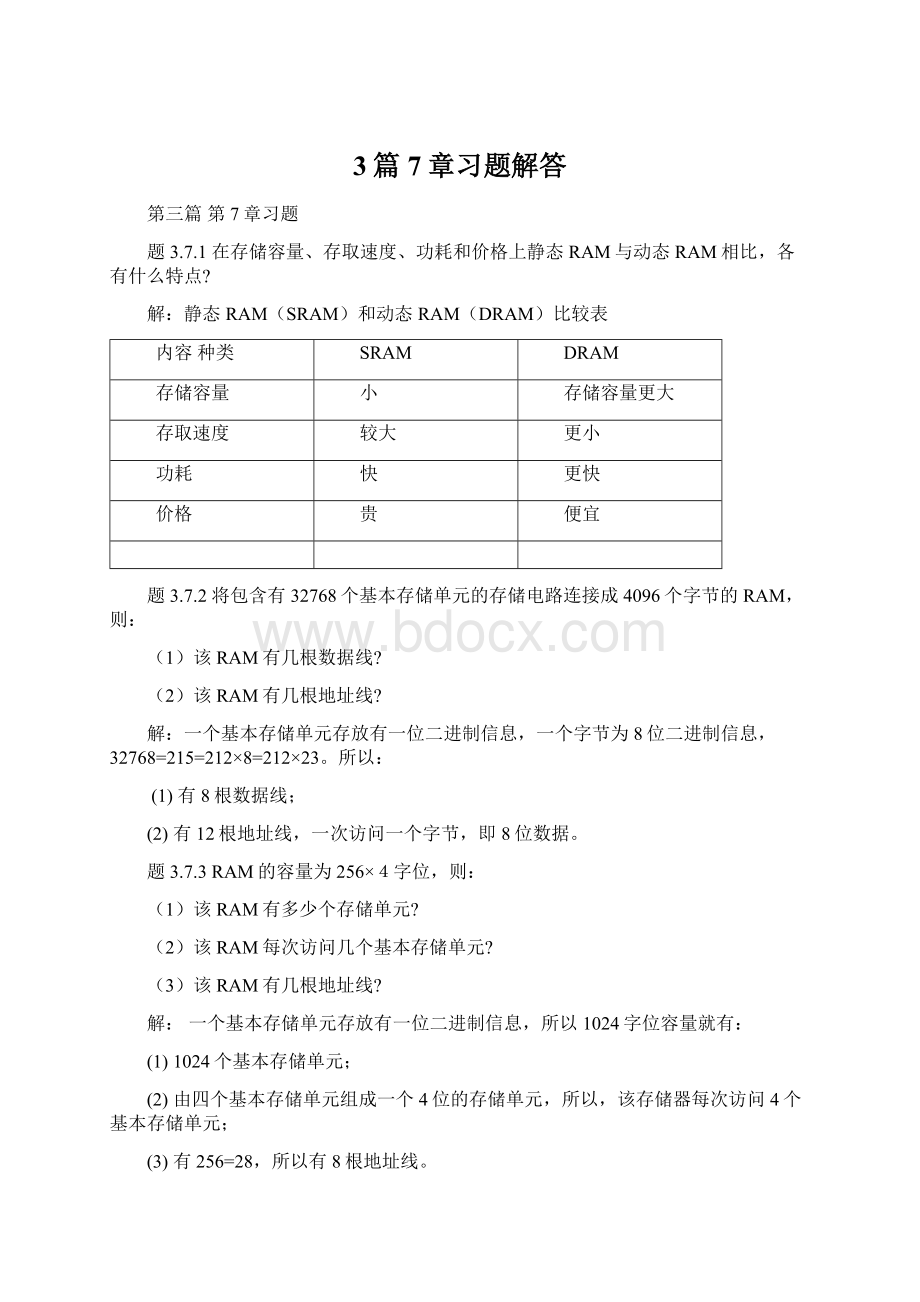

3篇7章习题解答文档格式.docx

- 文档编号:20828666

- 上传时间:2023-01-25

- 格式:DOCX

- 页数:16

- 大小:109.56KB

3篇7章习题解答文档格式.docx

《3篇7章习题解答文档格式.docx》由会员分享,可在线阅读,更多相关《3篇7章习题解答文档格式.docx(16页珍藏版)》请在冰豆网上搜索。

4字位的RAM只有4位数据线,要扩大成8位时应采用位扩展的方法实现。

将8位地址线、片选线、读/写控制线并联,RAM

(1)的4位作扩展后8位的高4位,RAM

(2)的4位作为扩展后的低4位,组成扩展后的8位数据输出。

其扩展的连接电路如图所示:

题3.7.5C850是64×

1字位容量的静态RAM,若要用它扩展成一个128×

4字位容量的RAM,需要几块C850?

并画出相应的电路图。

该题原地址为64=26为6位,现要有128=27,需用7位地址线,因此要用地址扩展;

数据线只有1位,现需要4位数据,同时要进行数据位扩展;

所以要有8块C850是64*1字位容量的静态RAM。

其连接后的电路如图所示:

题3.7.6按照编程工艺不同,只读存储器大致可分为哪几类?

各有什么特点?

熔丝/反熔丝型,EPROM型,E2PROM型,FlashMemory型等。

题3.7.7设某个只读存储器由16位地址构成,地址范围为000~FFF(16进制)。

现将它分为RAM、I/O、ROM1和ROM2等四段,且各段地址分配为RAM段:

000~DFFF;

I/O段:

E000~E7FF;

ROM1段:

F000~F7FF;

ROM2段:

F800~FFFF。

试:

(1)设16位地址标号为A15A14……A1A0,则各存储段内部仅有哪几位地址值保持不变?

(2)根据高位地址信号设计一个选择存储段的地址译码器。

(1)RAM存储段地址:

A15A14·

·

A1A0为0000000000000000-

110111*********1,所有的地址都变;

I/O存储段地址为

1110000000000000-111001*********1,只有A15A14A13A12A11=11100的地址不变;

ROM1存储段具体地址为1111000000000000-111101*********1只有A15A14A13A12A11=11110五位地址不变;

同理ROM2不变的地址为

A15A14A13A12A11=11111五位;

(2)因此,四个存储区的地址译码输出方程分别为:

画出相应的框图如下:

题3.7.8利用数据选择器和数据分配器的原理,将二只64×

8容量的ROM分别变换成一只512×

1字位和一只256×

2字位ROM。

变换成512×

1字位时用8选1的数选择器,变换成256×

2字位的系统时用

双4选1的数据选择器,它们的电路图分别如下:

题3.7.9有两块16KB(2048×

8)的ROM,试用它们构成:

(1)32KB(4096×

8)的ROM;

(2)32KB(2048×

16)的ROM。

(1)用二片16KB(2048*8)的ROM,加一个反相器即可实现32KB(4096*8)的ROM,连接图如图所示:

(2)该题只要进行数据位扩展即可,连接电路如图所示:

题3.7.10已知某8×

4位PROM的地址输入为A3、A2、A1、A0,数据输出为D3、D2、D1、D0,且对应地址中存放数据如题表2.5.10所示,试求出各数据输出关于地址输入的逻辑函数表达式。

题表3.7.10

0000

0011

1000

1011

0001

0100

1001

1100

0010

0101

1010

1101

0110

1110

0111

1111

D3=A3&

A2&

A1#A3&

A0#A3&

A2#A3&

A1&

A0;

D2=A2&

A0#A2&

A1#A2&

D1=A1&

A0#A1&

D0=A0;

题3.7.11试用PROM设计一个二位二进制数的乘法器。

设被乘数为A1、A0,乘数为B1、B0,乘积为P3、P2、P1、P0。

试问:

(1)PROM的容量应该为多少字位?

(2)画出PROM实现该乘法器的编程逻辑图。

(1)24×

4;

P3=A1&

A0&

B1&

B0;

(2)P2=A1&

B0#A1&

B1;

P1=A0&

P0=A0&

题3.7.12已知某逻辑电路如题3.7.12图所示,其中74LS161为一个四位二进制计数器,PROM中对应地址存放的数据如题表3.7.12所示,设计数器初态为“0000”,D=(D3D2D1D0)2,试:

`

(1)画出T=0~40秒内,输出数据D关于时间的变化波形。

(2)分析该电路实现了何种功能?

(3)若要用该电路实现一个近似的正弦波发生器,则PROM中的数据应如何存放

(4)若要改善波形的性能(如减少失真),电路应如何改造?

图题3.7.12

表题3.7.12

(1)波形图

(2)

(2)三角波发生器。

(3)只需对正弦波采样即可

(4)增加计数器的位数,同时增加PROM的数据位数

题3.7.13CPLD器件与FPGA器件相比,各有哪些特点?

它们分别适合设计何种类型的逻辑电路?

CPLD的基本逻辑块相对较大,布线延时可预测,资源利用率低。

适合设计复杂组合逻辑电路

FPGA的基本逻辑块较小,寄存器丰富,资源利用率高,布线延时不确定,特别适合大型时序逻辑电路的设计。

题3.7.14参考教材图3.7.25,试问单独用一个GLB最多可实现多少个逻辑变量的逻辑函数?

能否用它们实现这些变量组成的的所有逻辑函数?

由于一个GLB最多只有18个输入逻辑变量,故它最多可直接实现18个逻辑变量的逻辑电路。

由于其与或阵列,及其它硬件资源的限止,它并不能实现所有18个输入的逻辑函数。

题2.5.15试问四变量输入的逻辑函数发生器,需要多少个存储单元控制?

最多可产生多少个逻辑函数?

又可当作容量为多少字位的高速SARM?

相应的地址输入、数据输出是什么?

24个存储单元;

216种逻辑运算;

16(字)×

1(位)的SRAM。

题3.7.16现要设计一个模四的可逆二进制计数器,当输入X=0时,实现加法计数,X=1时,实现减法计数。

试画出描述该计数器的ASM流程图。

解:

(1)电路共有16个状态,可依次定义为S1~S16

根据外部输入X,可方便地画出其ASM图。

例,若当前状态为S3,若X=1,则下一状态转移至S2,若X=0,则下一个状态转移至S4。

题3.7.17现要设计一个“110”序列脉冲检测器,设输入序列为X,输出为Z。

试画出描述该序列脉冲检测器的ASM流程图。

定义如下状态

初始状态S0:

输入序列信号没有出现过“1”时的状态;

状态S1:

输入序列信号出现过一个“1”后的状态;

状态S2:

输入序列信号出现过连续两个“1”后的状态;

状态S3:

输入序列信号出现过连续两个“1”后,接着又出现“0”的状态,即出现了110序列信号。

ASM流程图如下:

题3.7.18(上机题)用VHDL语言描述一个能显示时、分、秒的数字钟电路,并要求时、分、秒可调。

不带时、分、秒可调功能的数字钟参考VHDL源文件

顶层VHDL代码:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYclockIS

PORT

(

g_clk,g_clr:

INSTD_LOGIC;

hh1_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

hh0_7bcd:

mm1_7bcd:

mm0_7bcd:

ss1_7bcd:

ss0_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0)

);

ENDclock;

ARCHITECTURErtlOFclockIS

COMPONENTcnt60

PORT(clk,clr,enable:

c60:

outSTD_LOGIC;

qh:

bufferSTD_LOGIC_VECTOR(2downto0);

ql:

bufferSTD_LOGIC_VECTOR(3downto0)

);

ENDCOMPONENT;

COMPONENTcnt24

PORT(clk,clr,enable:

bufferSTD_LOGIC_VECTOR(1downto0);

bufferSTD_LOGIC_VECTOR(3downto0)

COMPONENTBCDCODEn

PORT(d3,d2,d1,d0:

bcdcode:

OUTSTD_LOGIC_VECTOR(6downto0)

signalss_carry,mm_carry:

STD_LOGIC;

signalss1:

STD_LOGIC_VECTOR(2downto0);

signalss0:

STD_LOGIC_VECTOR(3downto0);

signalmm1:

signalmm0:

signalhh1:

STD_LOGIC_VECTOR(1downto0);

signalhh0:

BEGIN

second:

cnt60PORTMAP(clk=>

g_clk,clr=>

g_clr,enable=>

'

1'

c60=>

ss_carry,qh=>

ss1,ql=>

ss0);

minus:

ss_carry,clr=>

mm_carry,qh=>

mm1,ql=>

mm0);

hour:

cnt24PORTMAP(clk=>

mm_carry,clr=>

qh=>

hh1,ql=>

hh0);

hh1bcd:

BCDCODEnPORTMAP(d3=>

0'

d2=>

d1=>

hh1

(1),d0=>

hh1(0),bcdcode=>

hh1_7bcd);

hh0bcd:

hh0(3),d2=>

hh0

(2),d1=>

hh0

(1),d0=>

hh0(0),bcdcode=>

hh0_7bcd);

mm1bcd:

mm1

(2),d1=>

mm1

(1),d0=>

mm1(0),bcdcode=>

mm1_7bcd);

mm0bcd:

mm0(3),d2=>

mm0

(2),d1=>

mm0

(1),d0=>

mm0(0),bcdcode=>

mm0_7bcd);

ss1bcd:

ss1

(2),d1=>

ss1

(1),d0=>

ss1(0),bcdcode=>

ss1_7bcd);

ss0bcd:

ss0(3),d2=>

ss0

(2),d1=>

ss0

(1),d0=>

ss0(0),bcdcode=>

ss0_7bcd);

ENDrtl;

60进制计数器VHDL源文件:

ENTITYcnt60IS

clk,clr,enable:

c60:

qh:

ql:

ENDcnt60;

ARCHITECTURErtlOFcnt60IS

COMPONENTcnt10a

PORT(clk,clr,ena:

q:

outSTD_LOGIC_VECTOR(3downto0));

COMPONENTcnt6a

outSTD_LOGIC_VECTOR(2downto0));

signalen:

cnt10:

cnt10aPORTMAP(clk,clr,enable,ql);

en<

=ql(0)andql(3)andenable;

cnt6:

cnt6aPORTMAP(clk,clr,en,qh);

c60<

=ql(0)andql(3)andqh(0)andqh

(2);

24进制计数器VHDL源文件:

ENTITYcnt24IS

ENDcnt24;

ARCHITECTURErtlOFcnt24IS

COMPONENTcnt4a

outSTD_LOGIC_VECTOR(1downto0));

signalen,clear:

clear<

=clror(qh

(1)andql

(2));

cnt10aPORTMAP(clk,clear,enable,ql);

cnt4:

cnt4aPORTMAP(clk,clear,en,qh);

BCD编码VHDL源文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYBCDCODEnIS

d3,d2,d1,d0:

ENDBCDCODEn;

ARCHITECTUREbehaveOFBCDCODEnIS

signaltmp:

STD_LOGIC_VECTOR(3downto0);

tmp<

=d3&

d2&

d1&

d0;

PROCESS(d3,d2,d1,d0)

BEGIN

CASEtmpIS

WHEN"

0000"

=>

bcdcode<

="

0000001"

;

WHEN"

0001"

1001111"

0010"

0010010"

0011"

0000110"

0100"

1001100"

0101"

0100100"

0110"

0100000"

0111"

0001111"

1000"

0000000"

1001"

0000100"

WHENOTHERS=>

1111111"

ENDCASE;

ENDPROCESS;

ENDbehave;

10进制计数器VHDL源文件:

ENTITYcnt10aIS

clk,clr,ena:

q:

outSTD_LOGIC_VECTOR(3downto0)

ENDcnt10a;

ARCHITECTUREbehaveOFcnt10aIS

signaltmp:

PROCESS(clk,clr)

IFclr='

THEN

tmp<

="

ELSIF(clk'

EVENTANDclk='

)THEN

IFena='

THEN

IF(tmp="

)THENtmp<

ELSEtmp<

=tmp+'

ENDIF;

ENDIF;

q<

=tmp;

6进制计数器VHDL源文件:

ENTITYcnt6aIS

outSTD_LOGIC_VECTOR(2downto0)

ENDcnt6a;

ARCHITECTUREbehaveOFcnt6aIS

STD_LOGIC_VECTOR(2downto0);

000"

ifena='

then

if(tmp="

101"

)thentmp<

elsetmp<

endif;

endif;

4进制计数器VHDL源文件:

E

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 习题 解答

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx

县级党政机关办公用房总台帐.xls

县级党政机关办公用房总台帐.xls