数电课设大作业数字钟Word格式.docx

数电课设大作业数字钟Word格式.docx

- 文档编号:20765319

- 上传时间:2023-01-25

- 格式:DOCX

- 页数:16

- 大小:106.08KB

数电课设大作业数字钟Word格式.docx

《数电课设大作业数字钟Word格式.docx》由会员分享,可在线阅读,更多相关《数电课设大作业数字钟Word格式.docx(16页珍藏版)》请在冰豆网上搜索。

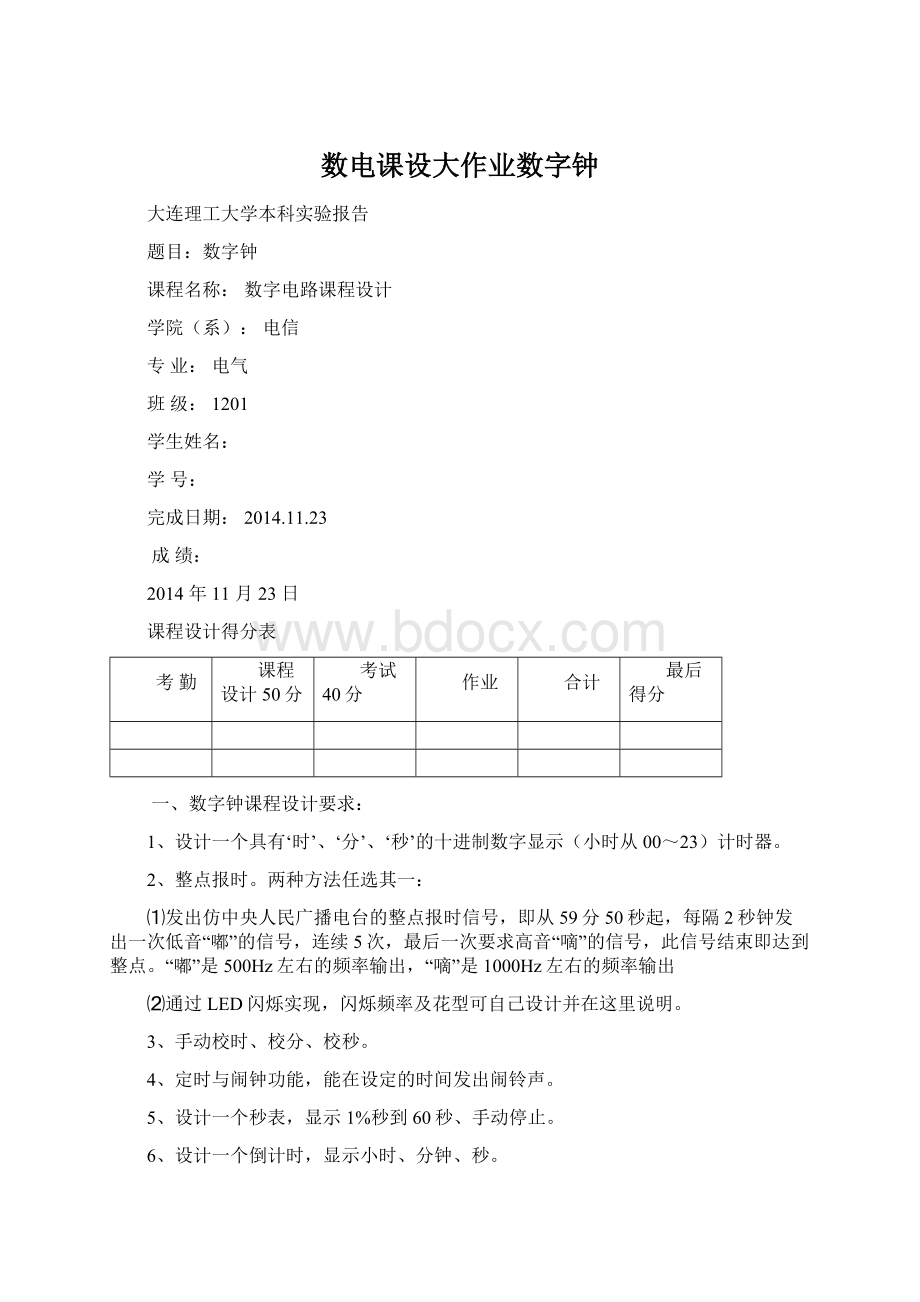

第1题25分,其他每题5分

二、课程设计考试(40分,每题分):

考试题目:

1、实体名□

2、计数器□

3、异步清零□

4、进位输出□

5、仿真图□

6、数码管输出□

7、分频□

8、元件例化□

9、引脚分配□

10、下载□

(1.大连理工大学电信学院,辽宁大连,116023;

2.大连理工大学电工电子实验中心,辽宁大连,116023;

)

1.设计要求

一、电子表部分:

(1)由晶振电路产生1HZ的校准秒信号。

?

(2)设计一个具有‘时’、‘分’、‘秒’的十进制数字显示(小时从00~23)计时器具有手动校时、校分,校秒和清零的功能。

(3)整点报时功能,通过LED闪烁实现,此实验LED灯亮一秒。

二、秒表部分:

(1)有晶振产生100HZ的校准0.01秒信号。

(2)设计一个有“时”、“分”、“秒”、“0.1秒”、“0.01秒”(23小时59分59秒99)显示功能

(3)具有开始计时暂停计时功能和清零功能

三、具有电子表和秒表状态切换。

四、划出框图和逻辑电路图,写出设计。

2.设计分析及系统方案设计

1设计主要分为数字钟和秒表计时两个部分并选择用二选一数据选择器来实现两种功能切换。

2由于时钟用的是cyclone2开发板上提供的50MHz晶振的频率,所以数字时钟和秒表计时都用到分频器分频分别得到1Hz和100Hz的时钟频率。

3数字时钟部分包括分频部分即分频器;

计时部分,包含模六计数器、模十计数器;

选位调节部分,分别对时钟分钟和小时部分进行调节,用二选一数据选择器实现;

数字显示部分,用到6个4-16译码器,和6个数码显示管;

整点报时部分,其中报时用LED灯闪烁代替;

含有清零端开关。

4秒表计时包含分频器;

计时器包含模六计数器,模十计数器,模三计数器;

数字显示器包含有8个4-16译码器,8个数码显示管;

计时启停开关,清零开关。

3.系统以及模块硬件电路设计

输入:

晶振50MHz,选位开关(0为可调节,1为正常计时),数字钟清零开关(0为清零),开关切换计时状态(1为数字计时,0为秒表计时),秒表启停开关(1启动,0停止),秒表复位开关(0复位),选择输出开关(1输出数字计时数字,0输出秒表计时数字)。

输出:

LED灯,数字显示部分。

整点计时

4系统的VHDL设计

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitykesheis

port(clk:

instd_logic;

qo1,qo2,qo3,qo4,qo5,qo6,qo7,qo8:

outstd_logic_vector(6downto0);

rst1:

--开关1

rst2:

--开关2

rst3:

--开关3

rst4:

--开关4

switch1:

switch2:

key1:

--分钟调节

key2:

--小时调节

key3:

runstop:

--秒表启停开关

led:

outstd_logic_vector(7downto0)

);

end;

architectureaofkesheis

signalqh,ql,qhs,qls,qhf,qlf,qhh,qlh:

std_logic_vector(3downto0):

="

0000"

;

signalrun:

std_logic:

='

0'

signalcnt,ct:

integer

signalqqh1,qqh2,qql1,qql2,qqhf1,qqhf2,qqhs1,qqhs2,qqls1,qqls2,qqhh1,

qqhh2,qqlh1,qqlh2,qqlf1,qqlf2:

std_logic_vector(3downto0);

signalclk1s,csf,csh,css,clk1s2,csf2,csh2,css2,csh2in,csf2in,css2in:

std_logic;

componentsegment

port(qi:

instd_logic_vector(3downto0);

qo:

outstd_logic_vector(6downto0)

endcomponent;

begin

u1:

segmentportmap(qh,qo1);

u2:

segmentportmap(ql,qo2);

u3:

segmentportmap(qhf,qo5);

u4:

segmentportmap(qlf,qo6);

u5:

segmentportmap(qhh,qo7);

u6:

segmentportmap(qlh,qo8);

u7:

segmentportmap(qhs,qo3);

u8:

segmentportmap(qls,qo4);

process(rst1,qqh1,qqh2,qql1,qql2,qqhf1,qqhf2,qqhs1,qqhs2,qqls1,qqls2,qqhh1,qqhh2,qqlh1,qqlh2,qqlf1,qqlf2)--电子表秒表切换

begin

ifrst1='

1'

then

qh<

=qqh1;

qhs<

=qqhs1;

qhf<

=qqhf1;

qhh<

=qqhh1;

ql<

=qql1;

qls<

=qqls1;

qlf<

=qqlf1;

qlh<

=qqlh1;

else

=qqh2;

qhs<

=qqhs2;

=qqhf2;

=qqhh2;

=qql2;

qls<

=qqls2;

=qqlf2;

=qqlh2;

endif;

endprocess;

process(runstop,rst2)--秒表计停开关

ifrst2='

run<

elsifrunstop'

eventandrunstop='

=notrun;

endprocess;

process(clk,clk1s,rst2,run)

ifrising_edge(clk)then

ifcnt=499999then

cnt<

=0;

clk1s<

elsecnt<

=cnt+1;

clk1s<

qql1<

qqh1<

elsifrun='

ifclk1s'

eventandclk1s='

if(qql1="

1001"

andqqh1="

)then

css<

;

elseifqql1="

=qqh1+1;

=qql1+1;

process(css,rst2)

ifrst2='

qqls1<

qqhs1<

if

css'

eventandcss='

if(qqls1="

andqqhs1="

0101"

csf<

elseifqqls1="

=qqhs1+1;

=qqls1+1;

endif;

process(csf,rst2)

qqlf1<

qqhf1<

csf'

eventandcsf='

if(qqlf1="

0011"

andqqhf1="

0010"

csh<

elseifqqlf1="

=qqhf1+1;

=qqlf1+1;

process(csh,rst2)

qqlh1<

qqhh1<

csh'

eventandcsh='

if(qqlh1="

andqqhh1="

elseifqqlh1="

=qqhh1+1;

=qqlh1+1;

process(clk,clk1s2,rst3)

ifct=499999then

ct<

clk1s2<

elsect<

=ct+1;

clk1s2<

ifrst3='

qql2<

qqh2<

elsifclk1s2'

eventandclk1s2='

if(qql2="

andqqh2="

css2<

elseifqql2="

=qqh2+1;

=qql2+1;

process(css2,rst4,key3)

ifrst4='

css2in<

=css2;

=key3;

process(css2in,rst3)

ifrst3='

qqls2<

qqhs2<

elsifcss2in'

eventandcss2in='

if(qqls2="

andqqhs2="

csf2<

elseifqqls2="

=qqhs2+1;

=qqls2+1;

process(csf2,switch1,key1)

ifswitch1='

csf2in<

=csf2;

=key1;

process(csf2in,rst3)

qqlf2<

qqhf2<

elsif

csf2in'

eventandcsf2in='

if(qqlf2="

andqqhf2="

csh2<

elseifqqlf2="

=qqhf2+1;

=qqlf2+1;

if(qqlf2="

andqqls2="

)then

led

elseled<

00000000"

process(csh2,switch2,key2)

ifswitch2='

csh2in<

=csh2;

=key2;

process(csh2in,rst3)

qqlh2<

qqhh2<

csh2in'

eventandcsh2in='

if(qqlh2="

andqqhh2="

elseifqqlh2="

=qqhh2+1;

=qqlh2+1;

entitysegmentis

port(

qi:

architecturebofsegmentis

process(qi)

begin

caseqiis

when"

=>

qo<

1000000"

0001"

1111001"

0100100"

0110000"

0100"

0011001"

0010010"

0110"

0000010"

0111"

1111000"

1000"

0000000"

0010000"

whenothers=>

1111111"

endcase;

1分频部分

新时钟状态图如下:

2秒表电子表输出切换部分

开关判断为1时输出为数字计时输出,为0时输出为秒表计时输出。

3计时部分

模6计数器、模10计数器、模3计数器

状态转换如下:

4数字显示部分

数字显示用4-16译码器中7个输出管脚连接数码管中7个共阳的发光二极管,当译码器输入四位二进制代码时,对应数码管显示相应的数字。

"

对应"

显示0;

显示1;

显示2;

显示3;

显示4;

显示5;

显示6;

显示7;

显示8;

others对应"

显示9;

5结论以及结果说明

本次课程设计主要在windowsXP系统运用quartus26.0版软件来进行调试。

部分仿真截图

通过本课学习到了VHDL的使用方法了解到了自己在学习上的一些不足,谢谢老师的指导。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数电课设大 作业 数字

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx