数字电子技术随堂练习Word下载.docx

数字电子技术随堂练习Word下载.docx

- 文档编号:20688474

- 上传时间:2023-01-25

- 格式:DOCX

- 页数:15

- 大小:781.07KB

数字电子技术随堂练习Word下载.docx

《数字电子技术随堂练习Word下载.docx》由会员分享,可在线阅读,更多相关《数字电子技术随堂练习Word下载.docx(15页珍藏版)》请在冰豆网上搜索。

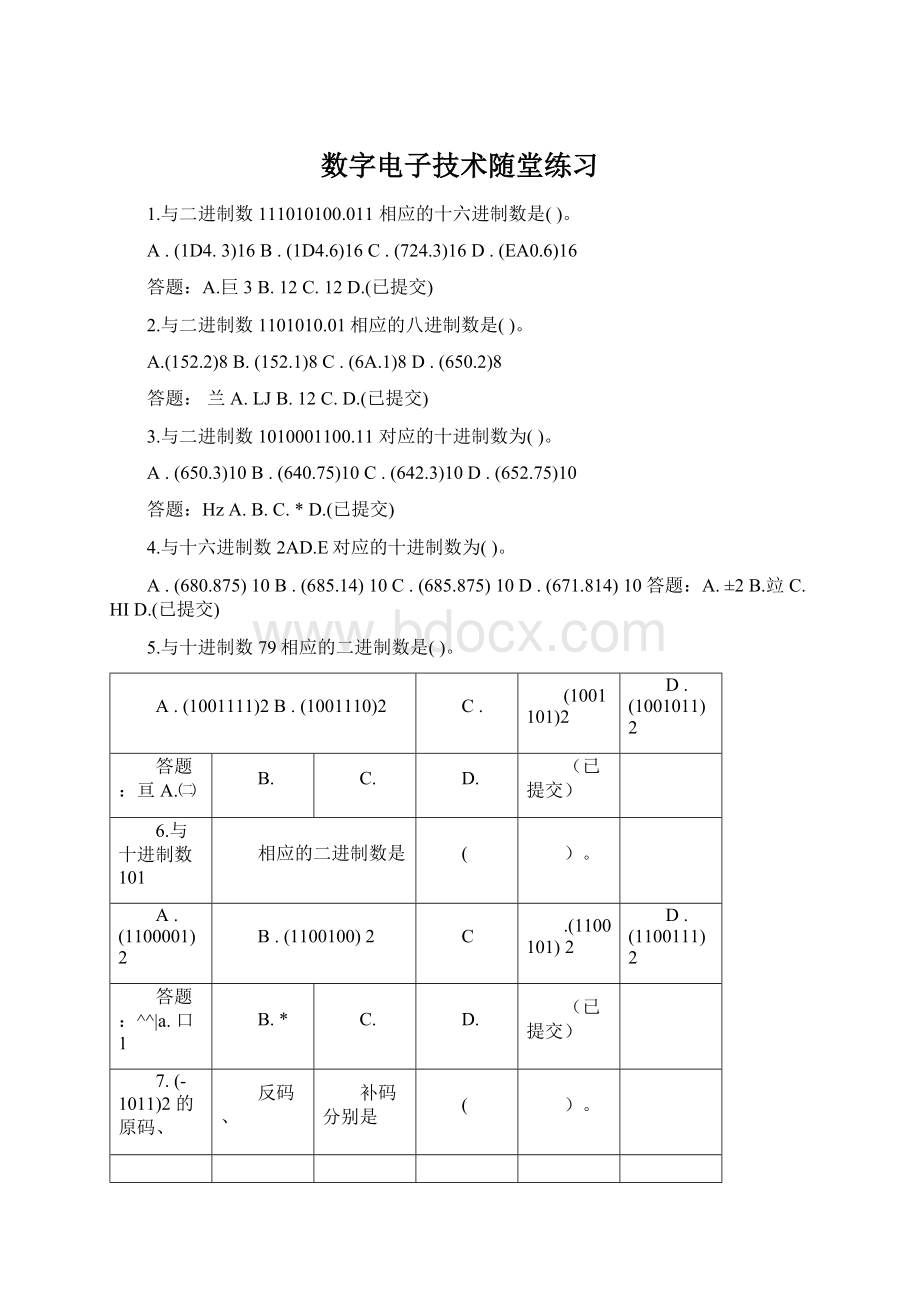

B.*

7.(-1011)2的原码、

反码、

补码分别是

A.11011、00100、00101B.11011、10100、10101

C.01011、00100、00101D.01011、10100、10101

A.E3B.C.D.(已提交)

8.采用二进制补码运算,(-1011-1001)的运算结果,其补码、原码分别为()

A.101100010100B.001100110100

C.0011000110100D.101100110100

A.凸B.C.*D.(已提交)

9.5421BCD码中表示十进制数9的编码为()。

A.1010B.1001C.1100D.1101

A.口B.*C.D.(已提交)

10.8421BCD码中表示十进制数9的编码为()。

1.函数式Y=AB+A'

BD+CD的对偶式为()

A孑心三(公斗哥(月+房4疔)(0+0)B『即二(丄+劉)(£

+£

+。

)(0+口)

C尸0三(」+占了(才+昌4门)(0+/)丫D^©

^(才屮和工卫亠扩+心丁^+门)'

2.运用反演定理写出函数Y=A'

D'

+A'

B'

C+ACD+CD的反函数Y为()。

A厂=(占+DJ(百+^+C)(A^Uf+D](C+

B厂=(占+Dy(才+F+a)XA+0+DY9+卩丫

rr=(/+Dy(A+h+C73+(?

+z/yc+DyC.

D广=(川+D){A+B+7)(却+C+Df)(Cr+D)

3.

函数Y(A,B,C)=A'

BC+AC+B'

的最小项之和的形式为(

AC)=ABC+占月匸^r^BC^ABC+A3C+ASCf

『(4民(7)=虫矽+占少C+』专旷+的C+/丘C+占月7

rF(A出Q=A^C14--F+ABC+ABfC+ABC1

DY甘Q=+ABC+4船+朋。

+ABV+A^C

4.函数耳二曲衣十月。

十虫°

转换成与非—与非式为()。

A尺=(吗+(加7+(吗

B”=((43)「+(就:

7+(2匚)丁

C,((砂(昭(吗丁C.

Df二⑷)

5.

函数F=A'

+AB转换成或非—或非式为(

A.F=(((AB)'

+(A'

)'

F=((AB)'

F=((A+B)'

+B'

6.某逻辑电路的状态表如图2-1所示,其输入变量为A,B,C,输出为F,则F的逻辑式为()。

A.F=A'

C+ABC

B.F=A'

BC'

+ABC

C.F=A'

C'

D.F=AB'

哉

B

F

11

(J

]

J

1

01

D

\

t

图2-1

7.函数昙CD)的卡诺图如图2-2所示,其最简与或”表达式为()。

图2-2

OA.B.*C.D.(已提交)

1.图3-1(a)、(b八(c八(d)中74系列TTL门电路的输出状态为低电平的是()

A.Y1B.Y2C.Y3D.Y4

(a)(b)(c)(d)

图3-1

A.ClB.囲c.OD.(已提交)

2.图3-2(a)、(b八(c八(d)中74HC系列CMOS门电路的输出状态为低电平的是()

5Lka

图3-2

眞A.CB.C.dD.(已提交)

3.TTL或非门多余的输入端在使用时()。

A.应该接高电平1B.应该接低电平0

C.可以接高电平1也可以接低电平0D.可以与其它有用端并联也可以悬空

打A.*B.I打C.D.(已提交)

4.CMOS与非门多余的输入端在使用时()。

A.应该接高电平1B.可以接低电平0也可以接高电平1

C.应该接低电平0D.可以与其它有用端并联也可以通过一个51W的电阻接地

A.EB.L:

lC.3D.(已提交)

5.和CMOS电路相比,TTL电路最突出的优势在于()。

A.可靠性高B.抗干扰能力强C.速度快D.功耗低

巨A.丄B.AC.3d.(已提交)

6.和TTL电路相比,CMOS电路最突出的优势在于()。

口A.*B.°

C.二D.(已提交)

7.在TTL门电路中,能实现线与”逻辑功能的门为()。

口A.*B.LJC.D.(已提交)

8.在CMOS门电路中,三态输出门、OD门、与非门、异或门和非门中,能实现线与”逻辑功能的门为()

A.OD门B.三态门C.或非门D.异或门

阿a.cib.inc.nD.(已提交)

9.门电路中,能实现总线连接方式的门为()。

A.OD门B.OC门C.或非门D.三态门

□A.UB.口C.!

-■!

D.(已提交)

10.欲使漏极开路的CMOS门电路实现线与”则其输出端应该()。

A•并联B•并联且外接上拉电阻和电源

C•外接上拉电阻和电源但不需并联D•无需并联也无需外接上拉电阻和电源

二A.同B.二C.UD.(已提交)

11.三态输出的门电路其输出端()。

A•可以并联且实现线与”B•不能并联也不能实现线与”

C•可以并联但不能实现线与”D•无需并联但可以实现线与”

二IA.L-3B.凶C.也D.(已提交)

12.图3-3中由74系列TTL与非门组成的电路中,门G输出高电平/低电平时流出其输出端的电流分别为

()。

已知与非门的输入电流为IIL=-1.6mA,IIH=40uA。

图3-3

A.3IIH、3IILB.3IIH、6IILC.6IIH、3IILD.6IIH、6IIL答题:

CA.Clb.@1C.dD.(已提交)

13.图3-4中由74系列TTL或非门组成的电路中,门G输出高电平/低电平时流出其输出端的电流分别为()。

已知或非门的输入电流为IIL=-1.6mA,IIH=40uA。

图3-4

A.3IIH、3IILB.6IIH、6IILC.3IIH、6IILD.6IIH、3IIL

行A.何1B.IQC.C|D.(已提交)

14.某集成电路芯片,查手册知其最大输出低电平VOL(max)=0.5V,最大输入低电平VIL(max)=0.8V,最小输出高电平VOH(min)=2.7V,最小输入高电平VIH(min)=2.0V,则其低电平噪声容限VNL等于()。

A.0.4VB.0.6VC.0.3VD.1.2V

门A.Ob.傀IC.nD.(已提交)

1.图4-1中Y的逻辑函数式为()。

Ay=(ABcy

2.用3线-8线译码器74HC138设计的逻辑电路如图4-2所示,74HC138的功能表如图4-3所示。

、则输岀丫3、Y2、丫1、Y0的函数式分别为()。

a抡田/©

=2>(4:

67)6=2沁3&

T)

A.、、

gBC)=》>(卩£

7)h(AgC)二工>(0』2戈4二67)

D二昱r2(^^C)=2W,3A7)

B.、

C.、

gg=迟帙(口57〕FjaEQ=为诫

D§

(耳尻丘丽)、与(具00)二工>言36了)

幷(具56二乞皿(13戸工!

、托d®

二乞皿(0丄234)6/7)

图4-2图4-3

二A.dB.对C.JD.(已提交)

3.用8选1数据选择器74LS152设计的逻辑电路如图4-4所示,74LS152的功能表如图4-5所示。

则其输岀F的函数式为()。

A.巩/也扎旳二住屈蛮+浓膵+翠少+&

恥AQE傀5爭

C.巩片凤乂珀二閘川+£

鼠風AZ+S風£

+$%样

CI.

^1-."

.■-■■:

=T:

「m—1「

图4-4图4-5

答题:

aHB.•

D.(已提交)

1.触发器输岀的状态取决于()。

A.输入信号B•电路的初始状态

C.时钟信号D•输入信号和电路的原始状态

A.口B.归C.*D.(已提交)

2.假设JK触发器的现态Q=0,要求次态Q*=0,则应使()

A•J=X,K=0B.J=0,K=X

C.J=1,K=XD.J=K=1

A.PIB.OC.D.(已提交)

3.T触发器的功能是()。

A•翻转、置“0”B.保持、置“1”

C•置“、置“0”D•翻转、保持

二A.口B.炒C.D.(已提交)

4.在时钟脉冲作用下,图5-1所示电路的功能是()。

CLK一

A•具有计数功能B•保持原状态C•置“0”•[置“1”

HA.

B.同C.-

*

A.

B.讨C.

7.设图5-4所示电路的初态Q1Q2=00,试问加入3个时钟正脉冲后,电路的状态将变为()。

图5-4

A.00B.01C.10D.11

1.逻辑电路如图6-1所示,该电路的功能为()。

A•不能自启动同步五进制加法计数器B•可自启动异步五进制加法计数器

图6-1

E3A.二B.二C.区D.(已提交)

2.由同步十进制计数器74LS160和门电路组成的计数器电路如图6-2所示。

74LS160的功能

表如图6-3所示。

该电路的功能为()。

A.8进制减法计数器B.8进制加法计数器

C.9进制减法计数器D.9进制加法计数器

74LS1^0W功能表

A.11进制加法计数器B.11进制减法计数器

C.10进制加法计数器D.10进制减法计数器

图6-4图6-5

1.数据通过()存储在存储器中。

A.读操作B.启动操作

C.写操作D.寻址操作

EJA.二B.畠C.D.(已提交)

2.下列说法不正确的是()。

A.半导体存储器的基本结构都是由地址译码器、存储矩阵和读写控制电路三大部分构成

B.ROM的主要特点是在工作电源下可以随机地写入或读岀数据

C•静态RAM存储单元的主体是由一对具有互为反馈的倒相器组成的双稳态电路

D•动态RAM存储单元的结构比静态RAM存储单元的结构简单

CA.庐B.QC.GD.(已提交)

3.若存储器容量为512KX8位,则地址代码应取()位。

A.17B.18C.19D.20

'

A.'

B."

C.「D.(已提交)

4.一片256KX4的ROM,它的存储单元数和数据线数分别为()。

A.2"

个,4条B.2耳个,18条

C.2个,4条D.2"

个,18条

A.鋼

B.@

c.r

5.快闪存储器属于(

)器件。

A•掩模ROMB•

可擦写

ROM

C•

动态RAMD•静态RAM

頁A.“

B.厂

C.厂

A•通用性强

C•可靠性好

B•其逻辑功能可以由用户编程设定

D•集成度高

1.可编程逻辑器件的基本特征在于()

昱D.(已提交)

巨A.

C•开发软件D•专用的编程语言

3.3、PAL器件与阵列、或阵列的特点分别为()。

A.固定、可编程B.可编程、可编程C.固定、固定D.可编程、固定

Ea.口b.匚C.塑D.(已提交)

4.4、产品研制过程中需要不断修改的中、小规模逻辑电路中选用(B)最为合适

A•PALB•GALC.EPLDD.FPGA

A.匡Ib.・C.D.(已提交)

)进行编

5、通用阵列逻辑GAL器件的通用性,是指其输岀电路的工作模式,可通过对(程实现。

A•输岀逻辑宏单元OLMCB•与门阵列

C•或门阵列D•与门阵列和或门阵列

E2A.2B.C.D.(已提交)

6.6、图8-1所示电路是PAL的一种异或输岀结构,其输岀丫的最小项之和表达式为()

图8-1

A.£

豹36912)B.£

懣05912)

2^6,9,13)D.X6&

12)

1.自动产生矩形波脉冲信号的是()。

A•施密特触发器B•单稳态触发器

C•T触发器D•多谐振荡器’

HA.'

B.QC.①D.(已提交)

2.将三角波变换为矩形波,需选用()。

A•单稳态触发器B•施密特触发器C.微分电路D•双稳态触发器

A.P'

lB.1/1C.D.(已提交)

3.单稳态触发器输岀脉冲的宽度取决于()。

A•触发脉冲的宽度B•触发脉冲的幅度

C.电源电压的数值D.电路本身的电阻、电容参数

HIa.UB.C.*D.(已提交)

4.为了提高对称式多谐振荡器振荡频率的稳定性,最有效的方法是()

A•提高电阻、电容的精度B•提高电源的稳定度

C•接入石英晶体D•保持环境温度不变

A.°

B.*C.D.(已提交)

5.欲得到一个频率高度稳定的矩形波,应采用()。

A.计数器B.单稳态触发器C.石英晶体多谐振荡器D.施密特触发器

A.RB.翅C.打D.(已提交)

6.多谐振荡器与单稳态触发器的区别之一是()。

A•前者有2个稳态,后者只有1个稳态

B•前者没有稳态,后者有2个稳态

C•前者没有稳态,后者只有1个稳态

D•两者均只有1个稳态,但后者的稳态需要一定的外界信号维持

匸:

A.B.*C.LJD.(已提交)

1.8位D/A转换器当输入数字量只有最低位为1时,输出电压为0.02V,若输入数字量为01001100时,

其输岀电压为()。

A.0.76VB.3.04VC.1.40VD.1.52V

EJA.二B.EJC.二D.(已提交)

2.某DAC的分辨率约为其满量程的0.4%,则它是一个()。

A.8位转换器B.10位转换器C.12位转换器D.16位转换器

旦A.wk.EJC.-ID.(已提交)

3.D/A转换器的主要参数有()、转换精度和转换速度。

A.分辨率B.输入电阻C.输出电阻D.参考电压

EJA.三B.CJC.二3D.(已提交)

4.以下()不是造成D/A转换器转换误差的主要因素。

A.基准电压VREF的波动B.放大器的零点漂移

C•放大器的电源电压D•电子开关的导通电阻和压降

口IA.EB.习C.^]|||d.(已提交)

5.各种A/D转换器电路中转换速度最快的是()。

A•并联比较型B•逐次渐近型C•双积分型D•计数型

E3A.二B.E3C.暑D.(已提交)

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子技术 练习

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx