浙江大学单片微型计算机与接口技术复习要点Word格式.docx

浙江大学单片微型计算机与接口技术复习要点Word格式.docx

- 文档编号:20581323

- 上传时间:2023-01-24

- 格式:DOCX

- 页数:13

- 大小:2.18MB

浙江大学单片微型计算机与接口技术复习要点Word格式.docx

《浙江大学单片微型计算机与接口技术复习要点Word格式.docx》由会员分享,可在线阅读,更多相关《浙江大学单片微型计算机与接口技术复习要点Word格式.docx(13页珍藏版)》请在冰豆网上搜索。

10.AE?

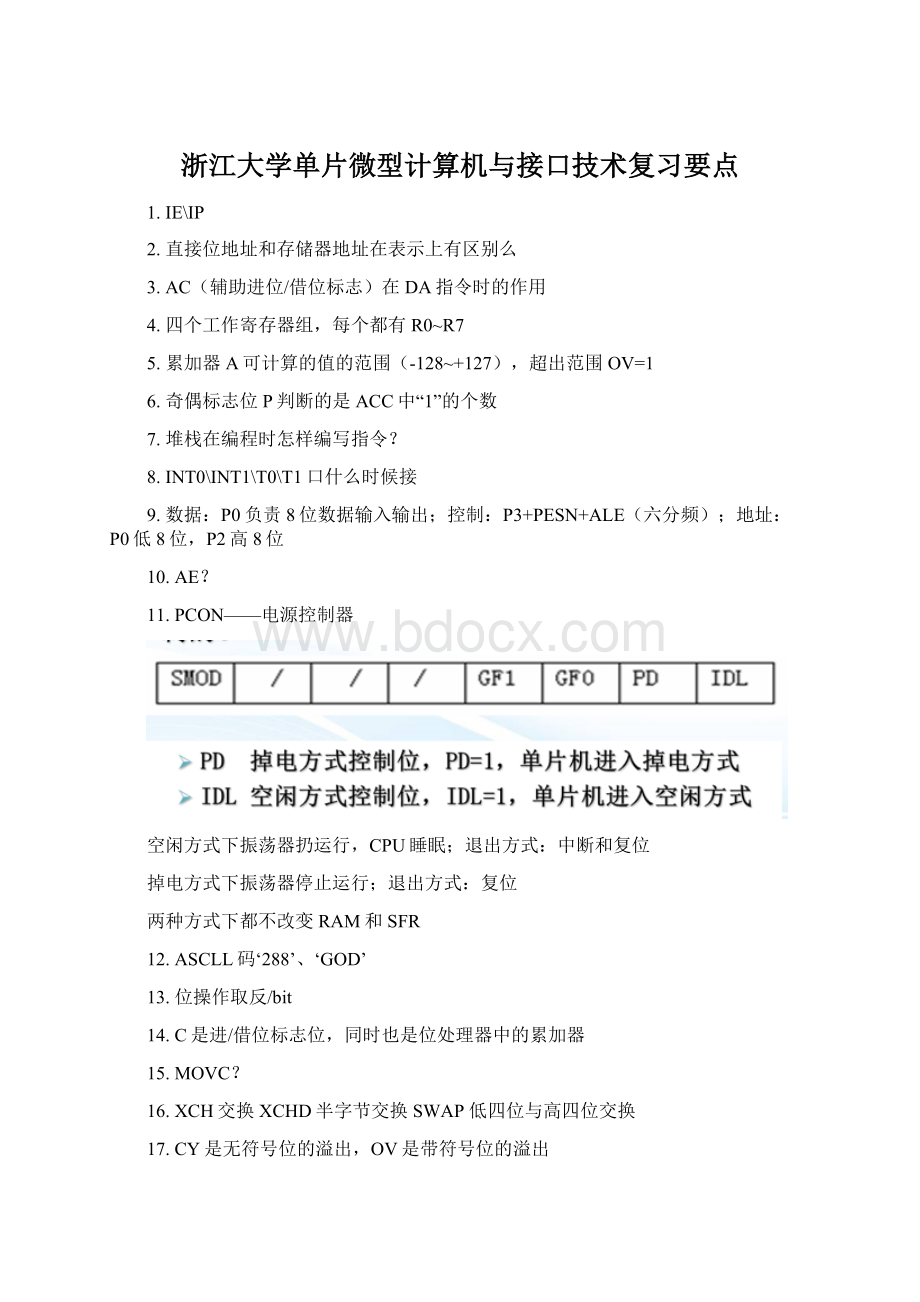

11.PCON——电源控制器

空闲方式下振荡器扔运行,CPU睡眠;

退出方式:

中断和复位

掉电方式下振荡器停止运行;

复位

两种方式下都不改变RAM和SFR

12.ASCLL码‘288’、‘GOD’

13.位操作取反/bit

14.C是进/借位标志位,同时也是位处理器中的累加器

15.MOVC?

16.XCH交换XCHD半字节交换SWAP低四位与高四位交换

17.CY是无符号位的溢出,OV是带符号位的溢出

18.MULAB8位无符号数相乘,高8位在B,低8位在A

?

19.DIVAB8位无符号数A除以B,A存商,B存余数B为00H时OV置1

20.DAA指令对CY和AC都有影响?

21.AJMPLJMP和SJMP区别?

22.十进制数与16进制数进行计算后就变成了16进制数?

23.ACALL与LCALL是否用LCALL就是万无一失了?

24.PUSH地址,SP自动+1?

25.PC+1/2/3如何判断?

26.PC指向的地址存入堆栈先存第八位再存高八位

27.ANLC,bit(CY)的值为C与bit中最低为相与的结果

28.JBCbit,rel(bit)=1时跳转,并将该为清零(bit)←0

29.DB53H,0B4H,’1’,’2’

30.Rn中的数送A:

XCHA,Rn

31.

32.50ms延迟程序:

33.堆栈PUSH\POP会对A产生影响么?

这个程序为什么非要用堆栈?

34.0~9的ASCLL码+30HA~F的ASCLL码+37H

35.16进制转10进制,MOVB,#100(#10);

DIVAB;

SWAPA;

ORLA,B

36.10进制转16进制,MOVB,#10H;

MOVR4,B;

MOVB,#10;

MULAB

37.INT0非/INT1非输入信号,IT0/IT1选择是低电平有效还是下降沿有效。

CPU检测到P3.2/P3.3引脚出现有效中断信号时,中断标志IE0/IE1置1,向CPU申请中断

38.TF0/TF1片内定时器/计数器T0/T1溢出中断请求标志。

溢出时置位

39.RI(SCON.0)或TI(SCON.1)串行口中断请求标志,满足要求置位

40.

41.

42.中断允许控制

43.中断优先控制

44.计时/计数器

45.要实现中断响应优先级,除了中断本身的INT0>

T0>

INT1>

T1,在同一个中断响应标志中,可以通过

JBbit.0,DV1

JBbit.1,DV2

…

实现DV1>

DV2>

….

46.TMOD与TCON的关系

GATE=1时,INT0非/INT1非引脚上电平为1才行

47.T0/T1做计数器(C/T=1时),计数范围为2^N

48.

49.串行控制SCON

50.TI发送完成(SBUF中的数据没有全部发出)前软件清零,发送完毕自动置1

.RI接收完成(数据没有全部进入SBUF)前软件清零,发送完毕自动置1

51.SMOD(PCON.7)

52.串口工作方式0用于扩展并行输入/输出口

RXD(P3.0)用于数据输入/输出,TXD(P3.1)作为时钟脉冲的输出端

53.串口方式1波特率的设定

54.串口方式1设置

55.

56.SCON中的SM2为多机控制位

57.C51串口工作,数据接收缓冲寄存器之前设置了一个移位寄存器,从而构成了串行接收的双缓冲结构

58.多机通信过程

59.串口波特率计算总结

60.T1以方式2作为波特率发生器

61.双机通信(A发送,B接收):

i)A发送E1信号,B反馈E2信号说明同意接收。

ii)A发送的同时不断更新“校验和”;

B发送的同时也不断更新“校验和”,并且两机发送地址和接收数据缓存地址相同(如40H)

iii)一个数据块发送完毕后,B将其得到的“校验和”与A发送来的“校验和”比较。

若相同,B回答00H,A机结束发送;

若不相同,B回答0FFH,A重新发送

62.若主机发送的数据TB为1,说明发送的是地址帧,在从机中找到相同地址的从机进行通信;

若主机发送的TB为0,说明是数据帧。

(存疑)?

63.一般ALE的下降沿或低电平锁存P0口输出的地址A0~A7

64.并行扩展唯一地选择片外某一存储单元或I/O端口,需要进行两次选择。

一是“片选”,二是“字选”。

65.3/8译码器,P2.7P2.6P2.5输入,输出对应A15A14A13,每个芯片的字选线从A12~A0共13根,可能的最大容量为2^13

66.EA非=0时,只访问外部程序存储器;

EA非=1时,先访问内部程序存储器,再访问外部

67.SPI三总线结构,系统一般使用4个I/O引脚:

MISO(主机输入/从机输出)、MOSI(主机输出/从机输入)、SLCK(串行时钟线)、SS非(从机选择)

68.SPI进行数据传送的时候,先传送MSB(高位),后传送LSB(低位)

69.SPI设置为主机方式时SCLK为输出;

SPI设置为从机方式时SCLK为输入

70.SS非在从机方式时,是输入端,用于使能SPI从机进行数据传送;

在主机方式时,一般由外部置为高电平

71.SCLK、MOSI、MISO三根线同名端相连;

一些芯片的CS非用一根I/O口线来控制

72.80C51中用串行口的方式0,实现SPI同步串行通信功能

73.I²

C公用双总线结构SDA(串行数据线),SCL(串行时钟线),允许多主

主控器件产生串行时钟(SCL)信号

74.总线条件:

a)总线不忙:

SCL和SDA都保持高电平

b)开始数据传送:

SDA保持高电平,SCL由高转低,作为起始信号(START)

c)停止数据传送:

SDA保持高电平,SCL由低转高,作为停止信号(STOP)

d)数据有效性:

开始信号以后,SCL保持高电平期间,SDA保持稳定说明数据有效(期间不变)

75.PSEN非在ALE下降之后(一个状态),在第三个节拍(3/2个状态)出下降,与ALE同时在第三个状态上升

76.数据存储器拓展,16K片外存储器6264的OE非接RD非,WE非接WR非,线选法进行片选(P2.7)接CE非(使能,低电平有效)

77.DAC0823转换器——要使输入存储器直通需要ILE=1&

CS非=0&

WR1非=0;

要使DAC寄存器直通需要XFER非=0&

WR2非=0

78.ADC0809转换器——启动A/D:

MOVX@DPTR,A(P2.7=0,WR非=0);

读A/D转换数据:

MOVXA,@DPTR

79.通过80C51I/O口扩展的矩阵式键盘,4根行线连接到P1.0~P1.3四个低位,并通过“与”门连到INT0非端

没有键被按下时,INT0非为高电平;

当有键按下时,INT0非变为低电平,向CPU发中断请求。

若CPU开放外部中断0,则响应中断、执行中断服务程序扫描键盘。

80.N位LED显示器需要N根位选线和8*N根段选线。

81.LED动态显示是不是显示字符都一样?

82.LCD1602

a)寄存器指令寄存器IR,数据寄存器DR

b)忙信号标志BF由数据线D7输出(若MOVXA,@DPTR/@R1,JBACC.7,rel)

c)地址计数器AC(没弄懂?

)

d)显示数据RAM(DDRAM)每一行各有一个40个字符的显示数据RAM区,第一行DDRAM单元的地址为00H~27H;

第二行DDRAM单元的地址为40H~67H

e)字符发生器ROM(CGROM)可产生160个不同的字符代码所表示的5*7点阵字符图形。

f)字符发生器RAM(CGRAM)自编程字符代码

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 浙江大学 单片 微型计算机 接口 技术 复习 要点

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx