Verilog流水灯实验报告Word格式.docx

Verilog流水灯实验报告Word格式.docx

- 文档编号:20534531

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:7

- 大小:149.92KB

Verilog流水灯实验报告Word格式.docx

《Verilog流水灯实验报告Word格式.docx》由会员分享,可在线阅读,更多相关《Verilog流水灯实验报告Word格式.docx(7页珍藏版)》请在冰豆网上搜索。

2、编写Verilog程序实现LED等依次亮灭,用Modelsim进行仿真,绘制波形图。

五、实验设计

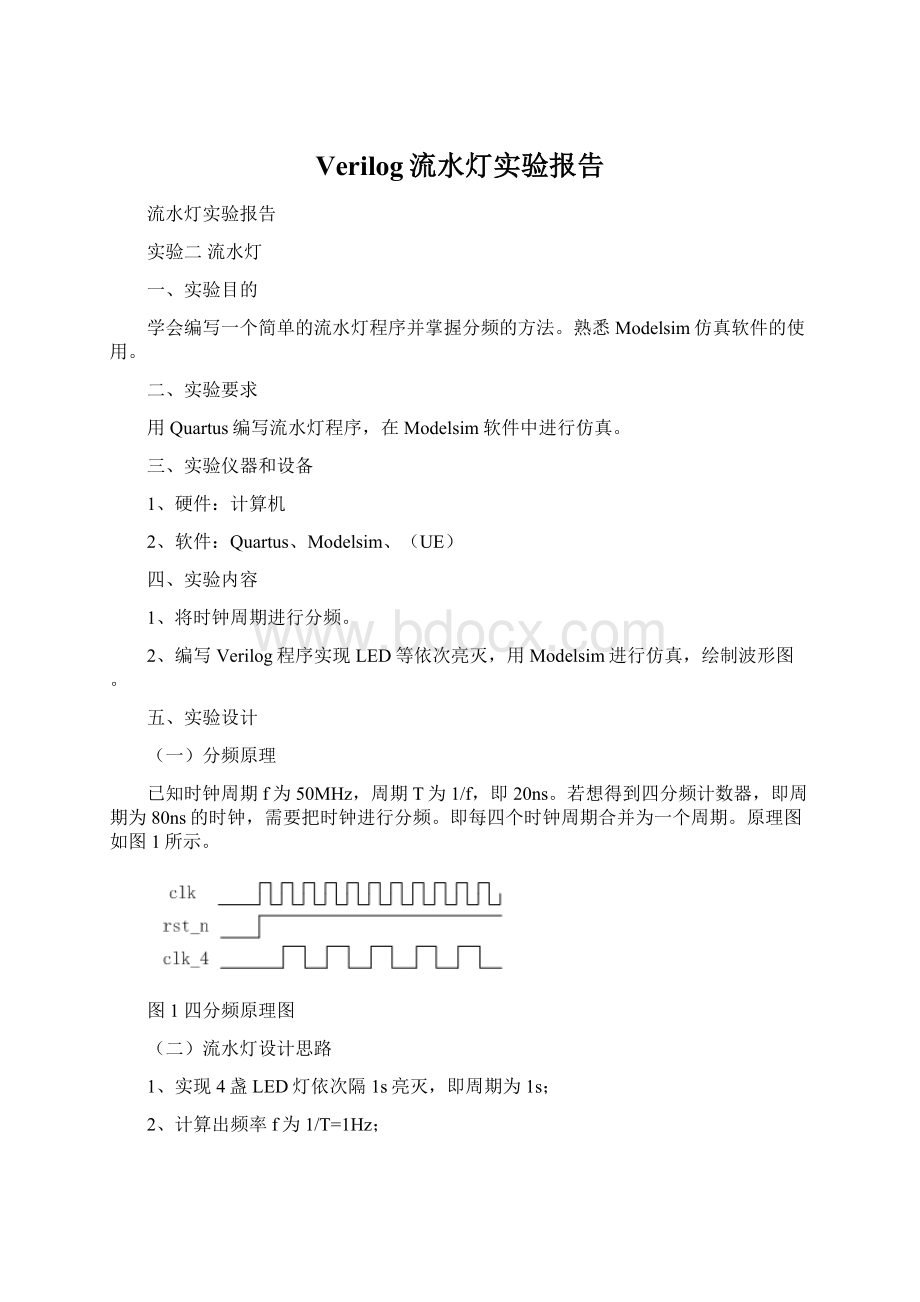

(一)分频原理

已知时钟周期f为50MHz,周期T为1/f,即20ns。

若想得到四分频计数器,即周期为80ns的时钟,需要把时钟进行分频。

即每四个时钟周期合并为一个周期。

原理图如图1所示。

图1四分频原理图

(二)流水灯设计思路

1、实现4盏LED灯依次隔1s亮灭,即周期为1s;

2、计算出频率f为1/T=1Hz;

3、设置计数器cnt,当检测到clk上升沿时开始计数,当cnt计数到24_999_999时,clk_4跳变为1,LED灯亮起,当cnt计数49_999_999时,clk_4置0,LED灯熄灭。

4、给LED赋初值4’b0001,第一盏灯亮。

5、利用位拼接,实现循环。

(三)设计框图

图2设计基本框图

(四)位拼接的用法

若输入a=4'

b1010,b=3'

b101,c=4'

b0101,想要使输出d=5'

b10001

用位拼接,符号“{}”:

d<

={b[2:

1],c[1],a[2:

1]}

即把b的低1~2位10,c的低1位0,a的低1~2位01拼接起来,得到10001。

流水灯

4'

b0001

b0010

b0100

b1000

相当于把低三位左移,并最高位放在最低位。

用位拼接可写为:

led<

={led[2:

0],led[3]};

低三位最高位

六、实验方法和步骤

(一)时钟分频

1、编写分频程序。

2、编写测试程序。

3、进行仿真,波形如图3所示。

图3分频仿真结果

(二)流水灯

3、编写测试程序。

3、进行仿真,为了节约时间和方便观察波形,将计数器值分别改为24、49跳转。

波形如图4所示。

图4流水灯仿真结果

七、实验参考程序

1、程序文件

modulediv_clk(//模块名与文件名一致。

定义端口列表,

inputwireclk,//输入线型

inputwirerst_n,

outputregclk_4//输出定义为寄存器型

);

reg[3:

0]cnt;

//中括号定义位宽,定义中间变量cnt

always(posedgeclk)

if(rst_n==0)

cnt<

=0;

//复位为0,计数器也为0

elseif(cnt==3)//当计数器=3时清零(可用elseif)

else

=cnt+1;

//计数器自加1

clk_4<

//复位为0.clk_4为0

elseif(cnt==1)

=1;

//当计数器为1时,时钟跳变为1

elseif(cnt==3)

//当计数器为3时,时钟跳变为0

endmodule

2、测试文件

`timescale1ns/1ns

moduletb_div_clk();

regclk;

regrst_n;

wireclk_4;

initial

begin

clk=0;

rst_n=0;

#100

rst_n=1;

end

always#5clk=~clk;

div_clkdiv_clk_inst(

.clk(clk),

.rst_n(rst_n),

.clk_4(clk_4)

endmodule

moduleLSD(//模块名与文件名一致。

inputwireclk,//输入线型

inputwirerst_n,

outputreg[3:

0]led

reg[25:

regclk_4;

elseif(cnt==49_999_999)//当计数器=49999999时清零(可用elseif)

always(posedgeclkornegedgeclk)//异步复位

elseif(cnt==24_999_999)

//当计数器为24999999时,时钟跳变为1

elseif(cnt==49_999_999)

//当计数器为49999999时,时钟跳变为0

clk_4=clk_4;

always(posedgeclk_4ornegedgeclk_4)

led<

=4'

b0001;

={led[2:

0],led[3]};

//位拼接

moduleLSD();

regcnt;

wireled;

LSDLSD_inst(

.led(led)

八、实验小结

1、做实验要养成良好的习惯,每次做实验时,都要建立一个新的文件夹存放实验所需的程序文件,为仿真时添加文件做准备,也方便以后的查找和使用。

2、写程序前要想清楚电路实现原理,根据所学数电知识对各个元器件进行控制。

3、写程序时注意排版美观整洁,同时注意添加注释。

4、注意程序中模块名要和文件名一致,否则程序报错,无法编译通过。

5、仿真时,可以选择不同的进制。

在想要更改的地方右键,选择【Radix】,其中【Binary】为二进制。

如图5所示。

图5更改进制

6、在流水灯仿真时,LED灯的波形一开始是错误的,因为程序中只检测了上升沿always(posedgeclk),加上下降沿检测always(posedgeclkornegedgeclk),即可解决问题,成功绘制波形图。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Verilog 流水 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx

《中式面点基础》中职课件-1 项目一 生物膨松面团制品.pptx

《中式面点基础》中职课件-1 项目一 生物膨松面团制品.pptx