DSP2812总结之2Word下载.docx

DSP2812总结之2Word下载.docx

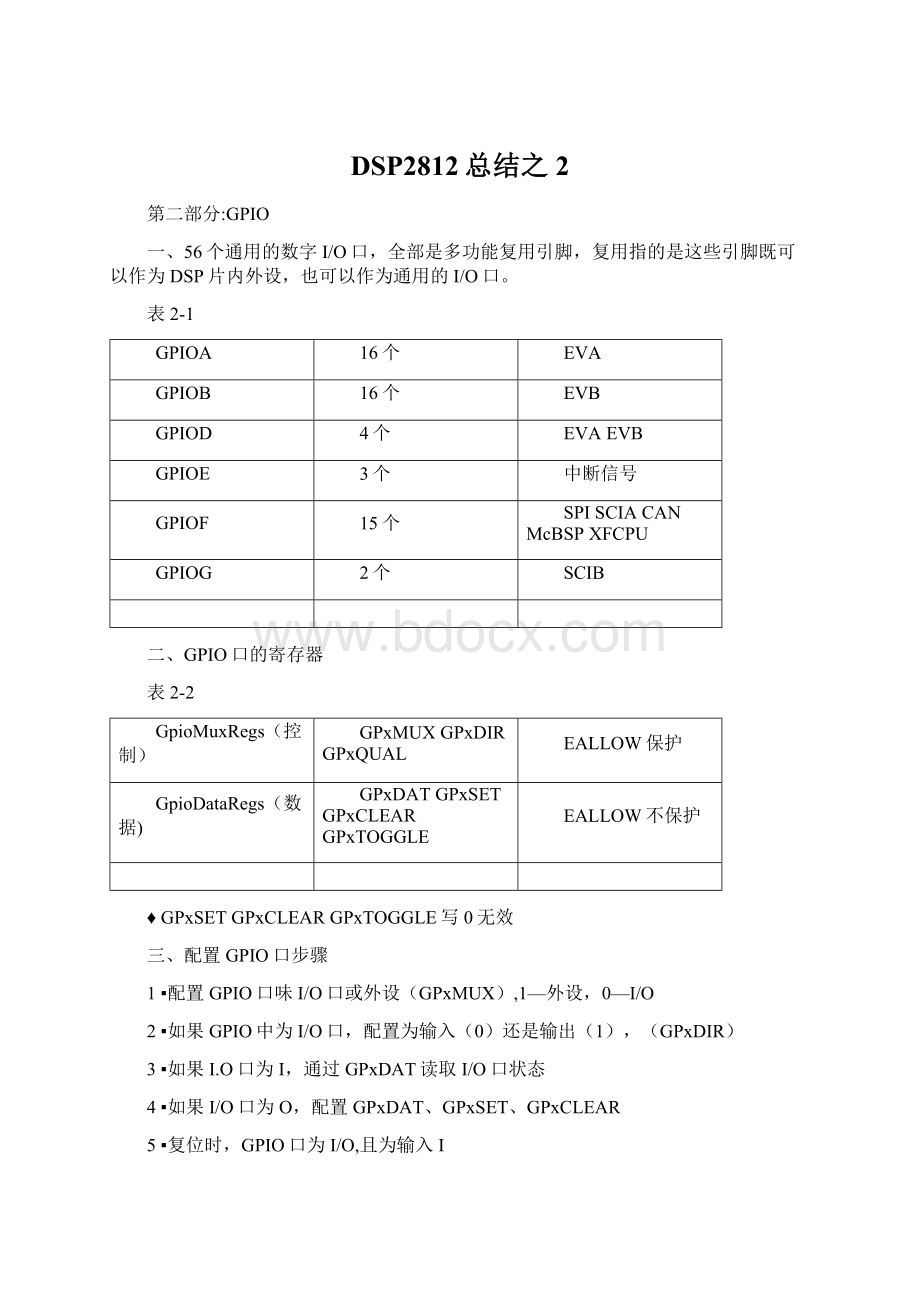

- 文档编号:20525765

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:46

- 大小:163.17KB

DSP2812总结之2Word下载.docx

《DSP2812总结之2Word下载.docx》由会员分享,可在线阅读,更多相关《DSP2812总结之2Word下载.docx(46页珍藏版)》请在冰豆网上搜索。

148

XA[14]

A10

144

XA[13]

E10

141

XA[12]

C11

138

19位XINTF地址总线

XA[11]

A14

132

XA[10]

C12

130

XA[9]

D14

125

XA[8]

E12

XA[7]

F12

121

XA[6]

G14

111

XA[5]

H13

108

XA[4]

J12

103

XA[3]

M11

85

XA[2]

N10

80

XA[1]

M2

43

XA[0]

G5

18

XD[15]

A9

147

PU

16位XINTF数据总线

XD[14]

B11

139

XD[13]

J10

97

XD[12]

L14

96

XD[11]

N9

74

XD[10]

L9

73

XD[9]

M8

68

XD[8]

P7

65

XD[7]

L5

54

XD[6]

L3

39

XD[5]

J5

36

XD[4]

K3

33

XD[3]

J3

30

XD[2]

H5

27

XD[1]

H3

24

XD[0]

G3

21

续表

PU/PD

XINTF信号(仅F2812)

XMP/

F1

17

I

可选择微处理器/微计算机模式。

可以在两者之间切换。

为高电平时外部接口上的区域7有效,为低电平时区域7无效,可使用片内的BootROM功能。

复位时该信号被锁存在XINTCNF2寄存器中,通过软件可以修改这种模式的状态。

此信号是异步输入,并与XTIMCLK同步

E7

159

外部DMA保持请求信号。

为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步

K10

82

外部DMA保持确认信号。

当XINTF响应

的请求时

呈低电平,所有的XINTF总线和选通端呈高阻态。

和

信号同时发出。

当

有效(低)时外部器件只能使用外部总线

P1

44

XINTF区域0和区域1的片选,当访问XINTF区域0或1时有效(低)

P13

88

XINTF区域2的片选。

当访问XINTF区域2时有效(低)

B13

133

XINTF区域6和7的片选。

当访问区域6或7时有效(低)

N11

84

写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGx寄存器的前一周期、当前周期和后一周期的值确定

M3

42

读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由XTIMINGx寄存器的前一周期、当前周期和后一周期的值确定。

注意:

是互斥信号

XR/

N4

51

通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期

XREADY

B6

161

数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREADY有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREADY采样3次。

以XTIMCLK频率对XREADY的采样与XCLKOUT的模式无关

JTAG和其他信号

X1/XCLKIN

K9

77

58

振荡器输入/内部振荡器输入,该引脚也可以用来提供外部时钟。

28x能够使用一个外部时钟源,条件是要在该引脚上提供适当的驱动电平,为了适应1.8V内核数字电源(VDD),而不是3.3V的I/O电源(VDDIO)。

可以使用一个嵌位二极管去嵌位时钟信号,以保证它的逻辑高电平不超过VDD(1.8V或1.9V)或者去使用一个1.8V的振荡器

X2

M9

76

57

振荡器输出

XCLKOUT

F11

119

87

O

源于SYSCLKOUT的单个时钟输出,用来产生片内和片外等待状态,作为通用时钟源。

XCLKOUT与SYSCLKOUT的频率或者相等,或是它的1/2,或是1/4。

复位时XCLKOUT=SYSCLKOUT/4

TESTSEL

A13

134

PD

测试引脚,为TI保留,必须接地

D6

160

113

I/O

器件复位(输入)及看门狗复位(输出)。

器件复位,XRS使器件终止运行,PC指向地址0x3FFFC0(注:

0xXXXXXX中的0x指出后面的数是十六进制数。

例如0x3FFFC0=3FFFC0h)当XRS为高电平时,程序从PC所指出的位置开始运行。

当看门狗产生复位时,DSP将该引脚驱动为低电平,在看门狗复位期间,低电平将持续512个XCLKIN周期。

该引脚的输出缓冲器是一个带有内部上拉(典型值100mA)的开漏缓冲器,推荐该引脚应该由一个开漏设备去驱动

TEST1

M7

67

测试引脚,为TI保留,必须悬空

TEST2

N7

66

50

B12

135

98

有内部上拉的JTAG测试复位。

当它为高电平时扫描系统控制器件的操作。

若信号悬空或为低电平,器件以功能模式操作,测试复位信号被忽略

在

上不要用上拉电阻。

它内部有上拉部件。

在强噪声的环境中需要使用附加上拉电阻,此电阻值根据调试器设计的驱动能力而定。

一般取22kΩ即能提供足够的保护。

因为有了这种应用特性,所以使得调试器和应用目标板都有合适且有效的操作

TCK

A12

136

99

JTAG测试时钟,带有内部上拉功能

TMS

D13

126

92

JTAG测试模式选择端,有内部上拉功能,在TCK的上升沿TAP控制器计数一系列的控制输入

TDI

C13

131

带上拉功能的JTAG测试数据输入端。

在TCK的上升沿,TDI被锁存到选择寄存器、指令寄存器或数据寄存器中

TDO

D12

127

93

JTAG扫描输出,测试数据输出。

在TCK的下降沿将选择寄存器的内容从TDO移出

EMU0

D11

137

100

带上拉功能的仿真器I/O口引脚0,当

为高电平时,此引脚用作中断输入。

该中断来自仿真系统,并通过JTAG扫描定义为输入/输出

EMU1

C9

146

105

仿真器引脚1,当

为高电平时,此引脚输出无效,用作中断输入。

该中断来自仿真系统的输入,通过JTAG扫描定义为输入/输出

ADC模拟输入信号

ADCINA7

B5

167

采样/保持A的8通道模拟输入。

在器件未上电之前ADC引脚不会被驱动

ADCINA6

D5

168

120

ADCINA5

E5

169

ADCINA4

A4

170

122

ADCINA3

B4

171

123

ADCINA2

C4

172

124

ADCINA1

D4

173

ADCINA0

A3

174

ADCINB7

F5

9

采样/保持B的8通道模拟输入。

在器件未上电之前ADC引脚不会

ADCINB6

D1

8

ADCINB5

D2

7

ADCINB4

D3

6

ADCINB3

C1

5

ADCINB2

B1

4

ADCINB1

C3

3

ADCINB0

C2

2

ADCREFP

E2

11

ADC参考电压输出(2V)。

需要在该引脚上接一个低ESR(50mΩ~1.5Ω)的10μF陶瓷旁路电容,另一端接至模拟地

ADCREFM

E4

10

ADC参考电压输出(1V)。

ADCRESE-XT

F2

16

ADC外部偏置电阻(24.9kΩ)

ADCBGREFN

E6

164

116

AVSSREFBG

E3

12

ADC模拟地

AVDDREFBG

E1

13

ADC模拟电源(3.3V)

ADCLO

B3

175

普通低侧模拟输入

VSSA1

F3

15

VSSA2

C5

165

117

VDDA1

F4

14

VDDA2

A5

166

118

VSS1

C6

163

115

ADC数字地

VDD1

A6

162

114

ADC数字电源(1.8V)

VDDAIO

B2

1

I/O模拟电源(3.3V)

VSSAIO

A2

176

128

I/O模拟地

电源信号

VDD

H1

23

20

1.8V或1.9V核心数字电源

L1

37

29

P5

56

P9

75

P12

63

K12

G12

112

C14

B10

143

102

C8

154

110

VSS

G4

19

内核和数字I/O地

K1

32

26

L2

38

P4

52

K6

P8

70

53

M10

78

59

L11

86

62

K13

J14

G13

E14

B14

129

95

D10

142

C10

B8

153

109

I/O口模拟地

VDDIO

J4

31

25

I/O数字电源(3.3V)

L7

64

49

L10

81

N14

G11

83

E9

145

104

VDD3VL

N8

69

Flash核电源(3.3V),上电后所有时间内都应将该引脚接至3.3V

通用输入/输出(GPIO)或外围信号

GPIOA或EVA信号

GPIOA0

PWM1(O)

M12

GPIO或PWM输出引脚#1

GPIOA1

PWM2(O)

M14

GPIO或PWM输出引脚#2

GPIOA2

PWM3(O)

L12

94

GPIO或PWM输出引脚#3

GPIOA3

PWM4(O)

L13

71

GPIO或PWM输出引脚#4

GPIOA4

PWM5(O)

K11

72

GPIO或PWM输出引脚#5

GPIOA5

PWM6(O)

K14

101

GPIO或PWM输出引脚#6

GPIOA6

T1PWM-T1CMP

J11

GPIO或定时器1输出#1

续表

176针PGF封装

GPIOA7

T2PWM_T2CMP

J13

PUI

GPIO或定时器2输出#2

GPIOA8

CAP1_QEP1(I)

H10

106

GPIO或捕获输入#1

GPIOA9

CAP2_QEP2(I)

107

79

GPIO或捕获输入#2

GPIOA10

CAP3_QEPI1(I)

GPIO或捕获输入#3

GPIOA11

TDIRA(I)

F14

I/OZ

GPIO或计数器方向

GPIOA12

TCKINA

(1)

F13

GPIO或计数器时钟输入

GPIOA13

(I)

E13

89

GPIO或比较器1输出

GPIOA14

E11

90

GPIO或比较器2输出

GPIOA15

F10

91

GPIO或比较器3输出

GPIOB或EVB信号

GPIOB0

PWM7(O)

N2

45

GPIO或PWM输出引脚#7

GPIOB1

PWM8(O)

P2

46

34

GPIO或PWM输出引脚#8

GPIOB2

PWM9(O)

N3

47

35

GPIO或PWM输出引脚#9

GPIOB3

PWM10(O)

P3

48

GPIO或PWM输出引脚#10

GPIOB4

PWM11(O)

L4

GPIO或PWM输出引脚#11

GPIOB5

PWM12(O)

M4

GPIO或PWM输出引脚#12

GPIOB6

T3PWM_T3CMP

K5

40

GPIO或定时器3输出

GPIOB7

T4PWM_T4CMP

N5

55

41

GPIO或定时器4输出

GPIOB8

CAP4_QEP3(I)

M5

GPIO或捕获输入#4

GPIOB9

CAP5_QEP4(I)

M6

GPIO或捕获输入#5

GPIOB10

CAP6_QEPI2(I)

P6

60

GPIO或捕获输入#6

GPIOB11

TDIRB(I)

L8

GPIO或定时器方向

GPIOB12

TCLKINB(I)

K8

GPIO或定时器时钟输入

GPIOB13

N6

61

GPIO或比较器4输出

GPIOB14

L6

GPIO或比较器5输出

GPIOB15

K7

GPIO或比较器6输出

GPIOD或EVA信号

GPIOD0

H14

定时器1比较输出

GPIOD1

/

G10

定时器2比较输出或EV-A开启外部AD转换输出

GPIOD或EVB信号

GPIOD5

P10

定时器3比较输出

GPIOD6

P11

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- DSP2812 总结

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx