Quartus II附录Word格式.docx

Quartus II附录Word格式.docx

- 文档编号:20494308

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:12

- 大小:524.32KB

Quartus II附录Word格式.docx

《Quartus II附录Word格式.docx》由会员分享,可在线阅读,更多相关《Quartus II附录Word格式.docx(12页珍藏版)》请在冰豆网上搜索。

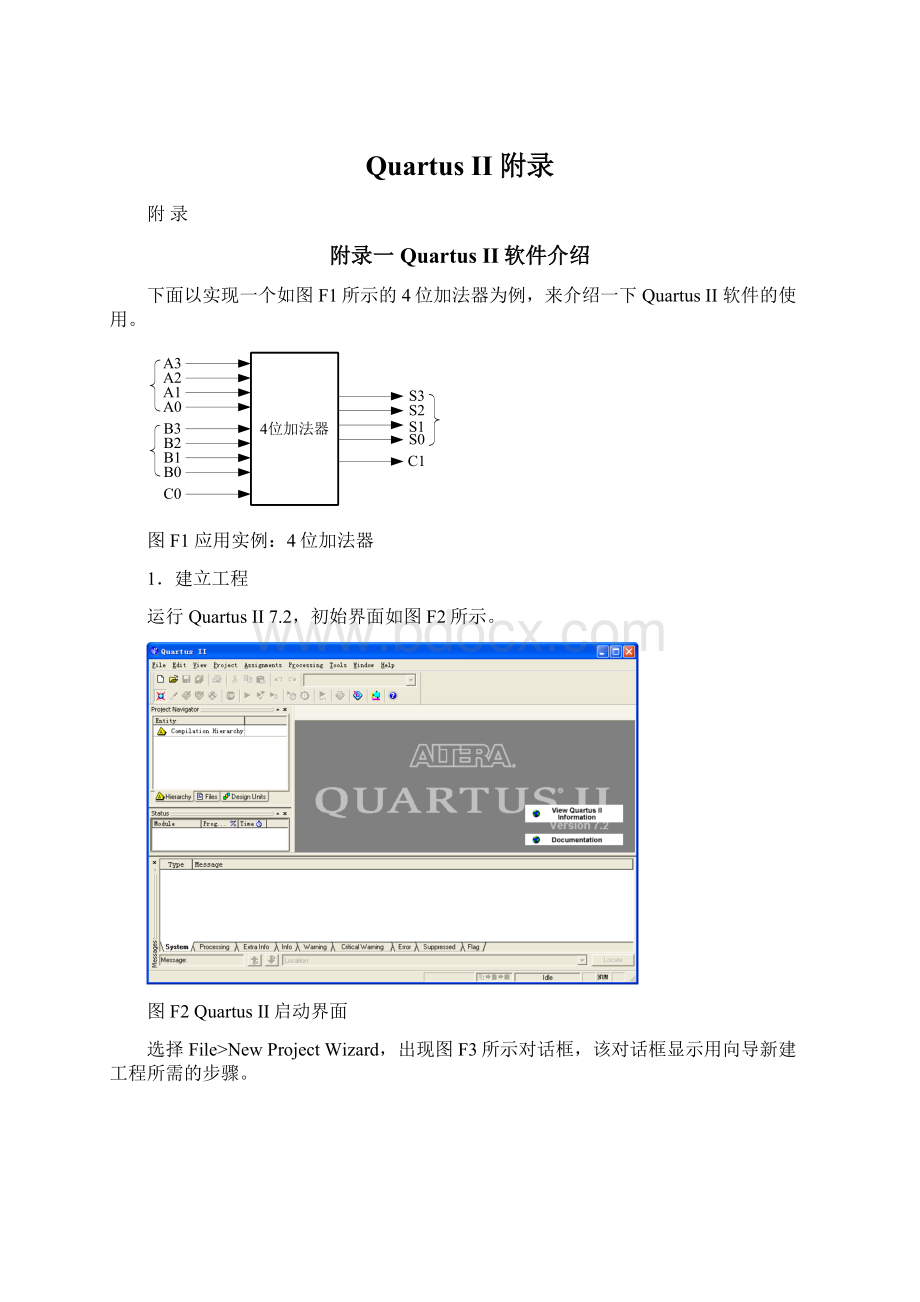

图F5 为工程新建目录

接下来出现图F6所示的对话框,可以将已经存在的设计文件添加到当前工程中来。

图F6 为工程添加设计文件

点击Next按钮,出现图F7所示对话框。

在Availabledevices列表中选择DE2平台上的FPGA型号EP2C35F672C6。

图F7 选择器件

点击Next,出现图F8对话框。

该对话框提示用户选择将要在新建工程中使用的第三方设计工具。

本设计全部采用QuartusII提供的设计输入、综合、仿真和时序分析工具,故直接点击Next。

图F8 选择第三方工具

图F9为汇总对话框,按Finish按钮完成新工程的建立。

图F9 新建工程信息汇总

2.设计输入

在当前工程下,选择File>

New菜单,打开图F10所示对话框。

图F10 新建文件对话框

选择VerilogHDLFile,点击OK,打开TextEditor。

Saveas菜单,进入图F11对话框。

图F11 另存为对话框

输入文件名为adder,选择保存类型为VerilogHDLFile,选中Addfiletocurrentproject,把名为adder.v的文件添加到当前工程中。

然后在TextEditor中,向adder.v中写入如下例1的代码。

--例1 编辑输入设计文件(adder.v)

moduleadder(A,B,C0,S,C1);

input[3:

0]A,B;

inputC0;

output[3:

0]S;

outputC1;

reg[3:

regC1;

always@(AorBorC0)

begin

S=A+B+C0;

if(A+B+C0>

15)

C1=1;

else

C1=0;

end

endmodul

然后对输入文件进行编译。

使用Processing>

startcompilation菜单,或点击工具按钮

,完成对设计的分析、综合与实现。

如果编译成功,弹出编译成功消息框,点击确定后,QuartusII界面如图F12所示。

如果编译过程中有错误出现,编译自动终止,并在Message窗口中显示错误信息。

编译结束后,系统还会自动打开一个CompilationReport窗口,显示了编译后的设计对目标芯片的资源占用情况。

图F12 编译结果

3.分配引脚

选择Assignments>

Pins菜单,为设计的输入和输出分配引脚。

文件adder.v中的输入输出变量、DE2板上的资源,以及FPGA引脚的对应关系如表F1所示。

表F1 引脚分配对照表

I/O

程序变量

DE2板

FPGA引脚

输

入

A[3]

SW4

A[2]

SW3

A[1]

SW2

A[0]

SW1

B[3]

SW8

B[2]

SW7

B[1]

SW6

B[0]

SW5

C0

SW0

出

S[3]

LEDG3

S[2]

LEDG2

S[1]

LEDG1

S[0]

LEDG0

C1

LEDG4

按照表格对FPGA引脚进行分配,结果如图F13所示。

图F13引脚分配结果

4.电路仿真

为了检验设计的正确性,接下来对程序实现的功能进行仿真。

首先建立矢量波形文件。

New菜单,OtherFiles选项卡,VectorWaveformFile,如图F14所示。

图F14 新建矢量波形文件

点击OK,进入矢量波形编辑器窗口,如图F15所示。

图F15 矢量波形编辑器窗口

使用File>

SaveAs菜单将文件保存为adder.vwf。

用Edit>

EndTime菜单设定仿真终止时间,这里设为200ns,用View>

FitinWindow菜单在窗口中显示整个仿真的时间范围。

接下来,需要将输入输出节点加入到波形中来。

选择Edit>

Insert>

InsertNodeorBus菜单,打开图F16所示窗口。

图F16 InsertNodeorBus对话框

点击NodeFinder,在NodeFinder窗口中选择Filter为Pins:

all,点击List,结果见图F17。

图F17 NodeFinder对话框

点击

按钮,将所有的节点添加到SelectedNodes框中。

点击OK,返回波形编辑窗口,用选择工具

和波形编辑工具

来编辑输入波形。

编辑后的结果如图F18,限于篇幅,图中只显示了A[3:

0]=[0000],B[3:

0]=[0000]~[1111],C0=0的输入组合。

图F18添加了节点的波形编辑窗口

下面进行功能仿真。

Settings菜单,打开Settings窗口,如图F19。

图F19 仿真设置窗口

点击SimulatorSettings,选择Simulationmode为Functional,按OK按钮,完成设置。

用Processing>

GenerateFunctionalSimulationNetlist菜单产生功能仿真所需的网表,最后用Processing>

StartSimulation菜单或

按钮启动功能仿真。

仿真结束后,得到的仿真波形如图F20所示。

图F20 仿真波形输出

5.编程配置

编程配置是把完成的4位加法器电路设计配置到FPGA芯片内,这里选用ALTERA公司的DE2实验板进行配置,DE2实验板内包含一片CycloneII芯片。

QuartusII提供两种编程配置方式:

一种是JTAG模式,通过USBBlaster直接配置FPGA,但FPGA中的内容掉电丢失;

另一种是AS模式,通过USBBlaster对DE2上的串行配置芯片EPCS16编程,由EPCS16来完成对FPGA的配置。

两种模式通过DE2上的SW19来选择:

当SW19处于RUN位置时,为JTAG模式;

当SW19处于PROG位置时,为AS模式。

用JTAG编程的步骤:

(1)连接主机的USB口和DE2的BLASTER口,打开DE2电源;

(2)将SW19拨到RUN档;

(3)使用Tool>

Programmer菜单或者点击

按钮,打开编程配置窗口,如图F21,双击USBBlaster,然后单击Close按钮,完成硬件设置;

图F21 编程窗口

(4)如果显示NoHardware,则点击HardwareSetup,打开硬件设置窗口,如图F22;

图F22 硬件设置窗口

(5)如果文件列表中没有文件,点击AddFile按钮,添加add.sof文件,确认Device项为DP2C35F672,并选中Program/Configure选项;

(6)点击Start按钮,开始编程,编程结束后,DE2上的发光二极管GOOD变亮。

用AS模式编程的步骤:

(1)选择Settings>

Device菜单打开器件配置窗口,如图F23;

图F23 器件配置窗口

(2)单击Device&

PinOptions按钮,选择Configurationx选项卡,在ConfigurationDevice框中选择EPCS16,如图F24所示,而后点击确定,回到上一级界面,点击OK结束配置,重新编译;

图F24 选择配置器件

(3)如果DE2平台电源打开,则关闭电源,将SW19拨到PROG档,连接好USB线,然后打开DE2电源;

(4)选择Tools>

Programmer菜单或者

按钮,打开图F21的编程配置窗口,在选择Mode为ActiveSerialProgrammer;

(5)点击AddFile按钮,添加adder.pof,并选中Program/Configure选项,结果如图F25所示;

图F25 AS模式下的编程配置窗口

(6)单击Start按钮,开始编程,变成结束后,DE2实验板上的发光二极管GOOD变亮。

6.电路测试

将SW19拨到RUN档,改变SW0~SW8,观察LEDG0~LEDG4。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Quartus II附录 II 附录

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx