FPGA直接控制ADC0809对模拟信号进行采样DOC文档格式.docx

FPGA直接控制ADC0809对模拟信号进行采样DOC文档格式.docx

- 文档编号:20474875

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:32

- 大小:313.97KB

FPGA直接控制ADC0809对模拟信号进行采样DOC文档格式.docx

《FPGA直接控制ADC0809对模拟信号进行采样DOC文档格式.docx》由会员分享,可在线阅读,更多相关《FPGA直接控制ADC0809对模拟信号进行采样DOC文档格式.docx(32页珍藏版)》请在冰豆网上搜索。

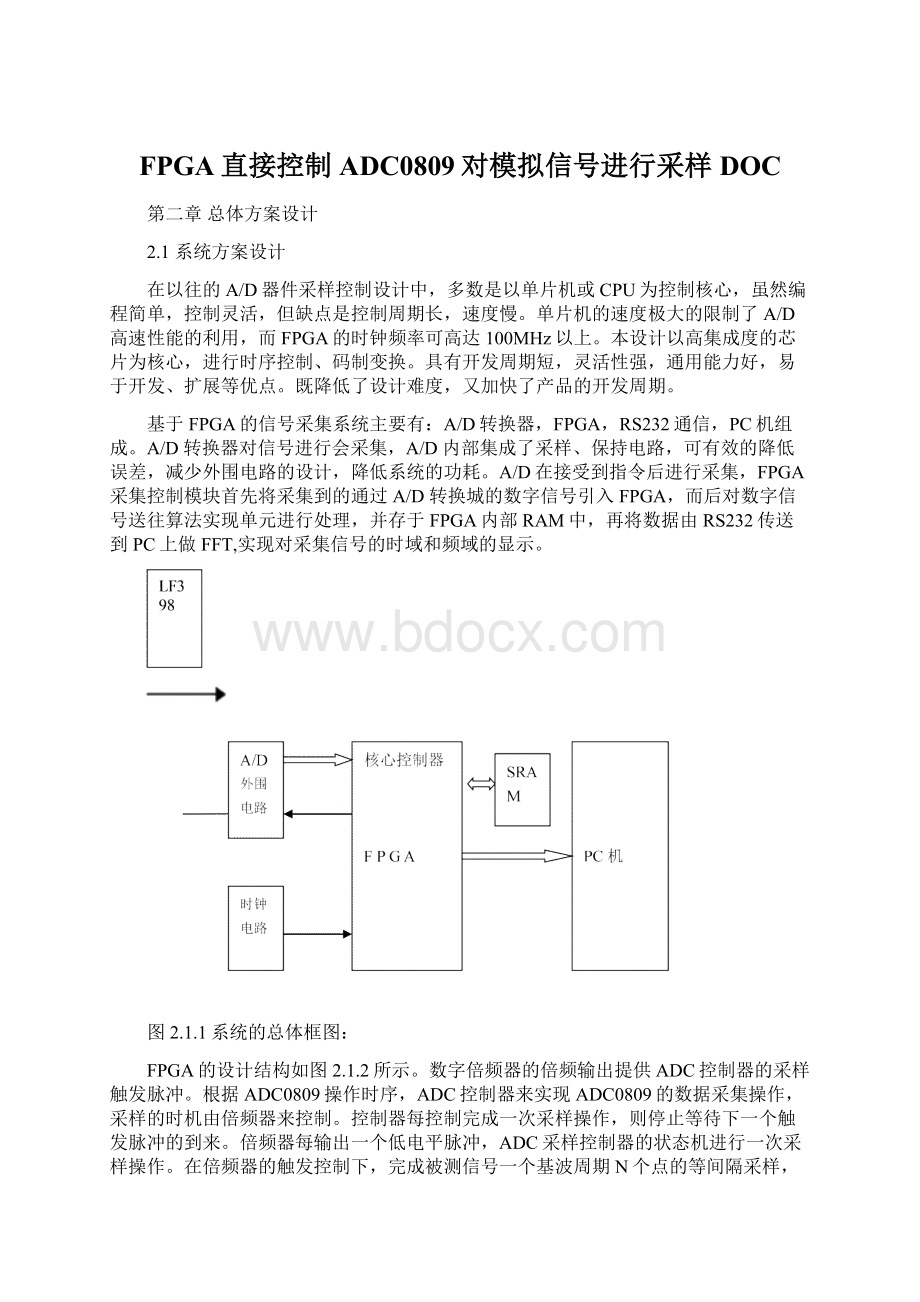

2.2.2AD模块方案设计

本课题要求对不大于10kHz的任意周期信号进行数据采集,根据奈奎斯特采样定理,AD的采样速率最小应为20kHz,而且要求系统简单可靠。

综合考虑,本系统最后选择了adc0809,它具有最高100sps的采样速率,转换时间不大于100us,芯片的控制和外围电路都较为简单,完全满足系统的设计要求。

2.2.3lf398模块方案设计

对变化较慢的模拟信号(即所谓低频信号)在A/D芯片之前可不加采样保持电路。

确切的说,若A/D转换器的速度比较模拟信号变化速度高很多倍,我们可将模拟信号直接加到A/D转换器上。

如果模拟信号变化比较快,为了保证转换精度,就要在A/D之前加上采样保持电路,使得在转换期间保持模入信号不变。

第三章系统硬件具体设计:

3.1硬件总体设计

本硬件电路的主要芯片有:

模数转换芯片ADC0809、FPGA。

其硬件电路如下图所示:

图3.1FPGA控制的ADC0809采样电路

图3.1中,输入部分:

IN0-IN7为8条模拟量输入通道。

ADC0809对输入模拟量要求:

信号单极性,电压范围是0-5V,若信号太小,必须进行放大;

输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路;

中间部分:

主要是FPGA芯片,实现对ADC0809的采样控制;

输出部分:

输出的8位二进制数字信号由两种方式显示,一种方式是由8个发光二极管组成,每一个二极管代表一位二进制数,当二极管处于发光状态即“亮”时,表示输出二进制“1”;

否则输出“0”。

简言之,“亮”—“1”,“灭”—“0”;

另一种输出方式是由两位数码管组成的,每一位数码管以十六进制(即0--F)显示二进制输出的四位。

3.2取样定理

为了能正确无误地用取样信号VS表示模拟信号VI,取样信号必须有足够高的频率。

可以证明,为了保证能从取样信号将原来的被取样信号恢复,必须满足

FS>

=FI(MAX)上式就是取样定理,其中,FS为取样频率,FI(MAX)为输入模拟信号Vi的最高频率分量的频率。

在满足上式的条件下,可以用低通滤波器将VS还原为VI。

这个低通滤波器的电压传输系数在低于FI(MAX)的范围内应保持不变,而在FS-FI(MAX)以前应迅速下降为0,因此,A/D转换器工作时的取样频率必须高于最大频率,取样频率提高也就意味着留给每次转换的时间相应的缩短,这就要求转换电路必须具备更快的工作速度。

因此,为了满足要求,通常取FS=(3--5)FI(MAX)。

3.3模数转换过程

采样-保持:

由于采样时间极短,采样输出为一串断续的窄脉冲,而要把每一个采样的窄脉冲信号数字化,是需要一定的时间,因此在两次采样之间,应将采样的模拟信号暂时存储起来。

把每次采样的模拟信号存储到下一个采样脉冲到来之前称为保持。

量化与编码:

量化与编码电路是A/D转换器的核心组成部分,对采样值的量化一般有两种方法:

(1)只舍不入:

首先取一最小量化单位∆=UM/2^N,UM是输入模拟电压的最大值,n是输出数字代码的位数。

当输入模拟电压U1在0-∆之间,则归入0*∆,当U1在∆-2∆之间,则归入1∆。

这样的量化方法产生的最大量化误差为,而且量化误差总是为正。

(2)有舍有入:

如果量化单位∆=2UM/(2^N+1)-1,当输入电压U1在0-∆/2之间,归入0*∆,当UT在∆/2-3∆/2之间归入1∆。

这种量化方法产生的最大量化误差为∆/2,而且量化误差有正、有负。

3.4模数转换类型

直接型A/D转换器:

直接型A/D转换器是把输入的模拟电压直接转换成输出的数字代码,而不需要经过中间变量。

这种A/D转换器的优点是转换速度快,但转换精度受分压电阻、基准电压及比较器阈值电压等精度的影响,精度较差。

间接型A/D转换器:

间接型A/D转换器是先将输入的模拟电压u转换成与之大小对应的中间变量,然后再将中间变量转换为输出的数字量。

目前使用较多的多属于电压-时间(V-T)变换型和电压-频率(V-F)变换型两大类:

(1)电压/时间型A/D转换器有单积分型、双积分型和四重积分型多种,但用的最多的是双积分型。

(2)电压-频率型A/D转换器,主要有积分器、窗口比较器、触发器和计数器等组成。

3.5模数转换精度

A/D转换器的转换精度:

在单片集成A/D转换器中,也用分辨率和转换误差来描述转换精度。

分辨率:

A/D转换器的分辨率是指引起输出数字量变动一个二进制数码最低有效位时,输入模拟量的最小变化量,小于此最小变化量的输入模拟电压变化,将不会引起输出数字量的变化。

转换误差:

通常以相对误差的形式给出,它表示A/D转换器实际输出的数字量与理想输出的数字量之间的差别,并用最低有效位LSB的倍数表示。

3.6模数转换芯片ADC0809

大规模集成电路芯片ADC0809是一种由单一+5V电源供电,采用逐次逼近转换原理,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中,能够对0~+5V的8路输入模拟电压进行分时转换的通用型可编程模数转换器。

(1)ADC0809的内部逻辑及引脚结构:

IN0STCLK

IN1EOC

IN2

IN3D0

IN4D1

IN5D2

IN6D3

IN7D4

D5

D6

D7

A

B

C

ALEVREF+VREF--OE

图3.6.1内部逻辑及引脚结构图

由上图可知,ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

地址锁存与译码电路完成对A,B,C三个地址位进行锁存和译码,其译码输出用于通道选择。

八位A/D转换器是逐次逼近式,由控制与时序电路、逐次逼近寄存器、树状开关以及256R电阻梯网络等组成。

(2).引脚结构

128

227

326

425

524

623

722

821

920

1019

1118

1217

1316

1415

图3.6.2引脚结构图

♦D7~D0:

输出数据线(三态)

♦IN0~IN7:

8通道(路)模拟输入

♦ADDA、ADDB、ADDC:

通道地址

♦ALE:

通道地址锁存

♦START:

启动转换

♦EOC:

转换结束状态输出

♦OE:

输出允许(打开输出三态门)

♦CLK:

时钟输入(10KHz~1.2MHz

(3)ADC0809主要引脚说明:

输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线:

4条,IN0-IN7:

8条模拟量输入通道,

ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B和C为地址输入线,用于选通IN0-IN7上的一路模拟量输入。

通道选择表如下表所示。

选择的通道

IN0

1

IN1

IN3

IN4

IN5

IN6

IN7

数字量输出及控制线:

11条

ST为转换启动信号。

当ST上跳沿时,所有内部寄存器清零;

下跳沿时,开始进行A/D转换;

在转换期间,ST应保持低电平。

EOC为转换结束信号。

当EOC为高电平时,表明转换结束;

否则,表明正在进行A/D转换。

OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。

OE=1,输出转换得到的数据;

OE=0,输出数据线呈高阻状态。

D7-D0为数字量输出线。

CLK为时钟输入信号线。

因ADC0809的内部没有时钟电路,所需时钟信号必须由外界提供,通常使用频率为500KHZ,

VREF(+),VREF(-)为参考电压输入。

3.7ADC0809设计及工作原理:

ADC0809满量程为5V,则分辨率为5000mV/256=20mV,也就是说当模拟电压小于20mV,ADC就不能转换了,所以分辨率一般表示式为:

分辨率=Vref/2位数(单极性)

或分辨率=(V+ref-V-ref)/2位数(双极性)

求f采≥要2f信,也就是说必须在信号的一个周期内采集2个以上的数据,才能保证信号形态被还原(避免出现“假频”),这就是“最小采样”原理。

若f信=20kHz,则f采≥40kHz,其转换时间要求≤25µ

s。

工作原理:

START是转换启动信号,一个正脉冲过后A/D开始转换:

ALE是3位通道选择地址信号锁存信号。

当模拟量送至某一输入端,有3位地址信号选择,而地址信号由ALE锁存。

EOC是转换情况状态信号,当启动转换约100us后,EOC将产生一个负脉冲,以示转换结束。

在EOC的上升沿后,且输出使能信号ENABLE为高电平,则控制打开三态缓冲器,把转换好的8位数据送至总线。

至此ADC0809的一次转换结束

8位A/D转换器ADC0809为单极性输入、逐次逼近型A/D转换器,其原理图如图2.3所示:

图3.78位逐次逼近型A/D转换器ADC0809原理图

逐次逼近式ADC是应用最广泛的一种A/D转换方法。

逐次逼近式进行转换时,用一个逐次比较寄存器存放转换出来的数字量,转换结束时,将数字量送到缓冲器中。

由启动信号对逐次比较寄存器清零,使D/A转换器输出电压

也为零。

比较器输出高电平,转换开始。

同时,逐次逼近寄存器在控制电路控制下进行计数。

ADC0809控制逻辑是通过类似对分搜索的方法来控制逐次比较寄存器进行计数,即首先使最高位

经D/A转换后得到一个满量程一半的模拟电压

.

与输入电压

进行比较,如果

比较器得出1,则控制电路使逐次比较寄存器的

位保留1;

如果

比较器输出为0,则清除位

的1,然后使次高位

与上次的结果相加后经D/A转换得到新的

(满量程的3/4或1/4),再与

进行比较,决定保留还是清除位上的1,重复上述过程,直至

为止。

这样,经过8次比较后,8位逐次比较寄存器的状态即为一次A/D转换完成后所对应的数字量。

转换结束后,控制电路送出一个低电平作为结束信号,同时,将逐次比较寄存器中的数字量送入缓冲寄存器,从而得到数字量输出。

3.8采样保持器LF398设计:

LF398是一个专用的采样保持芯片,它具有很高的直流精度和较高的采样速率,器件的动态性能和保持性能可以通过合适的外接保持电容达到最佳。

LF398的内部结构如图所示;

图3.8.1LF398的内部电路结构

N1是输入缓冲放大器,N2是高输入阻抗射极输出器。

S为逻辑控制采样/保持开关,当S接通时,开始采样;

当S断开时,开始保持。

图3.8.2LF398电路图

脉冲变高,采样,S合上,脉冲变低,保持,S打开。

LF398的引脚功能为:

3、12脚:

正负电源输入端。

1脚:

Vi,模拟电压输入端。

11脚:

MCTR,逻辑控制输入端,高电平为采样,低电平为保持。

10脚:

MREF,逻辑控制电平参考端,一般接地。

8脚:

HOC,采样/保持电容接入端。

7脚:

OUT,采样/保持输出端。

如图3-5所示,被抽样信号从PAM-SIN输入,进入LF398的1脚Vi端,经内部输入缓冲放大器N1放大后送到模拟开关S,此时,将抽样脉冲作为S的控制信号,当LF398的11脚MCTR端为高电平时开关接通,为低电平时开关断开。

然后经过射极输出器N2输出比较理想的脉冲幅度调制信号。

K1为“平顶抽样”、“自然抽样”选择开关。

第四章:

各个部分的接口设计:

4.1LF398与ADC0809连接框图

将ADC0809的启动转换脉冲START连到LF398的引脚8上,作为采样控制脉冲,在脉冲的下降沿启动转换,在转换期间,LF398处于保持状态。

35

LF398

模入8

图4.1LF398与ADC0809连接图

4.2FPGA与ADC0809连接框图

FPGA_IO16VCC

(IO16,IO15,IO14)

ADINPUT(IO1……..IO8)

(0…..7)

FPGA_IO9

FPGAVCC

(IO10…IO13)ALE200UF

104

图4.2ADC0809与FPGA连接引脚图

FPGA_IO1…8接收ADC08098位数数据

FPGA_IO9接收ADC0809转换结束信号EOC

FPGA_IO10…12为ADC0809提供8路模拟信号开关的3位地址选通信号(ADDA…C)

FPGA_IO13为ADC0809提供地址锁存控制信号ALE:

高电平时把三个地址信号送入地址锁存器,并经译码器得到地址输出,以选择相应的模拟输入通道

FPGA_IO14为ADC0809提供输出允许控制信号OE:

电平由低变高时,打开输出锁存器,将转换结果的数字量送到数据总线上

FPGA_IO15为ADC0809提供启动控制信号START:

一个正脉冲过后A/D开始转换

FPGA_IO16为ADC0809提供时钟信号CLK

IN0….IN7:

8路模拟信号输入端口

Vref+和Vref-:

参考电压输入端口

4.3FPGA与单片机连接框图

串行接口(RS-232),串行接口是连接FPGA和PC机的一种简单方式。

RS-232有下列特性:

∙使用9针的"

DB-9"

插头(旧式计算机使用25针的"

DB-25"

插头).

∙允许全双工的双向通讯(也就是说计算机可以在接收数据的同时发送数据).

∙

最大可支持的传输速率为10KBytes/s.

DB-9插头

你可能已经在你的计算机背后见到过这种插头

它一共有9个引脚,但是最重要的3个引脚是:

引脚2:

RxD(接收数据).

引脚3:

TxD(发送数据).

引脚5:

GND(地).

仅使用3跟电缆,你就可以发送和接收数据.

数据以每次一位的方式传输;

每条线用来传输一个方向的数据。

由于计算机通常至少需要若干位数据,因此数据在发送之前先“串行化”。

通常是以8位数据为1组的。

先发送最低有效位,最后发送最高有效位。

对于RS-232来说,是这样处理的:

1.

串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等)

2.

当没有数据传输的时候,发送端向数据线上发送"

1"

3.

每传输一个字节之前,发送端先发送一个"

0"

来表示传输已经开始。

这样接收端便可以知道有数据到来了。

4.

开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步

5.

每次传输完成一个字节之后,都在其后发送一个停止位("

)

图4.3FPGA与单片机连接框图

4.4FPGA与RAM连接框图

图4.4FPGA与RAM连接框图

第五章软件设计

系统软件的总体设计

需要分析的数据

SIN

SOUT

图5总体设计框图

5.1采样控制模块:

用状态机对ADC0809进行采样控制首先必须了解其工作时序,然后据此做出状态图,最后写出相应的VHDL代码。

(1)ADC0809时序分析

ADC0809的工作时序如下图3.3所示。

时序图中,START为启动转换信号,高电平有效;

ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;

EOC是转换情况状态信号,当启动转换约100us后,EOC产生一个负脉冲,以示转换结束;

在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

至此ADC0809的一次转换结束了.

ADC0809工作时序:

CLOCK

ADDA

ADDC

地址锁存启动

ALE/START

EOC

转换时间

OE

D0—D7

图5.1ADC0809工作时序图

由时序图知ADC0809的工作过程如下:

♦送通道地址,以选择要转换的模拟输入;

♦锁存通道地址到内部地址锁存器;

♦启动A/D变换;

♦判断转换是否结束;

♦读转换结果

(2)状态设计

根据ADC0809的工作时序图做出状态图,在对其采样控制电路中定义了七个状态:

初始化状态、模拟信号选通状态、启动A/D转换状态、启动采样状态、采样停止状态、输出数据状态、数据锁存状态。

reset

图3.4控制ADC0809采样状态图

如上图3.4所示,为控制ADC0809采样状态图,图中的ST0,ST1,ST2,ST3,ST4,ST5,ST6为设计定义的七种状态类型,与上面的七种状态一一对应。

在ST0状态中的RESET为复位信号,在此状态下输出ALE<

='

0'

;

START<

OE<

LOCK<

表示对ADC0809的初始化。

在ST1状态下输出ALE<

1'

其中ALE上升沿有效,此状态下模拟信号输入选通。

在ST2状态下,输出ALE<

START信号有效,启动A/D转换。

在ST3状态下,输出ALE<

在此状态中检测EOC的下降沿,如果EOC的下降沿来了则启动采样,否则,等待启动采样。

在ST4状态下,输出ALE<

在此状态中检测EOC的上升沿,如果EOC的上升沿来了则停止采样,否则,采样周期中等待。

在ST5状态下,输出ALE<

OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

在ST6状态下,输出ALE<

LOCK信号有效,将输出的数据锁存,至此一次完整地采样控制结束。

(3)进程设计

在做好状态图之后,进行进程的设计,本设计采用三进程进行状态机设计,如下图3.5所示:

LOCK1

图3.5采样状态机结构图

如上图3.5所示:

程序含三个进程,clock进程是时序进程,它在时钟信号CLK的驱动下,不断将nest_state中的内容赋给current_state,并由此信号将状态变量传输给组合进程pro。

组合进程pro有两个功能:

①状态译码功能,即根据从current_state信号获得的状态变量,以及来自ADC0809的状态线信号EOC,决定下一状态的转移方向,即确定此态的状态变量;

②采样控制功能,即根据current_state中的状态变量确定对0809的控制信号线ALE、START、OE等输出相应的控制信号,当采样结束后还要通过LOCK向锁存器进程latch发出锁存信号,以便将由0809的D[7..0]数据输出口的8位转换数据锁存起来,

至此ADC0809的一次转换结束。

5.2分频模块设计

由于硬件电路的时钟频率为32MHz,频率太高,在做下载是看不到预想的结果,故采用此模块,将频率变低已达到预期的效果。

另外,以计数的方式设计了一个8位二进制的输出来替代ADC0809的经模数转换后的8位二进制输出,即一个输入时钟经两个不同的分频之后为各所用,分频模块程序如下:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitydivis

Port(clk:

instd_logic;

--系统时钟

clk1:

outstd_logic;

--分频后的时钟输出

shuout:

outstd_logic_vector(7downto0));

--8位二进制输出端

endd

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 直接 控制 ADC0809 模拟 信号 进行 采样 DOC

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx