LC串联谐振电路重要特性Word文档下载推荐.docx

LC串联谐振电路重要特性Word文档下载推荐.docx

- 文档编号:20300210

- 上传时间:2023-01-21

- 格式:DOCX

- 页数:8

- 大小:74.71KB

LC串联谐振电路重要特性Word文档下载推荐.docx

《LC串联谐振电路重要特性Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《LC串联谐振电路重要特性Word文档下载推荐.docx(8页珍藏版)》请在冰豆网上搜索。

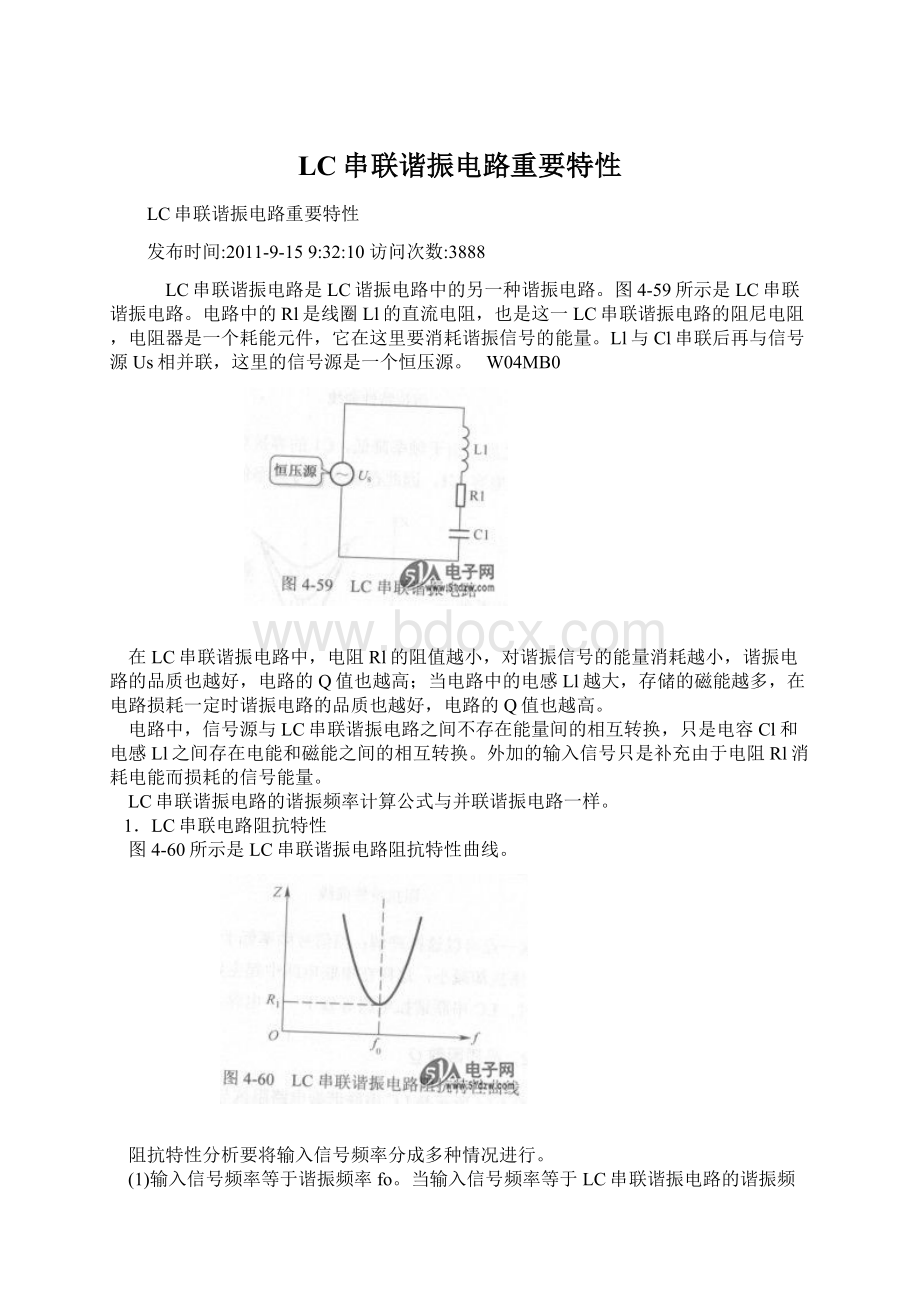

1.LC串联电路阻抗特性

图4-60所示是LC串联谐振电路阻抗特性曲线。

阻抗特性分析要将输入信号频率分成多种情况进行。

(1)输入信号频率等于谐振频率fo。

当输入信号频率等于LC串联谐振电路的谐振频率fo时,电路发生串联谐振,串联谐振时电路的阻抗最小且为纯阻性(不为容性也不为感性),如图4-61所示,其值为R1(纯阻性)。

当信导频率偏离LC谐振电路的谐振频率时,电路的阻抗要增大,且频率偏离的量越大,电路的阻抗就越大,这一点恰好是与LC并联谐振电路相反的。

要记住:

串联谐振时电路的阻抗最小。

(2)输入信号频率高于谐振频率fo。

当输入信号频率高于谐振频率时,LC串联谐振电路为感性,相当于一个电感(电感量大小不等于L1),如图4-62所示。

这一点可以这样理解:

在Ll和Cl串联电路中,当信号频率高于谐振频率之后,由于频率升高,Cl的容抗减小,而Ll的感抗却增大,在串联电路中起主要作用的是阻抗大的一个元件,’这样Ll起主要作用,因此在输入信号频率高于谐振频率之后,LC串联谐振电路等效于一个电感。

(3)输入信号频率低于谐振频率五。

当输入信号频率低于谐振频率时,LC串联谐振电路为容性,相当于一个电容(容量大小不等于C1),如图4-63所示。

当信号频率低于谐振频率之后,由于频率降低,Cl的容抗增大,而Ll的感抗却减小,这样在串联电路中起主要作用的是电容Cl,因此在输入信号频率低于谐振频率时,LC串联谐振电路等效于一个电容。

2.品质因数Q

图4-64所示是LC串联谐振电路阻抗与Q值之间关系的示意图。

图中三条阻抗曲线中,Qi曲线的品质因数最大,Q2曲线其次,Q3曲线最小,Q值越大曲线越尖锐,谐振时的电路阻抗越小,流过串联谐振电路的信号电流越大。

LC串联谐振电路的频带特性与并联谐振电路是一样的,也是谐振电路的Q值越大,频带越窄,反之则越宽。

锁相环CC4046为数字PLL,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO产生50%占空比的方波,输出电平可与TTL电平或CMOS电平兼容。

同时,它还具有相位锁定状态指示功能。

信号输入端:

允许输入0.1V左右的小信号或方波,经A1放大和整形,提供满足PD要求的方波。

PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率PDI由异或门构成,具有三角形鉴相特性。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率。

通常输入信噪比以及固有频差较小时采用PDI,输入信噪比较高或固有频差较大时,采用PDⅡ。

R1、R2、C确定VCO频率范围。

R1控制最高频率,R2控制最低频率。

R2=∞时,最低频率为零。

无输入信号时,PDⅡ将VCO调整到最低频率。

锁相环CD4046的一个重要功能是:

内部压迫、控振荡器的输出信号从第4脚输出后引至第3脚输入,与从第14脚输入的外部基准频率信号和相位的比较。

当两者频率相同时同,压控振荡器的频率能自动调整,直到与基准频率相同。

CD4046引脚图

AbsoluteMaximumRatings绝对最大额定值:

DCSupplyVoltage直流供电电压(VDD)−0.5to+18VDC

InputVoltage输入电压(VIN)−0.5toVDD+0.5VDC

StorageTemperatureRange储存温度范围(TS)−65℃to+150℃

PowerDissipation功耗(PD)

Dual-In-Line普通双列封装700mW

SmallOutline小外形封装500mW

焊接温度(TL)(焊接10秒)260℃

RecommendedOperatingConditions建议操作条件:

DCSupplyVoltage直流供电电压(VDD)3to15VDC

InputVoltage输入电压(VIN)0toVDDVDC

OperatingTemperatureRange工作温度范围(TA)−55℃to+125℃

引脚号名称功能

PH1114相位比较器输入端(基准信号输入),相位比较器输入信号,输入允许将0.1V左右的小信号或方波信号在内部放大并再经过整形电路后,输出至相位比较器。

PH123相位比较器输入端(比较信号输入)通常PD来自VCO的参考信号。

PH012PDⅠ输出端相位比较器1输出的相位差信号,它采用异或门结构,即鉴相特性为。

PH0213PDⅡ输出端相位比较器Ⅱ的输出端,它采用,上升沿控制逻辑。

PH031输出端(相位脉冲输出)相位比较器2输出的相位差信号,为上升沿控制逻辑。

环路人锁时为高电平,环路失锁时为低电平

VC019压控振荡器的控制端。

VC004压控振荡器输出端

INH5VCO禁止端,1有效控制信号输入,高电平时禁止,低电平时允许压控振荡器工作。

R111VCO外接电阻R1

R212VCO外接电阻R2

C16,7并接振荡电容C1,以控制VCO的振荡频率。

DEM010解调信号输出端

15ap内部独立的齐纳稳压二极管负极。

<

>

CD4046引脚功能说明介绍:

DCElectricalCharacteristics直流电气特性:

Symbol符号Parameter参数Conditions条件−55℃+25℃+125℃Units单位

最小最大最小典型最大最小最大

IDDQuiescentDeviceCurrent静态电流Pin5=VDD,Pin14=VDD,Pin3,9=VSS

VDD=5V50.0055150μA

VDD=10V100.0110300

VDD=15V200.01520600

Pin5=VDD,Pin14=Open,Pin3,9=VSS

VDD=5V45535185μA

VDD=10V45020350650

VDD=15V1200509001500

VOLLOWLevelOutputVoltage输出低电平电压VDD=5V0.0500.050.05V

VDD=10V0.0500.050.05

VDD=15V0.0500.050.05

VOHHIGHLevelOutputVoltage输出高电平电压VDD=5V4.954.9554.95V

VDD=10V9.959.95109.95

VDD=15V14.9514.951514.95

VIL输入低电平电压比较器和信号VDD=5V,VO=0.5Vor4.5V1.52.251.51.5V

VDD=10V,VO=1Vor9V3.04.53.03.0

VDD=15V,VO=1.5Vor13.5V4.06.254.04.0

VIH输入高电平电压比较器和信号VDD=5V,VO=0.5Vor4.5V3.53.52.753.5V

VDD=10V,VO=1Vor9V7.07.05.57.0

VDD=15V,VO=1.5Vor13.5V11.011.08.2511.0

IOLLOWLevelOutputCurrent输出低电平电流(Note4)VDD=5V,VO=0.4V0.640.510.880.36mA

VDD=10V,VO=0.5V1.61.32.250.9

VDD=15V,VO=1.5V4.23.48.82.4

IOHHIGHLevelOutputCurrent输出高电平电流(Note4)VDD=5V,VO=4.6V−0.64−0.51−0.88−0.36mA

VDD=10V,VO=9.5V−1.6−1.3−2.25−0.9

VDD=15V,VO=13.5V−4.2−3.4−8.8−2.4

IINInputCurrent输入电流AllInputsExceptSignalInput

VDD=15V,VIN=0V−0.1−10−5−0.1−1.0μA

VDD=15V,VIN=15V0.110−50.11.0

CINInputCapacitance输入电容AnyInput(Note3)7.5pF

PTTotalPowerDissipation总功率耗散fo=10kHz,R1=1MΩ,R2=∞,VCOIN=VCC/2mW

VDD=5V0.07

VDD=10V0.6

VDD=15V2.4

ACElectricalCharacteristics交流电气特性:

Symbol符号Parameter参数Conditions条件最小典型最大Units单位

VCOSECTION

IDDOperatingCurrent工作电流fo=10kHz,R1=1MΩ,R2=∞,VCOIN=VCC/2

VDD=5V20μA

VDD=10V90

VDD=15V200

fMAXMaximumOperatingFrequency最高工作频率C1=50pF,R1=10kΩ,R2=∞,VCOIN=VDD

VDD=5V0.40.8MHz

VDD=10V0.61.2

VDD=15V1.01.6

Linearity线性VCOIN=2.5V±

0.3V,R1≥10kΩ,VDD=5V1%

VCOIN=5V±

2.5V,R1≥400kΩ,VDD=10V1

VCOIN=7.5V±

5V,R1≥1MΩ,VDD=15V1

Temperature-FrequencyStabilityNoFrequencyOffset,fMIN=0%/℃<

5c1/f.VDDR2=∞

VDD=5V0.12–0.24%/℃

VDD=10V0.04–0.08

VDD=15V0.015–0.03

FrequencyOffset,频偏fMIN≠0VDD=5V0.06–0.12%/℃

VDD=10V0.05–0.1

VDD=15V0.03–0.06

VCOINInputResistance输入电阻VDD=5V106MΩ

VDD=10V106

VDD=15V106

VCOOutputDutyCycle输出占空比VDD=5V50%

VDD=10V50

VDD=15V50

tTHLVCOOutputTransitionTimeVCO的输出过渡期VDD=5V90200ns

VDD=10V50100

VDD=15V4580

PHASECOMPARATORSSECTION

RIN信号输入输入电阻 VDD=5V13MΩ

VDD=10V0.20.7

VDD=15V0.10.3

ComparatorInput比较器输入VDD=5V106MΩ

AC-CoupledSignalInputVoltageSensitivityAC耦合信号输入电压灵敏度CSERIES=1000pFf=50kHz

VDD=5V200400mV

VDD=10V400800

VDD=15V7001400

VCOIN−VDEMOffsetVoltage偏移电压RS≥10kΩ,VDD=5V1.502.2V

RS≥10kΩ,VDD=10V1.502.2

RS≥50kΩ,VDD=15V1.502.2

Linearity线性RS≥50kΩ

VCOIN=2.5V±

0.3V,VDD=5V0.1%

2.5V,VDD=10V0.6

5V,VDD=15V0.8

ZENERDIODE

VZZenerDiodeVoltage稳压二极管电压IZ=50μA6.37.07.7V

RZ>

ZenerDynamicResistance稳压动态电阻<

IZ=1mA100Ω

相比较状态图

ahref='

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- LC 串联 谐振 电路 重要 特性

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx