ALU实验报告.docx

ALU实验报告.docx

- 文档编号:20128712

- 上传时间:2023-04-25

- 格式:DOCX

- 页数:43

- 大小:1.22MB

ALU实验报告.docx

《ALU实验报告.docx》由会员分享,可在线阅读,更多相关《ALU实验报告.docx(43页珍藏版)》请在冰豆网上搜索。

ALU实验报告

ALU实验设计报告

班号:

28001020

组员:

方艳梅2801311032周秋彤2800102005

一、实验目的

(1)掌握ALU的一般结构设计

(2)掌握复杂的时序电路设计

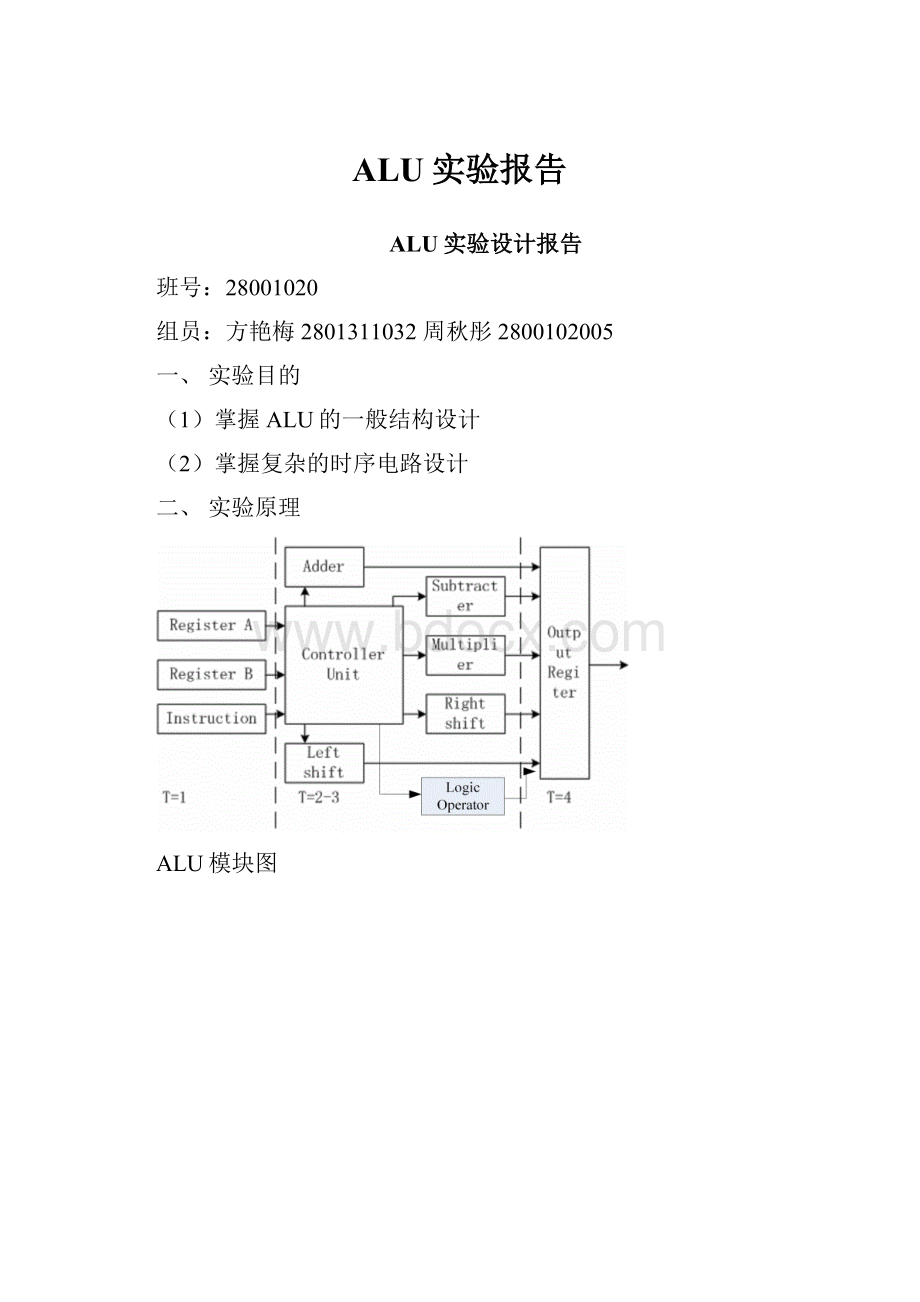

二、实验原理

ALU模块图

ALU结构图

加法器结构图:

构成加法器的全加器:

加法器结构图:

减法器机构图:

乘法器算法分析图:

乘法器结构图:

逻辑移位结构图:

逻辑运算结构图:

ALU共有五个输入端,一个输出端,a,b代表要处理的数据,为四比特,c为控制编码,为三比特,000代表需要ALU处理的这两个数据相加,001代表需要处理的是这两个数据想减,010代表需要处理的是这两个数据相乘,011代表要对a与b的后三位进行逻辑运算,而逻辑运算的类型由a与b的第一位共同组成的一个二进制编码确定,00代表逻辑与,01代表逻辑或,10代表逻辑非,11代表逻辑异或,100代表对a进行逻辑移位,移位方式由b的第一位确定,1代表要对a进行左移,0代表要对a进行逻辑右移,而b的后三位决定要对a进行移位操作的位数,如b为1010代表要对a左移两位,其余的c无效。

rst为复位控制,是一比特数据,且低电平使能。

en为使能控制,也是一比特数据,为高电平使能。

dout为按照输入要求操作后得出的数据,为八比特数据。

在数据输入ALU后,按照c的编码选择相应的模块对a与b的值进行处理,最后通过多路选通器,对输出进行控制,输出需要输出的模块。

整个ALU计算过程需要四个时钟周期,其中输入占一个周期,计算占两个周期,输出占一个周期。

在设计中,为了达到节能的目的,对每个模块定义了三个状态,开始计算(s0),计算中并等待下一次数据输入(s1),关闭(s2),即达到使用哪个模块就开启哪个模块的目的,算然增加了硬件开销,但大大地节约了能源。

三、实验内容

代码如下:

ALU:

----------------------------------------------------------------------------------

--Company:

--Engineer:

--

--CreateDate:

11:

28:

5812/15/2009

--DesignName:

--ModuleName:

alu-Behavioral

--ProjectName:

--TargetDevices:

--Toolversions:

--Description:

--

--Dependencies:

--

--Revision:

--Revision0.01-FileCreated

--AdditionalComments:

--

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

----Uncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entityaluis

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);c:

instd_logic_vector(2downto0);dout:

outstd_logic_vector(7downto0));

endalu;

architectureBehavioralofaluis

componentcontroller

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);c:

instd_logic_vector(2downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

signala_r,b_r:

std_logic_vector(3downto0);

signalc_r:

std_logic_vector(2downto0);

signaldout_r:

std_logic_vector(7downto0);

begin

inst_controller:

controllerportmap(clk=>clk,rst=>rst,en=>en,a=>a_r,b=>b_r,c=>c_r,dout=>dout_r);

process(rst,clk)

begin

ifrst='1'then

a_r<="0000";

b_r<="0000";

c_r<="000";

dout<="00000000";

elsifclk'eventandclk='1'then

ifen='1'then

a_r<=a;

b_r<=b;

c_r<=c;

dout<=dout_r;

endif;

endif;

endprocess;

endBehavioral;

----------------------------------------------------------------------------------

运算控制模块

----------------------------------------------------------------------------------

--Company:

--Engineer:

--

--CreateDate:

11:

17:

3412/15/2009

--DesignName:

--ModuleName:

controller-Behavioral

--ProjectName:

--TargetDevices:

--Toolversions:

--Description:

--

--Dependencies:

--

--Revision:

--Revision0.01-FileCreated

--AdditionalComments:

--

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

----Uncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entitycontrolleris

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);c:

instd_logic_vector(2downto0);dout:

outstd_logic_vector(7downto0));

endcontroller;

architectureBehavioralofcontrolleris

componentadder

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

componentsubtracter

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

componentmultiplier

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

componentlogic

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

componentshift

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endcomponent;

signalrst_adder:

std_logic;

signaladder_dout:

std_logic_vector(7downto0);

signalrst_subtracter:

std_logic;

signalsubtracter_dout:

std_logic_vector(7downto0);

signalrst_multiplier:

std_logic;

signalmultiplier_dout:

std_logic_vector(7downto0);

signalrst_logic:

std_logic;

signallogic_dout:

std_logic_vector(7downto0);

signalrst_shift:

std_logic;

signalshift_dout:

std_logic_vector(7downto0);

signalc_b1,c_b2:

std_logic_vector(2downto0);

typestateis(s0,s1,s2);

signaladder_s,adder_s_p,subtracter_s,subtracter_s_p,multiplier_s,multiplier_s_p,logic_s,logic_s_p,shift_s,shift_s_p:

state;

begin

inst_adder:

adderportmap(clk=>clk,rst=>rst_adder,en=>en,a=>a,b=>b,dout=>adder_dout);

inst_subtracter:

subtracterportmap(clk=>clk,rst=>rst_subtracter,en=>en,a=>a,b=>b,dout=>subtracter_dout);

inst_multiplier:

multiplierportmap(clk=>clk,rst=>rst_multiplier,en=>en,a=>a,b=>b,dout=>multiplier_dout);

inst_logic:

logicportmap(clk=>clk,rst=>rst_logic,en=>en,a=>a,b=>b,dout=>logic_dout);

inst_shift:

shiftportmap(clk=>clk,rst=>rst_shift,en=>en,a=>a,b=>b,dout=>shift_dout);

process(rst,clk)

begin

ifrst='1'then

c_b1<="000";

c_b2<="000";

elsifclk'eventandclk='1'then

ifen='1'then

c_b1<=c;

c_b2<=c_b1;

endif;

endif;

endprocess;

process(rst,clk)

begin

ifrst='1'then

adder_s_p<=s0;

subtracter_s_p<=s0;

multiplier_s_p<=s0;

logic_s_p<=s0;

shift_s_p<=s0;

elsifclk'eventandclk='1'then

ifen='1'then

adder_s_p<=adder_s;

subtracter_s_p<=subtracter_s;

multiplier_s_p<=multiplier_s;

logic_s_p<=logic_s;

shift_s_p<=shift_s;

endif;

endif;

endprocess;

process(adder_dout,subtracter_dout,multiplier_dout,logic_dout,shift_dout,c_b2)

begin

casec_b2is

when"000"=>

dout<=adder_dout;

when"001"=>

dout<=subtracter_dout;

when"010"=>

dout<=multiplier_dout;

when"011"=>

dout<=logic_dout;

when"100"=>

dout<=shift_dout;

whenothers=>

dout<="00000000";

endcase;

endprocess;

process(c,adder_s_p)

begin

caseadder_s_pis

whens0=>

ifc="000"then

rst_adder<='0';

adder_s<=s1;

else

rst_adder<='1';

adder_s<=s0;

endif;

whens1=>

ifc="000"then

rst_adder<='0';

adder_s<=s1;

else

rst_adder<='0';

adder_s<=s2;

endif;

whens2=>

ifc="000"then

rst_adder<='0';

adder_s<=s1;

else

rst_adder<='0';

adder_s<=s0;

endif;

whenothers=>

null;

endcase;

endprocess;

process(c,subtracter_s_p)

begin

casesubtracter_s_pis

whens0=>

ifc="001"then

rst_subtracter<='0';

subtracter_s<=s1;

else

rst_subtracter<='1';

subtracter_s<=s0;

endif;

whens1=>

ifc="001"then

rst_subtracter<='0';

subtracter_s<=s1;

else

rst_subtracter<='0';

subtracter_s<=s2;

endif;

whens2=>

ifc="001"then

rst_subtracter<='0';

subtracter_s<=s1;

else

rst_subtracter<='0';

subtracter_s<=s0;

endif;

whenothers=>

null;

endcase;

endprocess;

process(c,multiplier_s_p)

begin

casemultiplier_s_pis

whens0=>

ifc="010"then

rst_multiplier<='0';

multiplier_s<=s1;

else

rst_multiplier<='1';

multiplier_s<=s0;

endif;

whens1=>

ifc="010"then

rst_multiplier<='0';

multiplier_s<=s1;

else

rst_multiplier<='0';

multiplier_s<=s2;

endif;

whens2=>

ifc="010"then

rst_multiplier<='0';

multiplier_s<=s1;

else

rst_multiplier<='0';

multiplier_s<=s0;

endif;

whenothers=>

null;

endcase;

endprocess;

process(c,logic_s_p)

begin

caselogic_s_pis

whens0=>

ifc="011"then

rst_logic<='0';

logic_s<=s1;

else

rst_logic<='1';

logic_s<=s0;

endif;

whens1=>

ifc="011"then

rst_logic<='0';

logic_s<=s1;

else

rst_logic<='0';

logic_s<=s2;

endif;

whens2=>

ifc="011"then

rst_logic<='0';

logic_s<=s1;

else

rst_logic<='0';

logic_s<=s0;

endif;

whenothers=>

null;

endcase;

endprocess;

process(c,shift_s_p)

begin

caseshift_s_pis

whens0=>

ifc="100"then

rst_shift<='0';

shift_s<=s1;

else

rst_shift<='1';

shift_s<=s0;

endif;

whens1=>

ifc="100"then

rst_shift<='0';

shift_s<=s1;

else

rst_shift<='0';

shift_s<=s2;

endif;

whens2=>

ifc="100"then

rst_shift<='0';

shift_s<=s1;

else

rst_shift<='0';

shift_s<=s0;

endif;

whenothers=>

null;

endcase;

endprocess;

endBehavioral;

加法器:

--Company:

--Engineer:

--

--CreateDate:

10:

48:

3012/15/2009

--DesignName:

--ModuleName:

adder-Behavioral

--ProjectName:

--TargetDevices:

--Toolversions:

--Description:

--

--Dependencies:

--

--Revision:

--Revision0.01-FileCreated

--AdditionalComments:

--

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

----Uncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entityadderis

port(clk,rst,en:

instd_logic;a,b:

instd_logic_vector(3downto0);dout:

outstd_logic_vector(7downto0));

endadder;

architectureBehavioralofadderis

componentfull_adder

port(a,b,cin:

instd_logic;s,co:

outstd_logic);

endcomponent;

signala2_r,a3_r,a4_r:

std_logic;

signalb2_r,b3_r,b4_r:

std_logic;

signald0_r,d1_r:

std_logic;

signalc1_2_r:

std_logic;

signaldout_b:

std_logic_vector(4downto0);

signalc_b:

std_logic_vector(4downto0);

begin

process(rst,clk)

begin

ifrst='1'then

a2_r<='0';

a3_r<='0';

a4_r<='0';

b2_r<='0';

b3_r<='0';

b4_r<='0';

c1_2_r<='0';

d0_r<='0';

d1_r<='0';

elsifclk'eventandclk='1'then

a2_r<=a

(2);

a3_r<=a(3);

a4_r<=

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ALU 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#全自动电容电感测试仪.docx

#全自动电容电感测试仪.docx