VerilogLED数码管驱动电路设计Word文档下载推荐.docx

VerilogLED数码管驱动电路设计Word文档下载推荐.docx

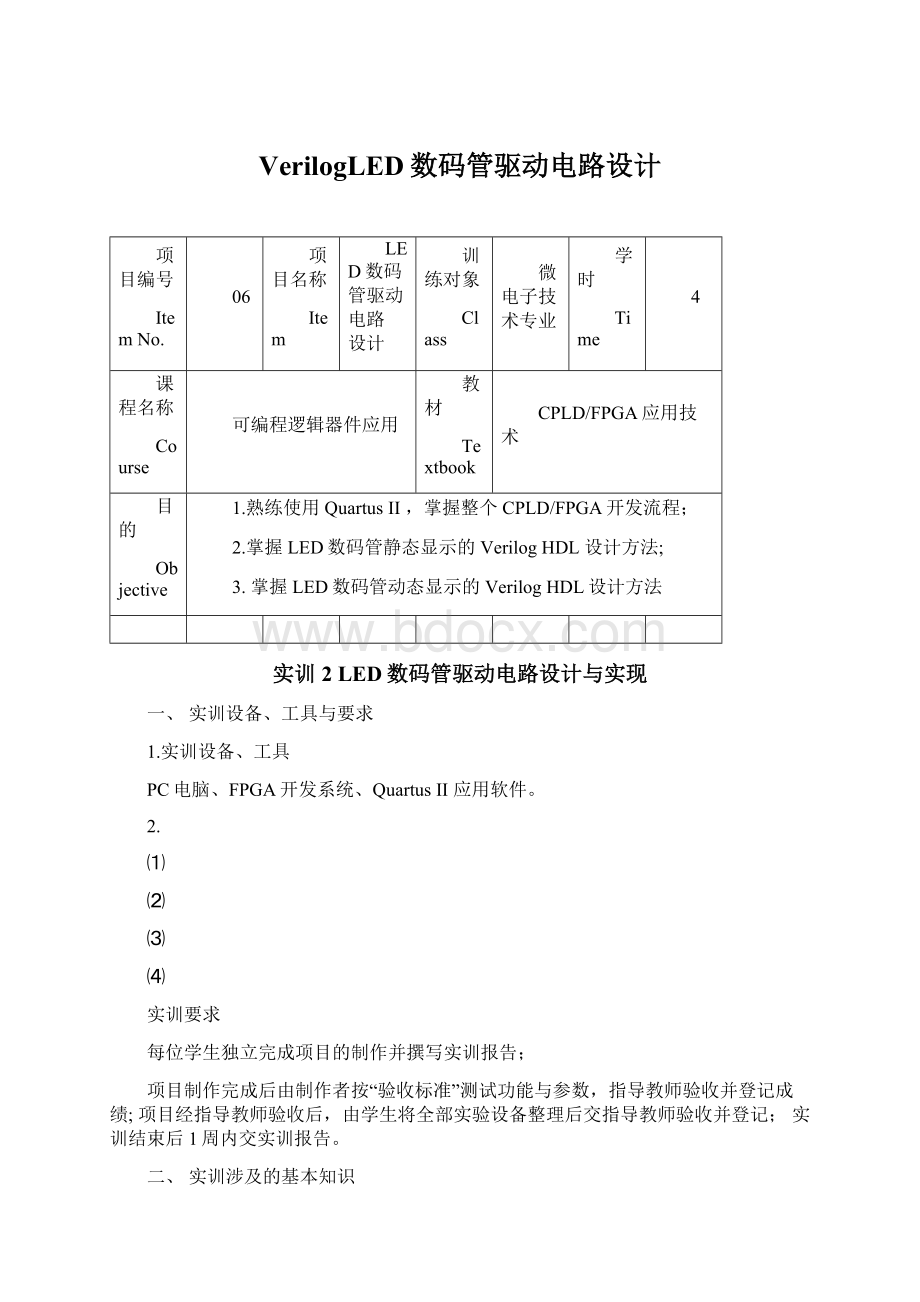

- 文档编号:20034097

- 上传时间:2023-01-16

- 格式:DOCX

- 页数:12

- 大小:275.59KB

VerilogLED数码管驱动电路设计Word文档下载推荐.docx

《VerilogLED数码管驱动电路设计Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《VerilogLED数码管驱动电路设计Word文档下载推荐.docx(12页珍藏版)》请在冰豆网上搜索。

⑴

⑵

⑶

⑷

实训要求

每位学生独立完成项目的制作并撰写实训报告;

项目制作完成后由制作者按“验收标准”测试功能与参数,指导教师验收并登记成绩;

项目经指导教师验收后,由学生将全部实验设备整理后交指导教师验收并登记;

实训结束后1周内交实训报告。

二、实训涉及的基本知识

1.请画出七段LED数码管显示电路的输入输出结构

2.列表描述共阴七段数码显示电路的输入输出关系和显示结果?

七段数码管显示电路输入

七段数码管显示电路输出

LED显示字形

in3in2in1in0

gfedcba

1

0000

0111111

0001

0000110

0010

1011011

2

0011

1001111

3

0100

1100110

0101

1101101

5

0110

1111100

6

0111

0000111

7

1000

1111111

8

1001

1100111

9

三、实训综合电路(七段译码器电路框图)

动态显示电路框图:

cnt:

u1

模10计数单个数码管显示电路框图:

四、实训步骤

1.阅读AlteraCyclongll开发系统用户手册,画出七段数码管的电路图和连接引脚。

信

号

clk

rst

led[6]

led[5]

led[4]

led[3]

led[2]

led[1]

led[0]

scan[3]

scan[2]

scan[1]

scan[0]

引脚

89

90

73

74

75

83

85

86

87

97

100

102

104

值

153

81

82

96

98

2.设计应用工程,将十进制的0-9的BCD码转换成七段数码管的显示码(组合逻辑电路)

七段LED数码管显示电路的Verilog代码:

moduleqiduan_0(cnt,led);

[3:

0]ent;

[6:

0]led;

always@(cnt)

begin

case(cnt)

4'

b0001:

led=7'

b0000110;

b0010:

b1011011;

b0011:

b1001111;

b0100:

b1100110;

b0101:

b1101101;

b0110:

b1111100;

b0111:

b0000111;

b1000:

b1111111;

b1001:

b1101111;

b1010:

b1110111;

default:

b0111111;

endease

end

endmodule

3.设计应用工程,四个数码管依次静态显示“1”、“2”、“3”、“4”;

七段LED数码管显示电路仿真波形图:

led<

=11'

b00101011011;

elseif(a==2'

b10)

b01001001111;

else

b10001100110;

4.设计应用工程,单个数码管完成从模10计数功能;

分频器:

modulefenpin25(clk,rst,clk_1hz);

inputinputoutputalways@(posedgeclkorposedgerst)begin

if(rst==1'

b1)

cnt<

=24'

d0;

elseif(cnt==13107119)begincnt<

clk_1hz<

=~clk_1hz;

end

ent<

=ent+1;

endendmodule

十进制计数器:

modulecnt10(rst,clk,cnt);

inputoutputalways@(posedgeclk)begin

b0)cnt<

=4'

b000;

elseif(cnt==4'

d9)cnt<

=cnt+1;

十进制计数器仿真波形图:

endcase

LED译码器仿真波形图:

Vtlu*

635

0cat

BOC

0l*d

BOil

0scan

A[

)pz

曲.9nz

400ns

T

60.0ns

SO.0ns

J

S,35ns

-1

;

two

)X0001X0010

XOOHX0100

X0101X0110

X0111XIDE■

Join

iiXooooiioXioiiaiiXiooiniXiiooiioXiioiioiXiiiiiooXooooiiiXiiiiiii.

[1]

顶层电路VerilogHDL代码:

modulecnt10led(rst,clk,led,scan);

inputinputoutputoutputwire

wire

rst;

elk;

[3:

0]scan;

fenpin25cnt10

qiduan

u0(.clk(clk),.rst(rst),.clk_1hz(clk_1hz));

u1(.clk(clk_1hz),.rst(rst),.cnt(cnt));

u2(.cnt(cnt),.led(led),.scan(scan));

框图:

CIK

rsi

0]

tanI3..Cl]

5.设计应用工程,LED数码管动态显示

分频器:

modulediv24(clk,rst,sclk);

inputrst;

inputclk;

1,2,3,4”,完成VerilogHDL设计;

outputsclk;

wiresclk;

[23:

0]cnt;

reg

always@(posedgeclk)begin

cnt<

=cnt+1;

assignsclk=cnt[23];

二位计数器:

modulecnt2(sclk,rst,cnt);

inputinputoutput

sclk;

rst;

[1:

[1:

always@(posedgesclk)begin

if(rst==1'

=2'

b00;

二位计数器仿真波形图:

Value£

S.35I

40

田cnt

B130

A1

e4

sclk

40.0TLE

QO.0Hi

SOpHE

psns

S.35iLM

JI_

厂srrIDXLiX00X0111厂丽'

00

LED译码器:

moduleledyima(cnt,led);

input[1:

output[10:

[10:

2'

b00:

led=11'

b00010000110;

b01:

b10:

b11:

moduleled_0(clk,rst,led);

input

outputwiresclk;

wire[1:

div24u0(.clk(clk),.rst(rst),.sclk(sclk));

cnt2u1(.sclk(sclk),.rst(rst),.cnt(cnt));

ledyimau2(.cnt(cnt),.led(led));

五、验收标准

1)程序运行正常;

2)仿真功能和下载功能正常;

六、扩展与改进

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VerilogLED 数码管 驱动 电路设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx