EDAWord文档格式.docx

EDAWord文档格式.docx

- 文档编号:19879691

- 上传时间:2023-01-11

- 格式:DOCX

- 页数:16

- 大小:235.91KB

EDAWord文档格式.docx

《EDAWord文档格式.docx》由会员分享,可在线阅读,更多相关《EDAWord文档格式.docx(16页珍藏版)》请在冰豆网上搜索。

11"

=d;

WHENOTHERS=>

='

0'

;

ENDCASE;

ENDPROCESS;

ENDbehave3;

双2选1多路选择器

ENTITYmuxkIS

PORT(a1,a2,a3:

instd_logic;

s0,s1:

outy:

ENDENTITYmuxk;

ARCHITECTUREbehaveOFmuxkIS

SIGNALtmp:

std_logic;

SIGNALoutx:

BEGIN

Pr1:

PROCESS(a2,a3,s0)BEGIN

CASEs0IS

WHEN'

tmp<

=a2;

1'

=a3;

Pr2:

PROCESS(a1,tmp,s1)BEGIN

CASEs1IS

outx<

=a1;

=tmp;

outy<

=outx;

ENDbehave;

3-4将3-20程序的计数器改为12进制计数器,程序用例3-21的方式表述,并且将复位RST改为同步清0控制,加载信号LOAD改为异步控制方式。

讨论例3-20与例3-21的异同点。

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT12IS

PORT(CLK,RST,EN,LOAD:

INSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREbehavOFCNT12IS

SIGNALQ:

STD_LOGIC_VECTOR(3DOWNTO0);

REG:

PROCESS(CLK,LOAD)

IFLOAD='

THENQ:

=DATA;

ELSIFCLK'

EVENTANDCLK='

THEN

IFEN='

IF(RST='

)THENQ:

=(OTHERS=>

'

);

ELSE

IFQ<

11THENQ:

=Q+1;

ELSEQ:

=(OTHERS=>

ENDIF;

COM:

PROCESS(Q)

IFQ="

1011"

THENCOUT<

ELSECOUT<

ENDIF;

DOUT<

=Q;

ENDbehav;

3-5设计含有异步清零和计数使能的16位二进制加减法可控计数器

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

USEieee.std_logic_arith.all;

ENTITYex3_5IS

port(clk:

clr,en,control:

cnt:

outstd_logic_vector(15downto0));

ARCHITECTUREbhvOFex3_5IS

signalcnt_tmp:

std_logic_vector(15downto0);

process(clk,clr)begin

ifclr='

then

cnt_tmp<

=(others=>

elsif(rising_edge(clk))then

ifen='

ifcontrol='

thencnt_tmp<

=cnt_tmp+1;

elsecnt_tmp<

=cnt_tmp-1;

endif;

endprocess;

cnt<

=cnt_tmp;

END;

例5.2偶数分频电路(8分频)

libraryieee;

useieee.std_logic_1164.all;

entityfredevider8is

port(clkin:

clkout:

outstd_logic);

end;

architecturebehoffredevider8is

constantN:

integer:

=3;

signalcounter:

integerrange0toN;

signalclk:

begin

process(clkin)

begin

ifrising_edge(clkin)then

ifcounter=Nthen

counter<

=0;

clk<

=notclk;

elsecounter<

=counter+1;

endif;

clkout<

=clk;

例5.2偶数分频电路(8分频

5.2.6三态总线电路设计

5.4并行赋值语句讨论

并行赋值语句也包含类似进程的顺序语句特性。

ENTITY实体名IS

[GENERIC(参数名:

数据类型);

]

PORT(端口表);

ENDENTITY实体名;

描述

ENTITYTriBuff1IS

PORT(OE,Datain:

Dataout:

OUTSTD_LOGIC);

ARCHITECTUREbehvOFTriBuff1IS

PROCESS(OE,Datain)

BEGIN

IFOE='

Dataout<

Z'

=Datain;

ENDPROCESS;

3.1

?

3-12带锁存器,描述?

EDA是以CPLD和FPGA芯片为基础,利用硬件描述语言和EDA工具软件自动完成具有系统功能的电路设计。

一是模块化,二是元件重用(reuse).

一、定义

SignalA:

std_logic;

VariableA:

std_logic_vector(7downto0);

constantwidth:

integer:

=8--在定义时赋值

3-6图3-18是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

ENTITYmux_dIS

PORT(CL,CLK0:

OUT1:

ARCHITECTUREbehaveOFmux_dIS

SIGNALx,y:

x<

=NOT(CLXORy);

OUT1<

=NOTy;

PROCESS(CLK0)BEGIN

IFCLK0'

EVENTANDCLK0='

THEN

=x;

ENDbehave;

个进制数数的表达

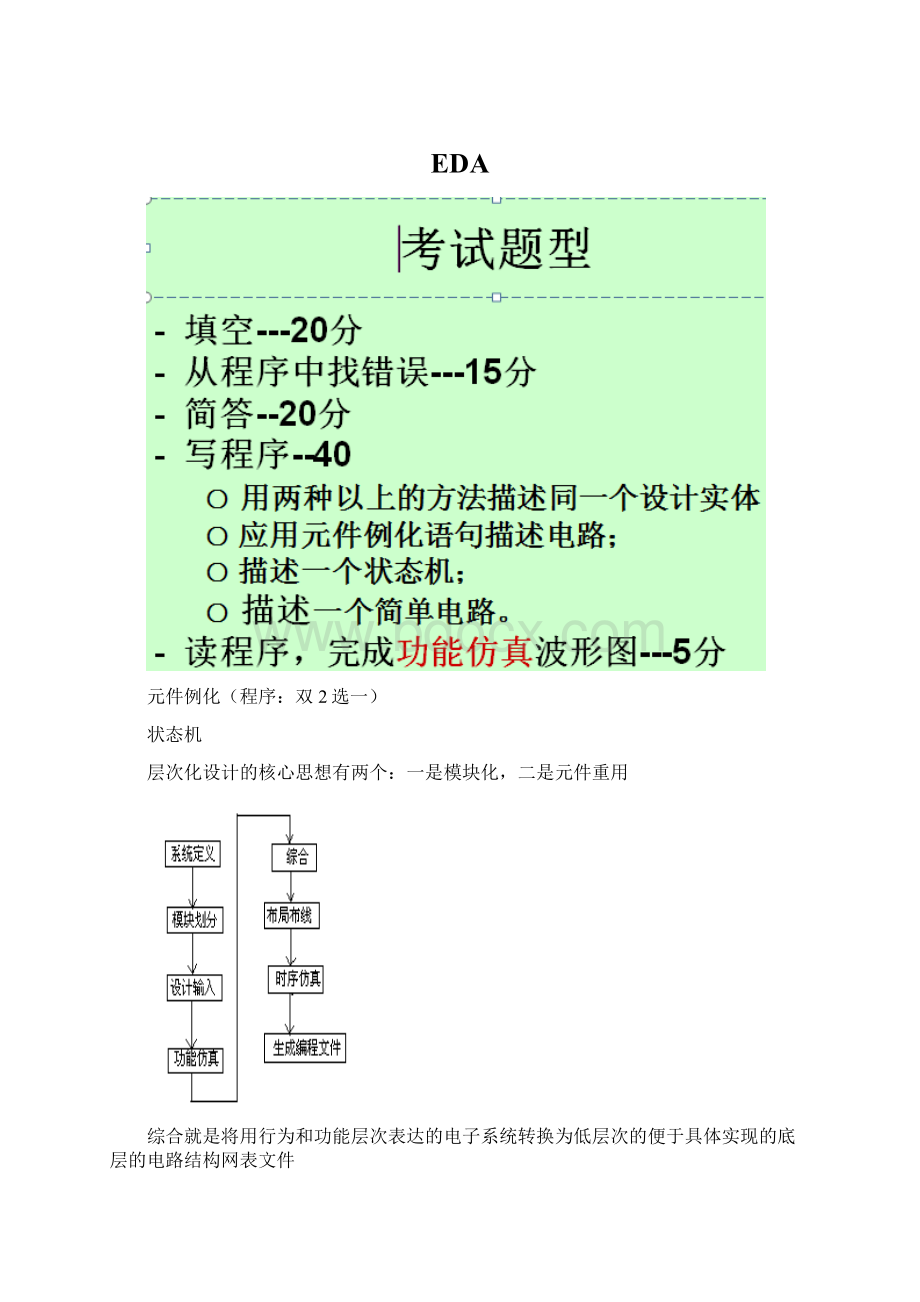

下列是EDA技术应用时涉及的步骤:

A.原理图/HDL文本输入;

B.适配;

C.时序仿真;

D.编程下载;

E.硬件测试;

F.综合

请选择合适的项构成基于EDA软件的FPGA/CPLD设计流程:

A→___F___→___B__→____C___→D→___E____

2.基于EDA软件的FPGA/CPLD设计流程为:

原理图/HDL文本输入→__功能仿真_→综合→适配→__时序仿真

___→编程下载→硬件测试

10.状态机编码方式中,其中__A__占用触发器较多,但其简单的编码方式可减少状态译码组合逻辑资源,且易于控制非法状态。

P221

A.一位热码编码

1、带计数使能的异步复位计数器(即:

不需要等到下一个脉冲即更新)

输入端口:

clk时钟信号

rst异步复位信号

en计数使能

load同步装载

data(装载)数据输入,位宽为10

输出端口:

q计数输出,位宽为10

ENTITYCNT1024IS

PORT(CLK,RST,EN,LOAD:

INSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR(9DOWNTO0);

Q:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCNT1024;

ARCHITECTUREONEOFCNT1024IS

PROCESS(CLK,RST,EN,LOAD,DATA)

VARIABLEQ1:

STD_LOGIC_VECTOR(9DOWNTO0);

IFRST='

Q1:

=(OTHERS=>

'

复位

ELSIFCLK='

ANDCLK'

EVENTTHEN

IFLOAD='

Q1:

置数

ELSE

IFEN='

Q1:

=Q1+1;

计数

ENDIF;

ENDIF;

Q<

=Q1;

ENDONE;

看下面原理图,写出相应VHDL描述

ENTITYTRI_STATEIS

PORT(E,A:

Y:

INOUTSTD_LOGIC;

B:

ENDTRI_STATE;

ARCHITECTUREBEHAVOFTRI_STATEIS

PROCESS(E,A,Y)

IFE='

B<

=Y;

Y<

='

ELSE

=A;

ENDBEHAV;

信号与变量的区别:

信号赋值语句在进程外作为并行语句,并发执行,与语句所处的位置无关。

变量赋值语句在进程内或子程序内作为顺序语句,按顺序执行,与语句所处的位置有关。

信号赋值符号为<

=,变量赋值符号位:

=。

信号赋值符号用于信号赋值动作,不立即生效,变量赋值符号用于变量赋值动作,立即生效。

6、WHEN_ELSE条件信号赋值语句和IF_ELSE顺序语句的异同:

*WHEN_ELSE条件信号赋值语句中无标点,只有最后有分号;

必须成对出现;

是并行语句,必须放在结构体中。

*IF_ELSE顺序语句中有分号;

是顺序语句,必须放在进程中

10、构成一个完整的VHDL语言程序的五个基本结构:

实体(ENTITY)、结构体(ARCHITECURE)、配置(CONFIGURATION)、库(LIBRARY)、程序包(PACKAGE)。

14、VHDL的子程序有

过程(PROCEDURE)

和

函数(FUNCTION)

两种类型,具有可重载性特点。

13.VHDL语言中信号(变量)定义的位置是结构体中特定位置,变量也可在进程中定义

17.关于VHDL数据类型,正确的是运算与数据类型无关

27.VHDL运算符优先级NOT的优先级最高,逻辑运算的优先级最低

4-7含有异步清零和计数使能的16位二进制加减可控计数器。

ENTITYCNT16IS

PORT(CLK,RST,EN:

CHOOSE:

INBIT;

SETDATA:

BUFFERINTEGERRANCE65535DOWNTO0;

COUT:

BUFFERINTEGERRANCE65535DOWNTO0);

ENDCNT16;

ARCHITECTUREONEOFCNT16IS

PROCESS(CLK,RST,SDATA)

VARIABLEQI:

STD_LOGIC_VECTOR(65535DOWNTO0);

IFRST='

THEN--计数器异步复位QI:

ELSIFSET=’1’THEN--计数器一步置位

QI:

=SETDATA;

ELSIFCLK'

THEN--检测时钟上升沿

IFEN=’1’THEN–检测是否允许计数

IFCHOOSE=’1’THEN--选择加法计数

QI:

=QI+1;

--计数器加一

ELSEQI=QI-1;

ENDIF;

COUT<

=QI;

--将计数值向端口输出

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx